FPGA 4选1时钟选择:易灵思Ti60F225详解

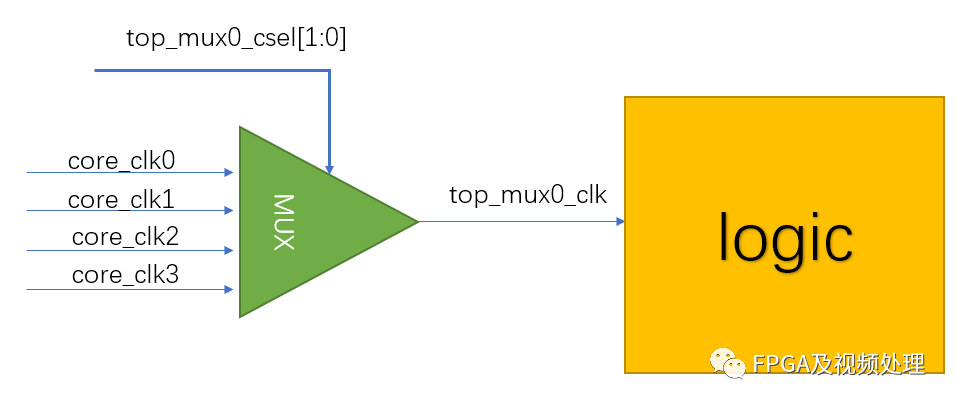

在trion要实现一个4选1时钟复用或许比较麻烦。但是在钛鑫上已经给出了解决方案。这里以Ti60F225为例来介绍如何实现下面的4选择1时钟选择功能。 在FPGA

关于「易灵思」的技术文章、设计资料与工程师讨论,持续更新。

在trion要实现一个4选1时钟复用或许比较麻烦。但是在钛鑫上已经给出了解决方案。这里以Ti60F225为例来介绍如何实现下面的4选择1时钟选择功能。 在FPGA

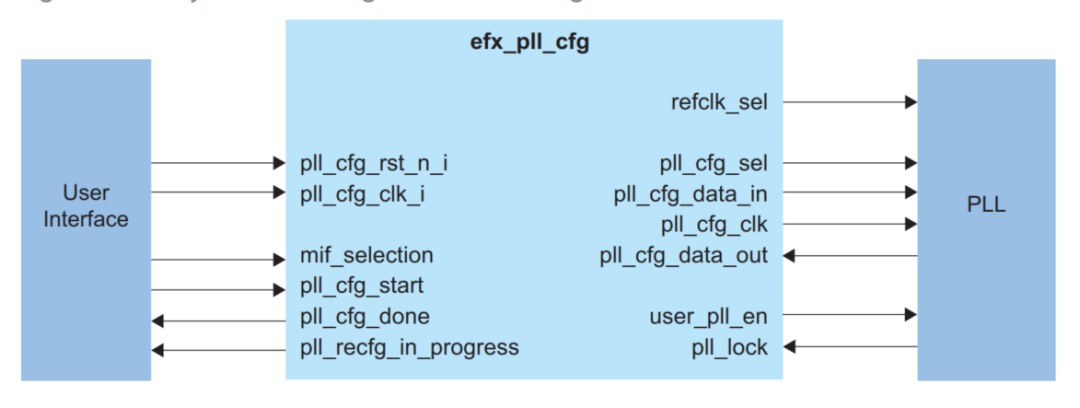

TJ375已经支持PLL的动态配置。打开PLL在Advance Settings中的Dynamic Reconfiguration中勾选Enable就可以了。最大可以支持8

近日,由国产FPGA领军企业易灵思与南京大学集成电路学院联合举办的“深度学习与硬件加速”暑期课程圆满结课。本次课程为期5天(7月7日至7月11日),面向大三本科生,旨在通过

金秋九月,芯聚蓉城。9月16日下午,易灵思(Elitestek)在成都希顿酒店成功举办了以“蓉芯聚力·易启未来”为主题的技术研讨会。本次盛会吸引了成都及周边地区众多行业工程

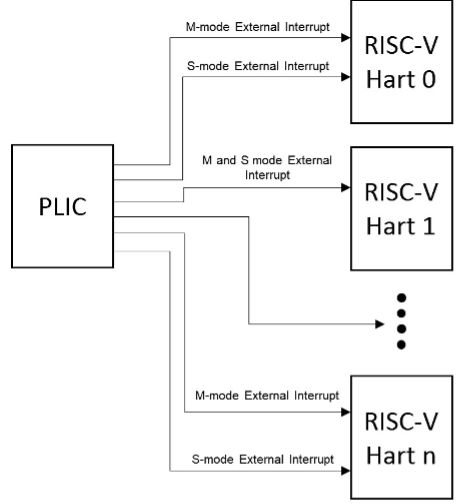

随着 RISC -V处理器在 FPGA 领域的广泛应用,易灵思 FPGA 的 Sapphire RISC-V 内核凭借软硬核的灵活支持,为开发者提供多样选择。本文深入探讨

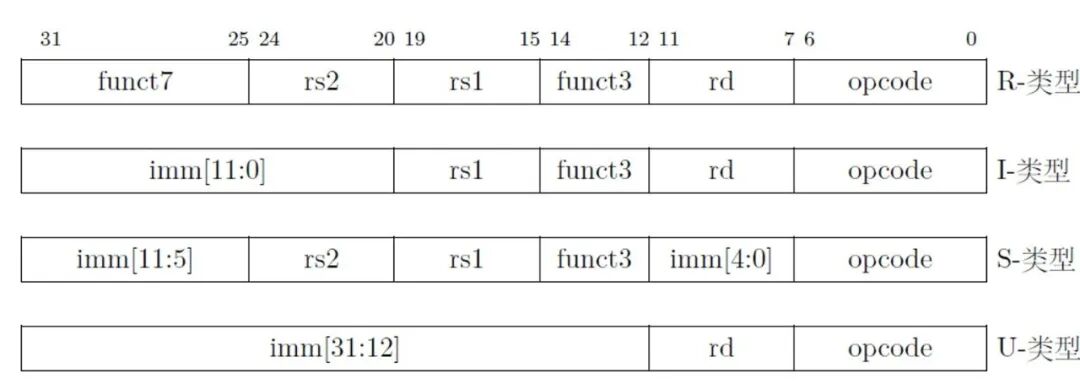

RISC-V(Reduced Instruction Set Computing-V)是一个开源指令集架构(ISA),它的设计目标是提供一个简洁、可扩展且高效的指令集,适用

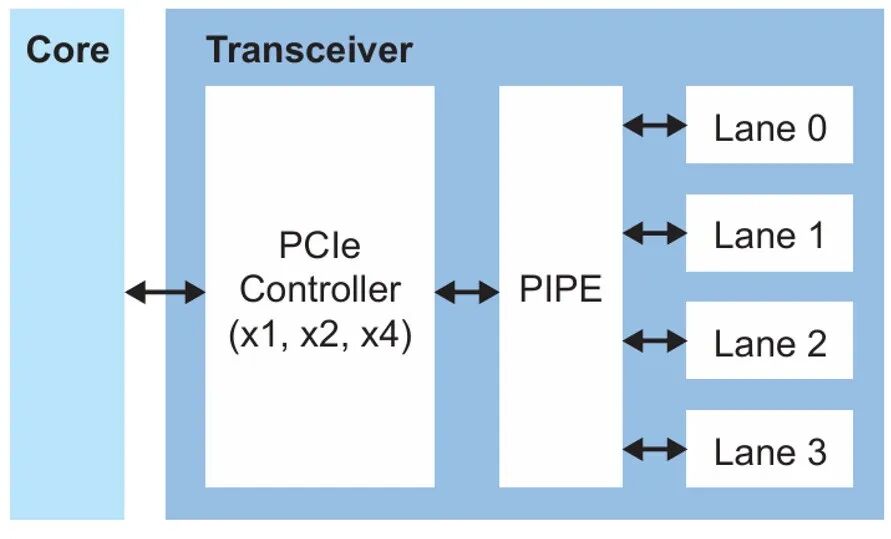

在数字经济飞速发展的今天,数据传输速率已成为硬件性能突破的核心瓶颈。作为国内首款适配中端FPGA的PCIe Gen4高速接口方案,钛金高速接口的闪亮登场,凭借高速低功耗特性

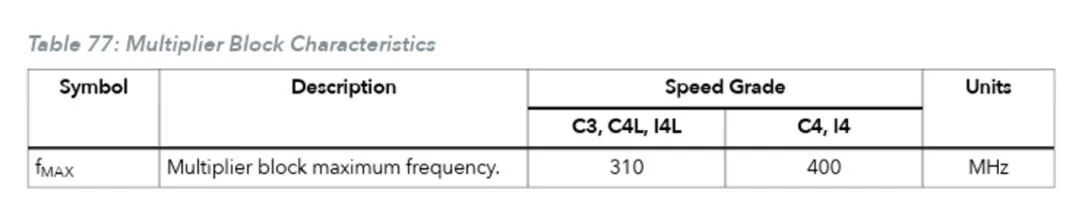

在现代数字信号处理(DSP)应用中,FPGA(现场可编程门阵列)凭借其高度并行性、可定制性和灵活性,已成为加速信号处理任务的核心硬件平台之一。 作为在该领域具备领先技术

2025年11月30日,第八届全国大学生嵌入式芯片与系统设计竞赛——FPGA创新设计赛道全国总决赛在南京圆满落下帷幕。在这场代表国内FPGA领域最高水平的大学生赛事中,易灵

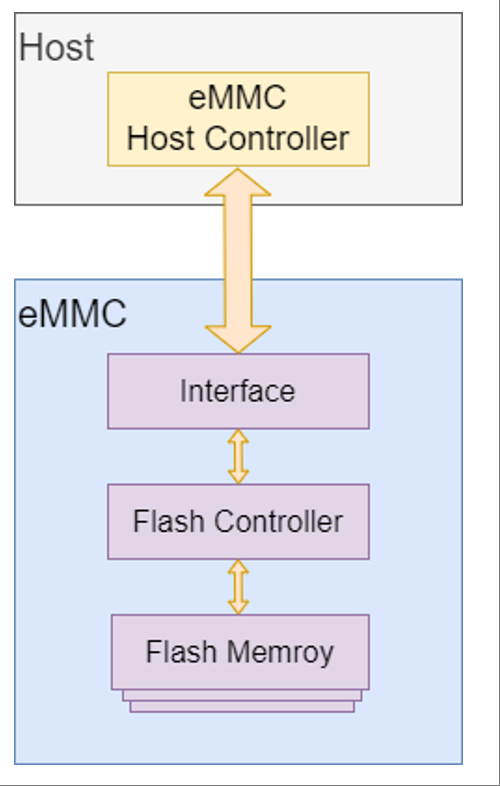

eMMC全称为 embedded Multi Media Card,主要用于非易失性存储,它弥补了 FPGA 芯片自身存储能力的不足,为 FPGA 提供一个高集成度、大容量