史前工艺做电路板!泥土和柴火纯手搓PCB:全套教程已开源

[ ](https://mp.weixin.qq.com/s?__biz=MzA5MDk2NTEwNQ==&mid=2656510277&idx=1&sn=8b196489488c2621d143b38b6eaa1b09&scene=21#wechat_redirect) 近日,Feminist Hacking在博客上发布了一项开源项目,用天然黏土制作可工作的PC

纳米网技术应用频道 — 提供技术应用领域最新资讯、技术文章和行业动态。

[ ](https://mp.weixin.qq.com/s?__biz=MzA5MDk2NTEwNQ==&mid=2656510277&idx=1&sn=8b196489488c2621d143b38b6eaa1b09&scene=21#wechat_redirect) 近日,Feminist Hacking在博客上发布了一项开源项目,用天然黏土制作可工作的PC

如今,电子产品公司正面临日益增大的压力,需要在从原材料采购到报废处理的整个产品生命周期中,减少对环境的影响。客户期待高能效的解决方案,监管机构要求企业承担责任,投资者也愈发关注可衡量的环境、社会和治理(ESG)进展。 因此,设计工程师的日常决策不仅关乎性能规格和物料清单(BOM)成本,还影响着公司的环境足迹、开发效率,以及长期竞争力。你选择的每一个元器件、评估的每一种拓扑结构,和做出的每一个设计权

PolarFire® FPGA助力4K / 8K机器视觉快速落地 如果您正在做高速成像或机器视觉系统开发,那么好消息来了——只用一套PolarFire FPGA生态,就能同时搞定SDI、SLVS-EC 和 CoaXPress™接口! PolarFire FPGA 通过统一的平台,大幅简化设计流程,让复杂的视频接口开发变得更高效、更可控。 三种方式,全面加速您的下一代设计 SDI Rx/Tx I

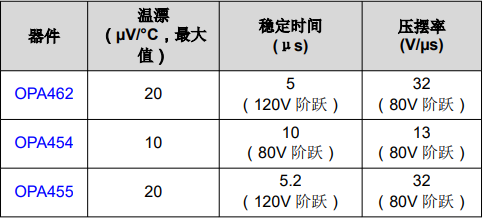

简介 随着半导体产业的不断发展,半导体测试设备发挥着重要作用。由于半导体和集成电路的不断发展以及对电子产品的越发严刻的要求,测试设备必须不断改进。德州仪器 (TI) 提供了各种各样的精密放大器,它们能为测试集成电路提供了更准确的结果。 电压强励(也称为被测器件 (DUT) 或负载激励)是一个重要方面。在半导体器件上施加某些电压条件并观察半导体的反应对于确保器件正确响应很重要。为提供理想的最终结果,

关键要点 AI工作负载需求急剧攀升,单机柜功耗从120kW跃升至600kW-1MW,向800V架构转型势在必行,以此突破传统48V系统的物理极限。 得益于成熟的生态系统、可靠的工程验证、可控的安全特性以及对现有基础设施的兼容性,48V架构依旧具备高度适用性。 热插拔控制器正转型升级为供电入口节点与首道防线,可提供实时遥测数据、支持预测性维护、优化容量规划,同时提升能耗预测精度并实现主动

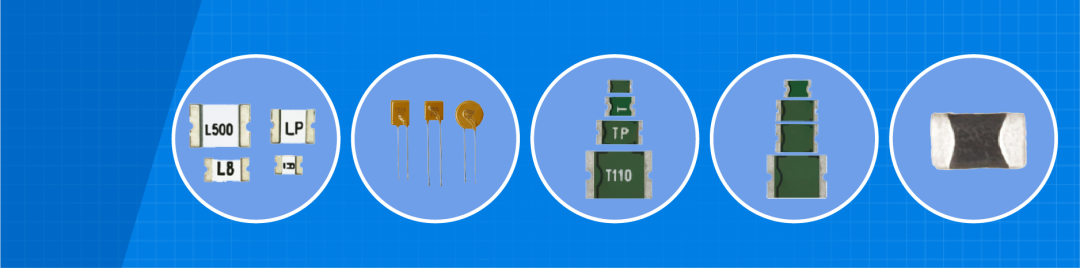

您是否遇到过电子设备突然停止工作,随后又恢复正常运行?这很可能是自恢复保险丝在发挥作用。本文将从定义、原理、优势和典型应用,系统梳理自恢复保险丝的基本知识,为您的电子设备设计与元器件选型提供参考。 Q**1** 什么是自恢复保险丝 自恢复保险丝(PPTC,Polymer Positive Temperature Coefficient),全称是聚合物正温度系数器件,是一种基于高分子材料与导电

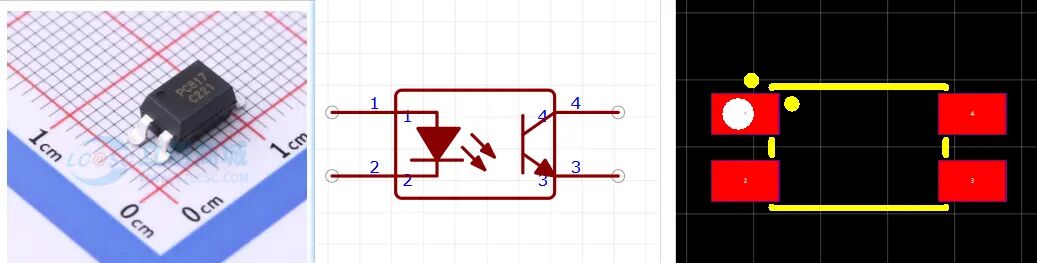

前言 光耦隔离,对嵌入式工程师来说,再熟悉不过了。 但遇到具体问题时,很多教程只告诉你"接个光耦就行",却不讲为什么选这个型号、电阻怎么算、CTR是什么。 今天这篇,不讲虚的,从原理到选型到电阻计算,手把手带你搭一个能直接用的光耦隔离电路。 一、光耦介绍 光耦(Optocoupler),也称光电耦合器,是一种利用光信号实现电信号隔离和传输的电子器件。 它主要由发光二极管(LED)和光敏元件(如光

两年前,华为Mate 60系列横空出世,首次实现手机直连卫星通话,直接震惊了整个通信行业。 在此之前,卫星通信终端始终绕不开一个“累赘”——高增益圆极化天线阵列,最典型的就是四臂螺旋天线。哪怕是后来电信推出的卫星手机,也依然带着一根显眼的外置螺旋天线,像拖着条“小辫子”,既不美观,也不方便携带。 可华为Mate 60偏要打破常规:卫星天线被完全隐形,悄无声息地藏进了手机金属中框里。 当时我们反复

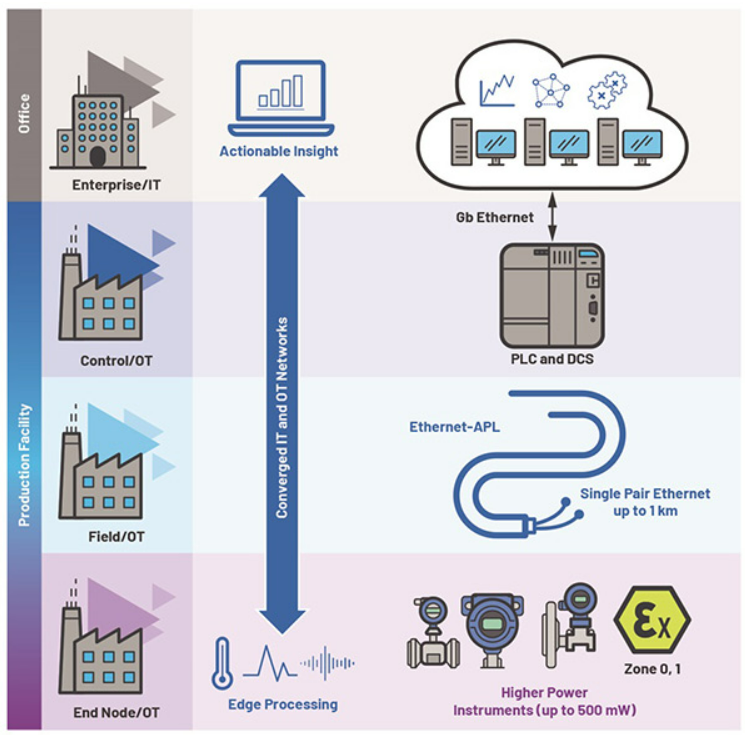

关键要点 ABB与ADI的合作带来了强大的Ethernet-APL(高级物理层)技术,将推动各类加工厂的工业自动化升级。 Ethernet-APL支持通过单根线缆实现高速数据传输与供电,即使在危险区域也能稳定运行。 Ethernet-APL不仅能够简化安装并降低成本,而且能够提升大型工业设施的可靠性。 借助实时诊断功能和无缝设备集成能力,运营人员能够高效开展维护与运营工作。 过

工程名称:60多元手搓摩托车 BSD 盲区监测! 工程作者:zaodianshane 前言 我希望做一个雷达。 在骑行的时候,只要有车/人靠近盲区。 雷达就会亮灯提醒我。 本文主要分享这个雷达的开源方案! 但在分享之前,俺想先说明一下 *其实我并不是专业做嵌入式这块的,我是做建筑工程管理这块工作的。可以说是一个完全零基础的小白。*我都是近1个月利用晚上下班时间看视频学习画板子做电路测试,看人家的

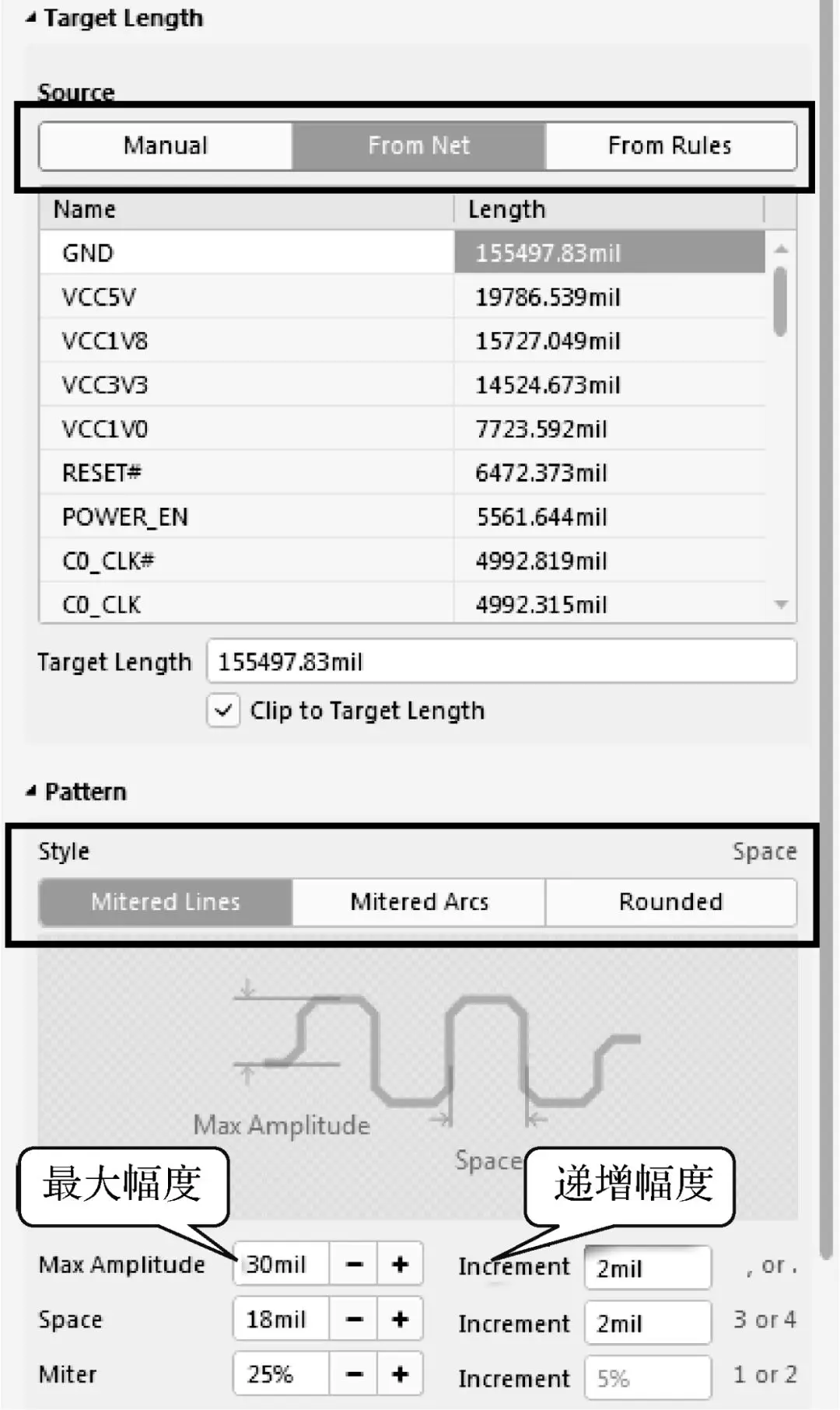

在高速PCB设计中,时序控制与信号完整性变得愈发重要。你是否也曾面对总线时序不匹配的烦恼?有没有想过“蛇形走线”不仅是个美观技巧,更是一门高效提升性能的实战技能? 今天我们就以Altium Designer中的单端与差分蛇形等长走线技巧为例,手把手教你掌握这项必备技能!每一步配图对应,让你看得懂、学得会! 单端蛇形走线,时序控制第一步 在高速并行总线(如DDR SDRAM)设计中,由于多个数据信号

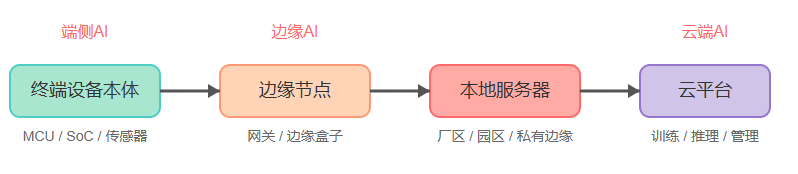

文章简介 这几个词现在被混着用得非常厉害。很多时候,一篇文章里前面写“边缘AI”,后面又说“端侧AI”,再往后又说“AI+嵌入式”,读下来感觉都差不多,但其实它们说的不是同一个维度。 更麻烦的是,很多真实项目同时跨了多个概念。你如果只记定义,不看实际例子,还是很容易分不清。 所以这篇增强版不只讲概念,还会把每个词放进真实工程场景里去解释。你看完之后,至少能知道:一个词到底是在说“行业融合”、还是在

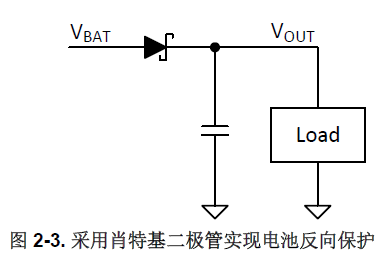

引言:效率与可靠性的工程权衡 在电源系统前端,输入保护电路必须在坚固可靠和高效节能之间取得平衡。传统方案在此面临根本性矛盾: 肖特基二极管:如同一位可靠的“卫士”,能有效阻断反向电流,但其较高的正向压降(如10A时约0.5V)会导致显著的功率损耗(约5W)和散热难题,同时在电池电压较低时严重压缩后级电路的工作裕量。 P沟道MOSFET:如同一扇低阻的“开关”,导通损耗极低,但它缺乏关键的反

工程名称:提醒喝水杯垫V2.0 工程作者:平韵の立创小分部 前言 这,是一个提醒喝水杯垫~ DIY成本仅80! 诶?这时候可能就有人说了 做一个不如买一个! 的确是这样的。 但,如果你了解到了它的这些功能,或许你会有不一样的看法…… *0***1 它有什么功能? ” 它会提醒你喝水:当你放下水杯,杯垫就会开始倒计时,时间到会提醒你喝水 可自定义倒计时时间 屏幕实时显示:时间,天气,

实现净零排放的一个基本要素是减少所有行业的CO2排放量。然而,根据国际能源协会(IEA)的数据,建筑行业实现2050年全球CO2净零排放目标的进展依然不尽人意。具体而言,2030年的目标是与2021年相比每平方米的能耗减少35%。目前,建筑能耗占全球能耗的30%,为此人们担心,除非建筑行业采取具体行动实现系统数字化转型和自动化,否则排放目标将无法实现。为了实现有效的自动化,需要进行更多的实时数据采

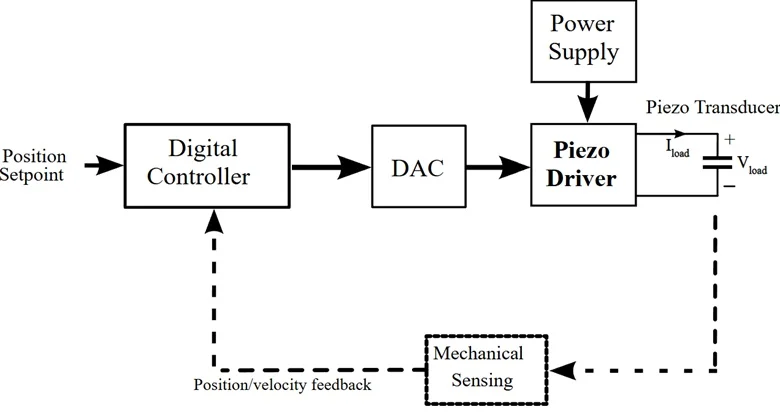

压电作动器广泛应用于各类定位系统中。这类作动器依托逆压电效应工作,这是一种物理换能机制:压电材料在接收电荷作用时会产生机械作用力。 但我们无法将运动控制器直接与压电作动器相连,必须搭配压电放大器。压电放大器也常被称作压电驱动器,是整套压电控制系统的核心关键部件。 市面上有各类大功率压电放大器可供选型。本文为三篇系列文章的第一篇,将对比解析AB 类与D 类输出级架构在压电放大器应用中的优缺点。正如后

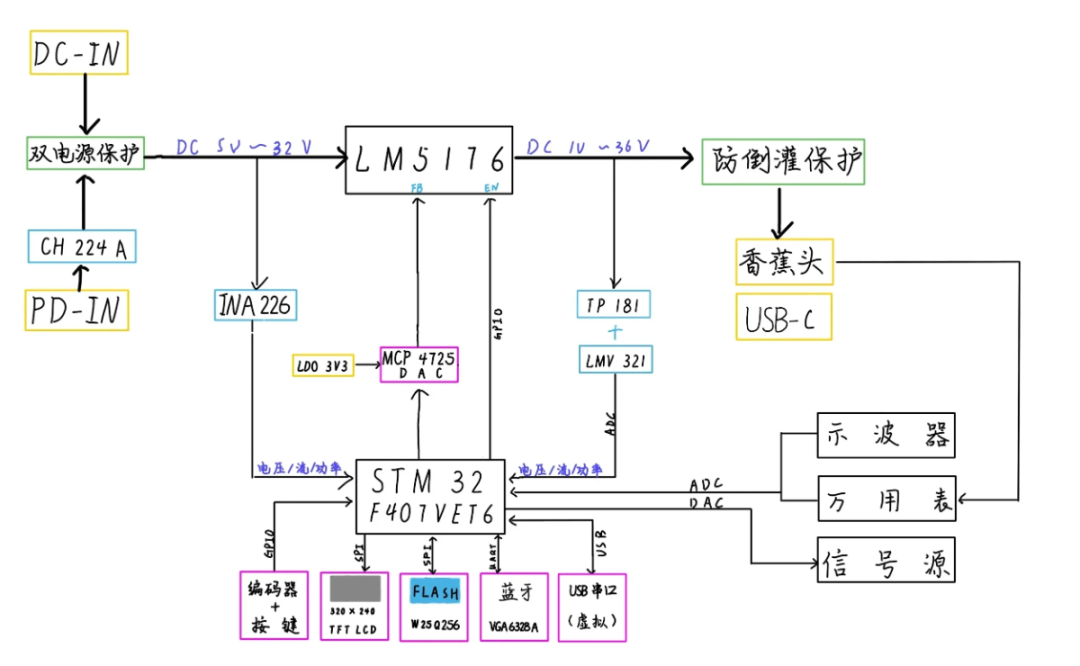

工程名称:XM_POWER_KIT 数控电源+示波器+万用表+信号源四合一 工程作者:雪萌_Xuemeng 前言 这个小小的工具箱,有4大功能! 它集成了: 数控电源 250W输出 示波器 500Khz带宽 波形发生器 最大50Khz任意波输出 万用表 3%精度 每一个单拎出来都很实用啊啊!! 而这一切,就基于一块87×60mm的6层PCB实现****?! 他怎么做到的?!咱瞅瞅他的设计方案!在那

在现代电子设备中,温度检测是保障系统安全、提升性能与可靠性的关键技术。无论是防止手机电池过热,还是确保工业电机在适宜温度下运行,都离不开温度传感器的“感知”。在众多传感器中,**热敏电阻**因其结构简单、成本低廉、响应迅速而备受青睐。本文将深入浅出地剖析热敏电阻的工作原理、常用电路、关键参数及选型要点。 一、 热敏电阻:温度变化的“电阻翻译官” 核心原理:热敏电阻的本质是一种对温度高度敏感的电

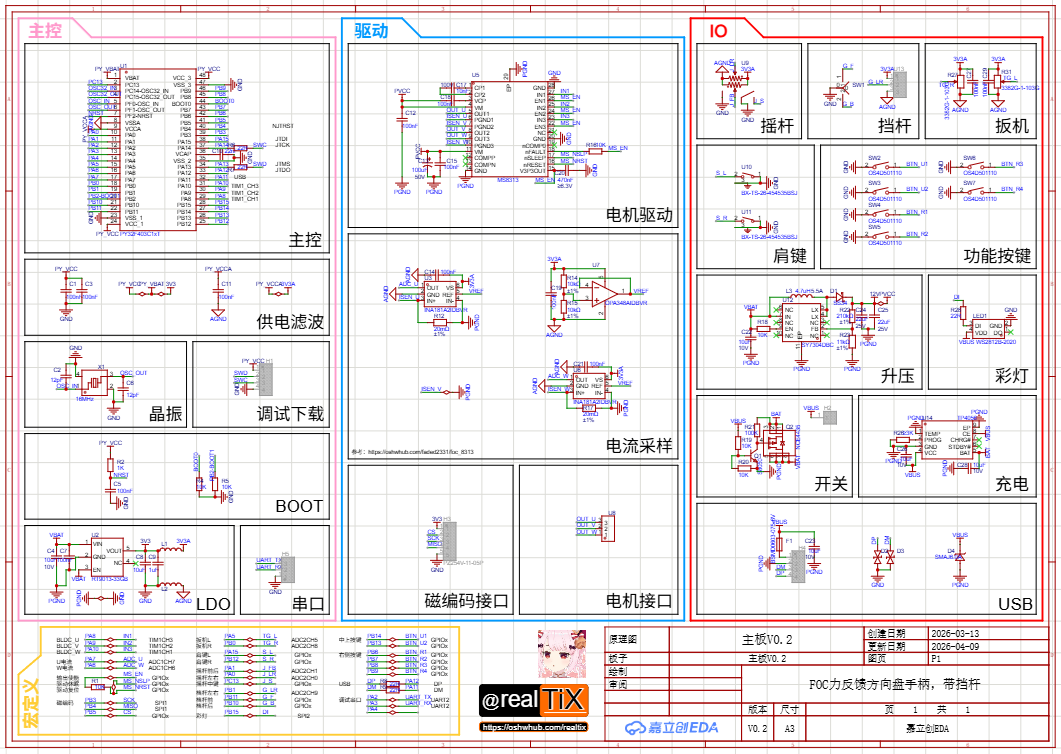

工程名称:FOC力反馈方向盘手柄,带挡杆 工程作者:realTiX 前言 小编今天逛开源平台,看到了一个很有趣的力反馈方向盘。 控制赛车非常丝滑**▼** 这这这,这是主打一个,在家也能实现“赛车”自由? 但这不是最重要的!最重要的是: 作者只用 1颗主控+1个10X7cm的主板PCB 就实现了 FOC+力反馈+USB HID全流程! 这是什么水平? 这是非常的有水平! 事情变得有趣起来了…… 这

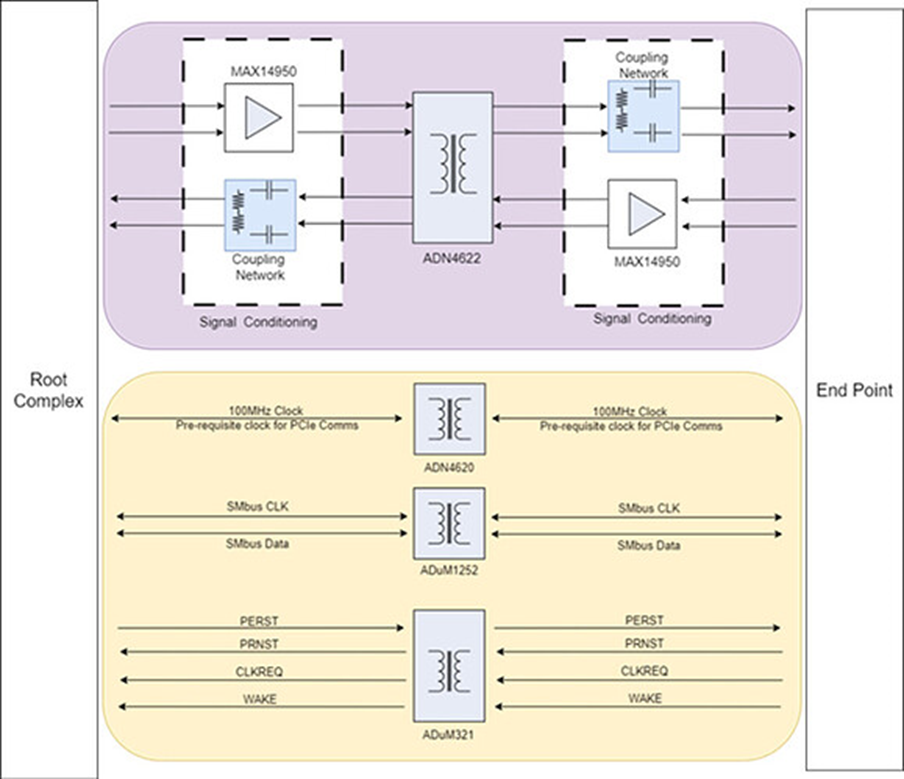

文章**概述** 工业与高可靠性领域,实现 PCI Express(PCIe)接口的电气隔离对于系统的抗噪声、可靠性、接地分离以及安全要求至关重要。ADI(Analog Devices)提供基于 Giga‑Speed 隔离技术的完整方案,可满足 PCIe Gen 1 高速链路的隔离需求,并确保信号完整性(SI)与协议兼容性。 ADN4622BRNZ:PCIe Gen 1 LVDS 链路隔离核心器件