ESD防护详解:静电放电原理与测试标准

本文介绍了静电放电(ESD)的本质、危害以及如何通过测试验证防护效果。详细讲解了ESD的产生机理和行业通用的测试体系,包括HBM、MM、CDM等模型,并分享了上海雷卯电子在ESD防护领域的实践经验。

关于「雷卯电子」的技术文章、设计资料与工程师讨论,持续更新。

本文介绍了静电放电(ESD)的本质、危害以及如何通过测试验证防护效果。详细讲解了ESD的产生机理和行业通用的测试体系,包括HBM、MM、CDM等模型,并分享了上海雷卯电子在ESD防护领域的实践经验。

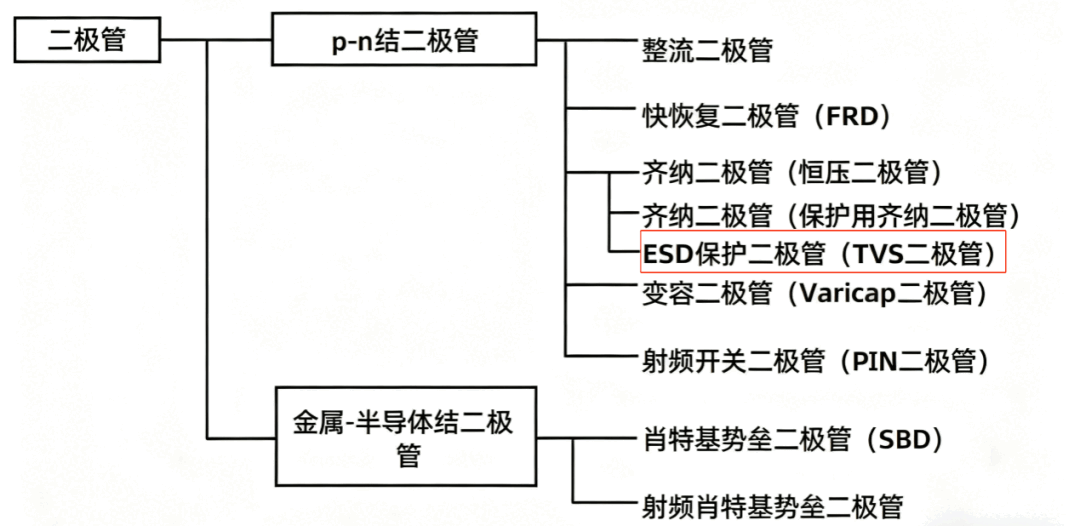

本文详细解析了ESD保护二极管的结构和工作原理,介绍了其在正常工作和ESD冲击时的不同表现,并重点突出了上海雷卯电子在该领域的技术优势。

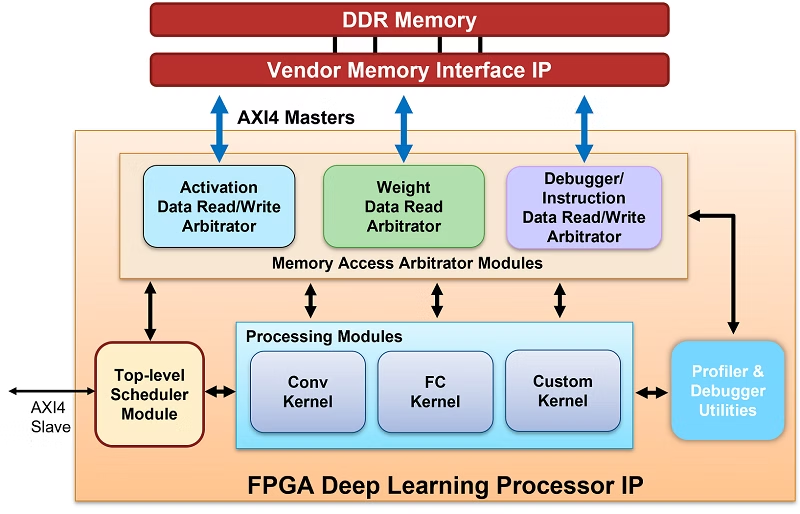

如果你已经在用 MATLAB 做深度学习,那一定知道它的训练和仿真体验非常丝滑。但当模型要真正落地到 FPGA 上时,往往就会卡住:怎么把网络结构和权重优雅地搬到硬件里?

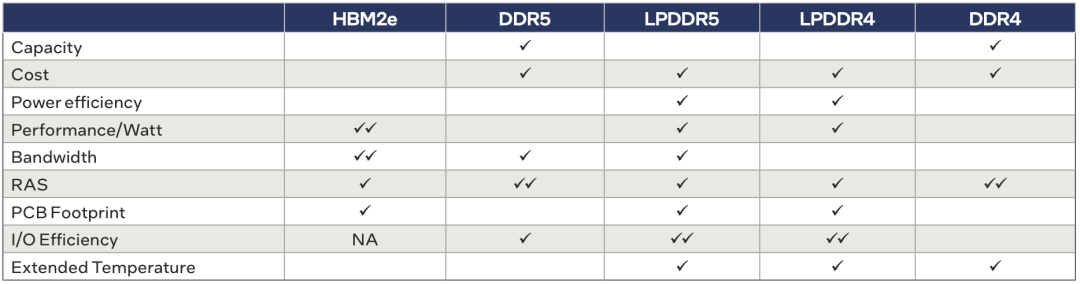

在技术飞速发展的今天,内存性能、占用面积和能效已成为现代应用的关键考量因素。 Agilex 5 FPGA 内存技术提供灵活的内存接口,可有效应对上述关键需求。 Ag