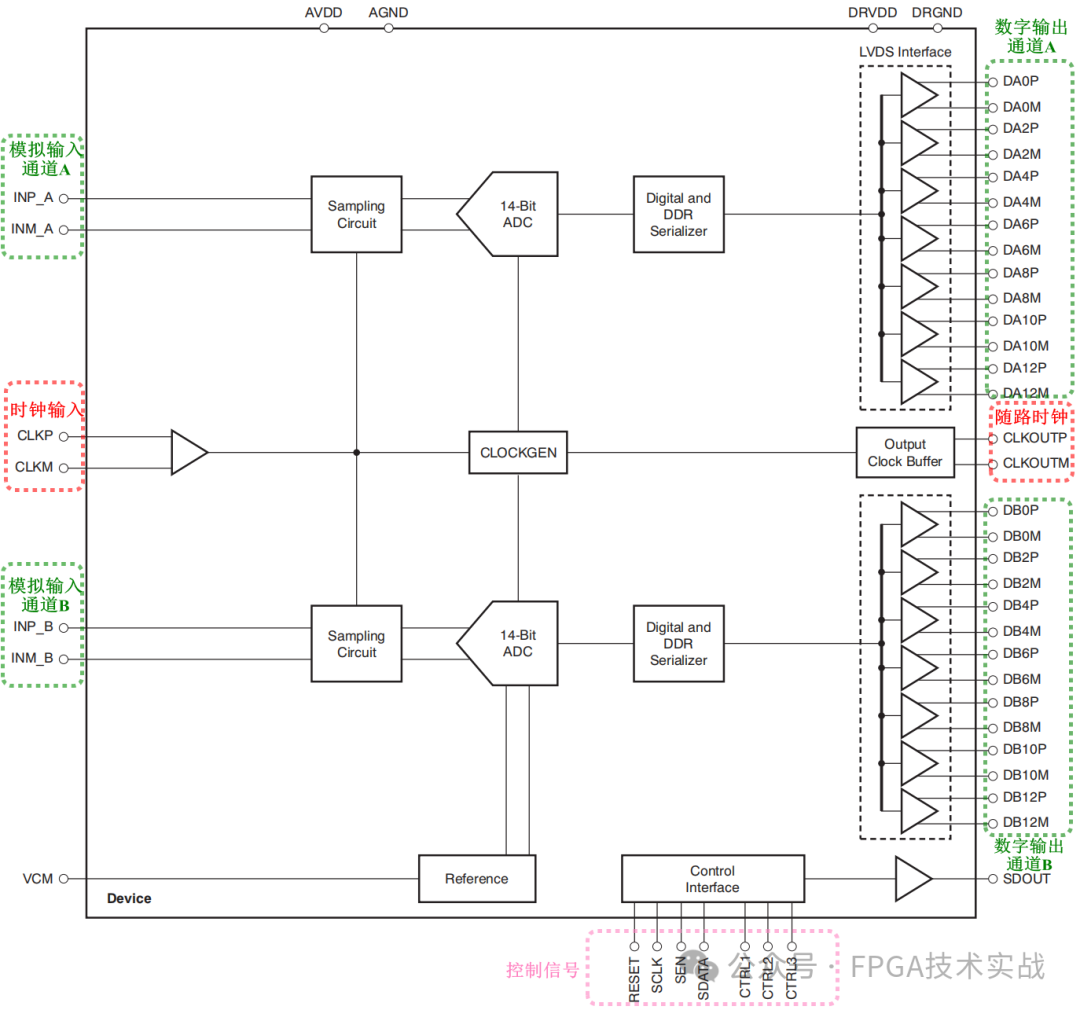

Altera FPGA与ADS4249及DAC3482的DDR LVDS接口设计详解

引言:本文以TI的ADS4249(ADC)和DAC3482(DAC)之间的接口为例,介绍Altera FPGA与ADC/DAC之间的DDR LVDS接口设计以及时序约束详细

关于「Altera (阿尔特拉)」的技术文章、设计资料与工程师讨论,持续更新。

引言:本文以TI的ADS4249(ADC)和DAC3482(DAC)之间的接口为例,介绍Altera FPGA与ADC/DAC之间的DDR LVDS接口设计以及时序约束详细

AI 正在向边缘迁移 从聊天机器人、内容生成到高级数据分析,AI 已无处不在。过去,大多数 AI 处理都在云端完成。然而,随着模型功能日益强大以及对实时洞察的需求持续增

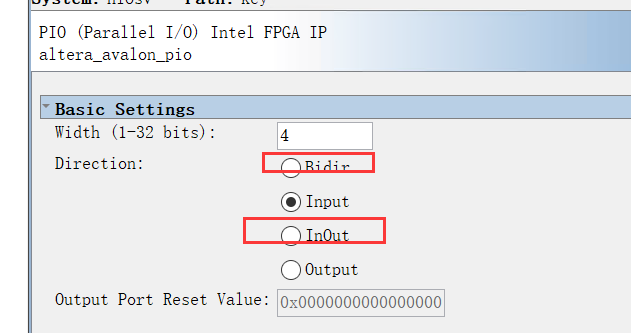

PIO IP是FPGA 设计中比较简单常用的IP, 当设置PIO IP的Direction的时候,可以看到有如下4个选项: Input代表这组IO是输入引脚,O

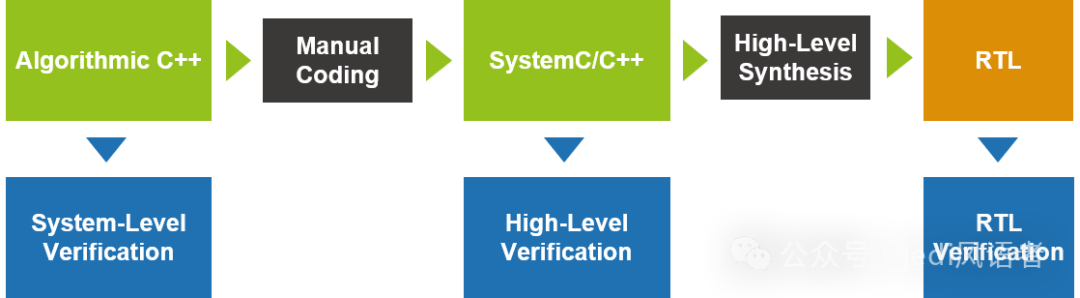

上篇和中篇,我们介绍了FPGA的四大特点,以及这些特点所带来的市场和应用机会,概述如下:硬件可编程:通信网络,芯片验证等;并行和实时:视频图像处理,AI推理等;高集成度:工业机

今天,全球 FPGA 创新技术领导者 Altera 宣布,全球技术投资巨头银湖资本(Silver Lake)已完成对 Altera 51% 股权的收购,该股权原由英特尔公司

Quartus Prime 专业版 25.3 现已正式发布, FPGA AI 套件 25.3 版本同步亮相。新版软件实现了 FPGA 设计效率的重大飞跃,带来了更智能的工具

Agilex 5 D 系列 FPGA 和 SoC 家族全面升级,为中端 FPGA 应用能力带来巨大飞跃——逻辑单元、内存、DSP/AI算力提升高达 2.5 倍,外存带宽提升

近日,全球 FPGA 创新技术领导者 Altera 的Agilex 5 FPGA 与 SoC 产品系列,荣获2025 年 AspenCore 全球电子成就奖(WEAA)的处

2025 年初,全球 FPGA 创新领导者 Altera 正式启动了“Altera 解决方案合作伙伴加速计划”,旨在强大的生态系统支持下,助力企业打破壁垒,提速创新引擎,加