数字隔离器输出并联电平异常原因及解决方案详解

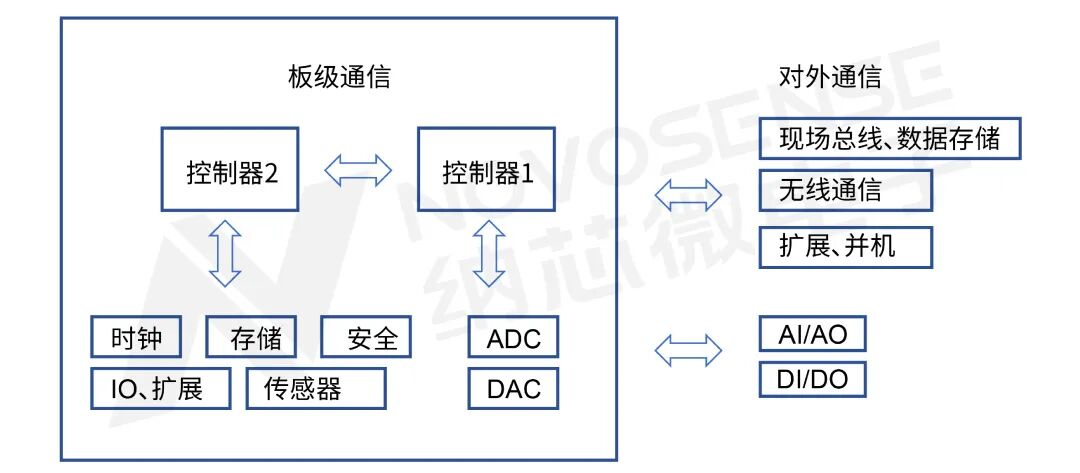

文章来源:纳芯微电子 在工业系统 SPI 一主多从通信架构中,为节省 IO 资源,数字隔离器输出通道并联复用是常见设计,但实际应用中极易出现电平无法正常拉高 / 拉低的

关于「SPI通信」的技术文章、设计资料与工程师讨论,持续更新。

文章来源:纳芯微电子 在工业系统 SPI 一主多从通信架构中,为节省 IO 资源,数字隔离器输出通道并联复用是常见设计,但实际应用中极易出现电平无法正常拉高 / 拉低的

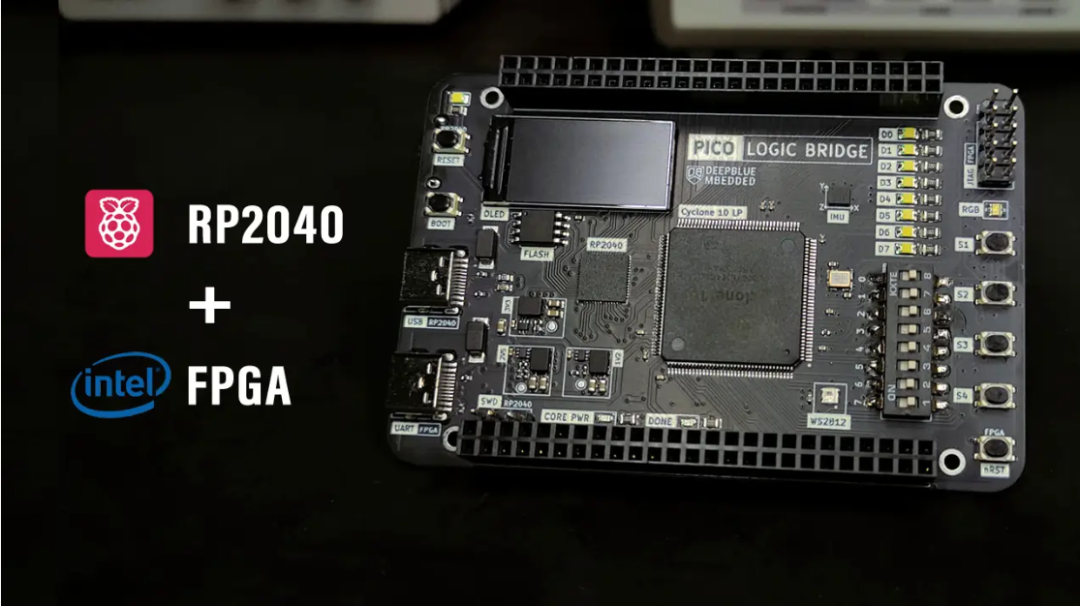

“在本文中,我将向大家展示一个结合了树莓派Pico (RP2040) 与 Cyclone 10 FPGA 的PCB设计项目。我将解释项目中的一些设计决策

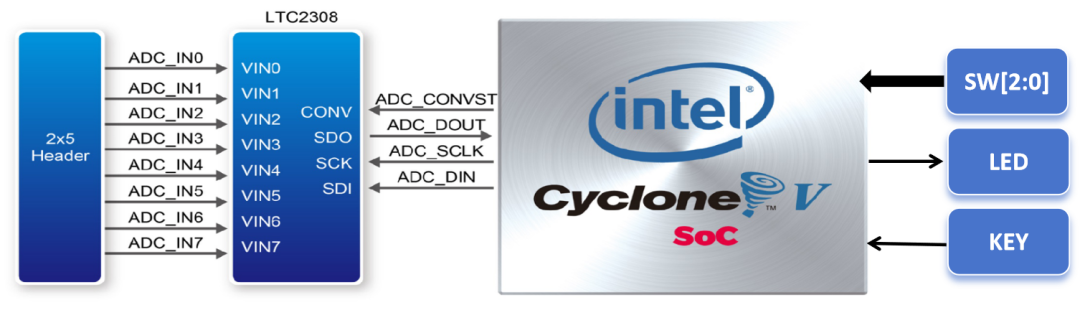

1本教程重点 介绍模数转换原理。 介绍SPI通信协议。 介绍LTC2308工作原理。 学习Verilog代码设计。 学习ModelSim仿真。 学习