FPGA在边缘AI中的应用:低时延与低功耗解决方案

AI 正在向边缘迁移 从聊天机器人、内容生成到高级数据分析,AI 已无处不在。过去,大多数 AI 处理都在云端完成。然而,随着模型功能日益强大以及对实时洞察的需求持续增

关于「产品发布」的技术文章、设计资料与工程师讨论,持续更新。

AI 正在向边缘迁移 从聊天机器人、内容生成到高级数据分析,AI 已无处不在。过去,大多数 AI 处理都在云端完成。然而,随着模型功能日益强大以及对实时洞察的需求持续增

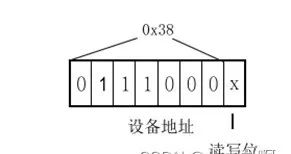

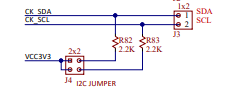

概念 传感器输出经过标定的数字信号输出,通过标准的I2C接口传输数据; 相对湿度的分辨率在0.024%RH,工作范围为0~100%RH; 温度值的分辨率在0.0

近日,被誉为 “全球移动通信行业发展风向标” 的 2025世界移动通信大会(MWC上海)在上海新国际博览中心圆满落幕。本届大会以 “开启智能互联新纪元” 为主题,吸引全球创

01Veloce proFPGA Veloce proFPGA 平台提供三类主板:Uno、Duo 和 Quad。这些主板支持轻松插入和混用不同类型的现场可编程门阵列 (

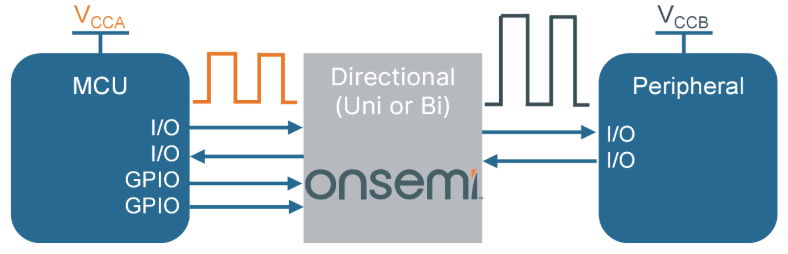

电子系统设计师在为当今的汽车、工业和消费应用设计产品时面临着一系列挑战。他们必须确保产品在不同设备上的精确度、紧凑集成和能源效率,同时满足不断增长的性能期望。与此同时,对于

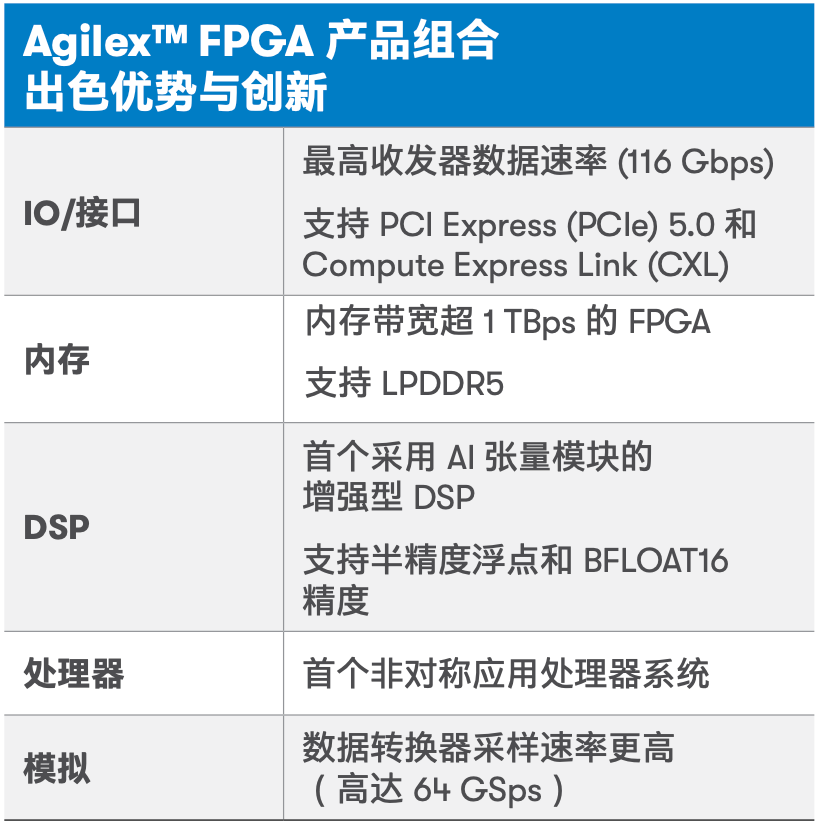

数据爆炸式增长正推动新产品需求激增,这些新产品需具备数据传输、处理和存储能力,并方便开发人员从中获得可执行的深度分析,助力他们基于硬件灵活性来应对市场需求的动态变化、集成多

近日,“2025智多晶FPGA技术研讨会”在武汉成功举办。本次交流会以“智绘新篇 晶质领航”为主题,智多晶专业技术团队在会上揭晓了公司匠心打造的多款FPGA芯片新产品、多项

在国产 FPGA 加速突破、迈向高性能、高可靠的新阶段,智多晶隆重推出新一代 SA5T-200 系列 FPGA 器件。该系列面向高算力、高清视频、高速通信等关键应用场景,集

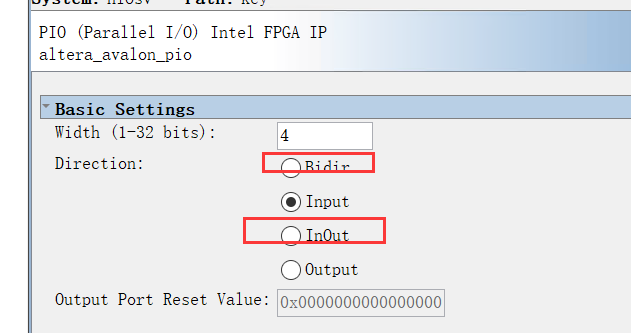

PIO IP是FPGA 设计中比较简单常用的IP, 当设置PIO IP的Direction的时候,可以看到有如下4个选项: Input代表这组IO是输入引脚,O

本文作者:AMD 工程师 Sandy Macnamara 本文讲述了AMD UltraScale /UltraScale+ FPGA 原生模式下,异步模式与同步模式的对

如何为您的应用选择更理想的 DRAM? 对于嵌入式系统工程师而言,选择合适的 DRAM 至关重要,需综合考虑带宽、时延与功耗限制。在近期发布的白皮书中,我们详细比较了主

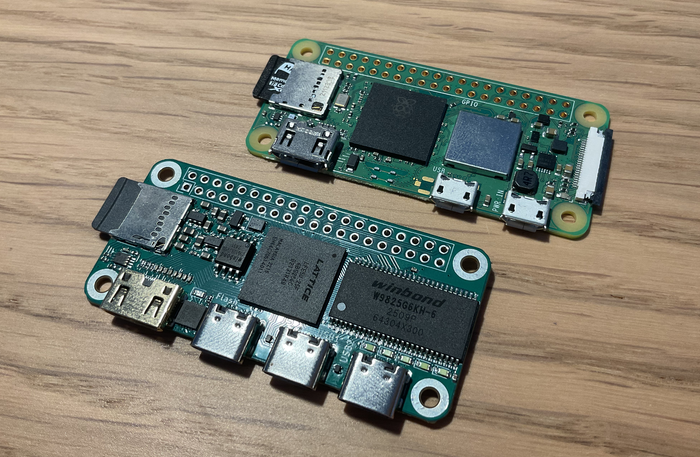

“Icepi Zero 是一款 Raspberry Pi Zero 尺寸的便携式 FPGA 开发板,基于 Lattice ECP5。”

来源:OpenFPGA;;作者:碎碎思 在本文中,我们将介绍如何构建带有VGA输出的低分辨率热成像。该解决方案基于Melexis MLX90640红外阵列、FPGA S

在边缘智能日益复杂的应用场景中,系统协同能力已成为性能的新衡量维度。 ALINX 近期发布的 BZ10 异构多处理采集计算开发板在这方面的表现十分亮眼。 (

近日,由国产FPGA领军企业易灵思与南京大学集成电路学院联合举办的“深度学习与硬件加速”暑期课程圆满结课。本次课程为期5天(7月7日至7月11日),面向大三本科生,旨在通过

简介:本文介绍如何利用FPGA和DMA技术处理来自AD9280和AD9708 ADC的数据。首先,探讨了这两种ADC的特点及其与FPGA的接口兼容性。接着,详细说明了使用X

近日,上海松江举办的“2025中国科创领袖大会暨科创板开市六周年峰会”上,“科创板开市六周年评选”榜单揭晓,安路科技凭借在FPGA领域的持续突破与创新成果,荣膺“2025最

Altera Agilex™ 3 FPGA和SoC FPGAAltera/Intel Agilex™ 3 FPGA和SoC FPGA使创新者能够将成本优化的设计提升到更高的性能

当下,半导体行业的安全需求正经历深刻演变,后量子密码学(PQC)与《网络弹性法案》(CRA)成为绕不开的重要议题。跟随本文一起,深入剖析这两大趋势带来的挑战,并详解Alte

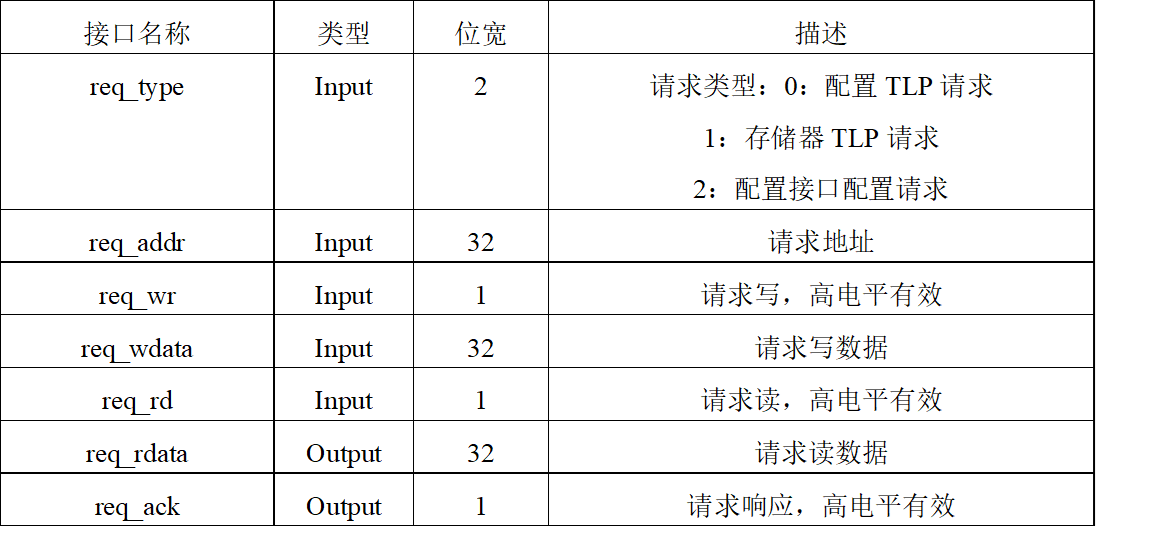

请求模块的具体任务是将系统的请求转换成为axis接口形式的TLP或配置管理接口信号。这些请求主要包含初始化配置请求和门铃写请求,初始化配置请求由初始化模块发起,当配置请求的