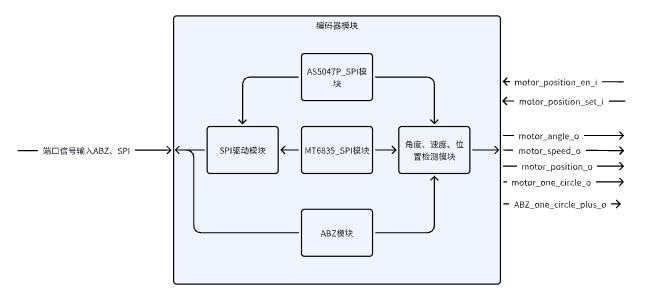

FPGA FOC编码器模块详解:AS5047P与MT6835驱动方案

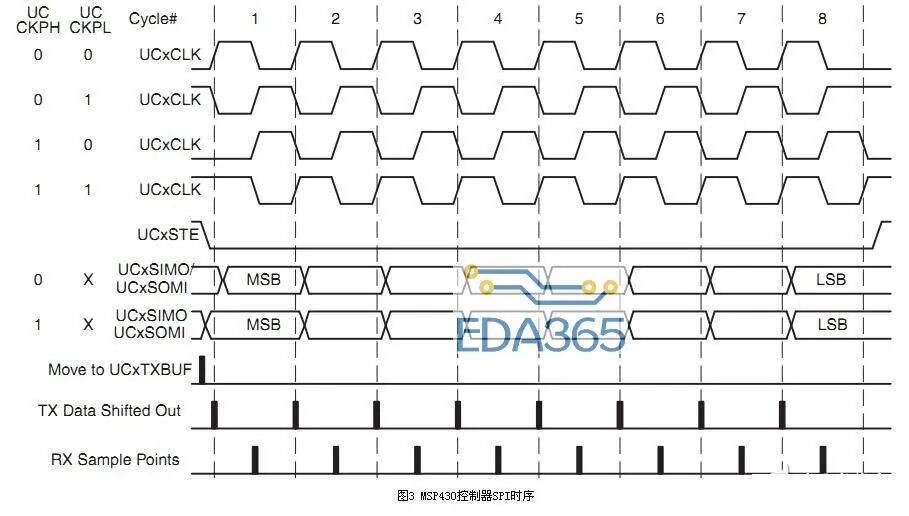

以下文章来源于FPGA之旅,作者电击小子 一. 简介 在使用有感FOC算法的时候,离不开使用编码器来获取电机角度,编码器的种类非常多,常见的有AS5600、AS50

关于「嵌入式与微控制器系统」的技术文章、设计资料与工程师讨论,持续更新。

以下文章来源于FPGA之旅,作者电击小子 一. 简介 在使用有感FOC算法的时候,离不开使用编码器来获取电机角度,编码器的种类非常多,常见的有AS5600、AS50

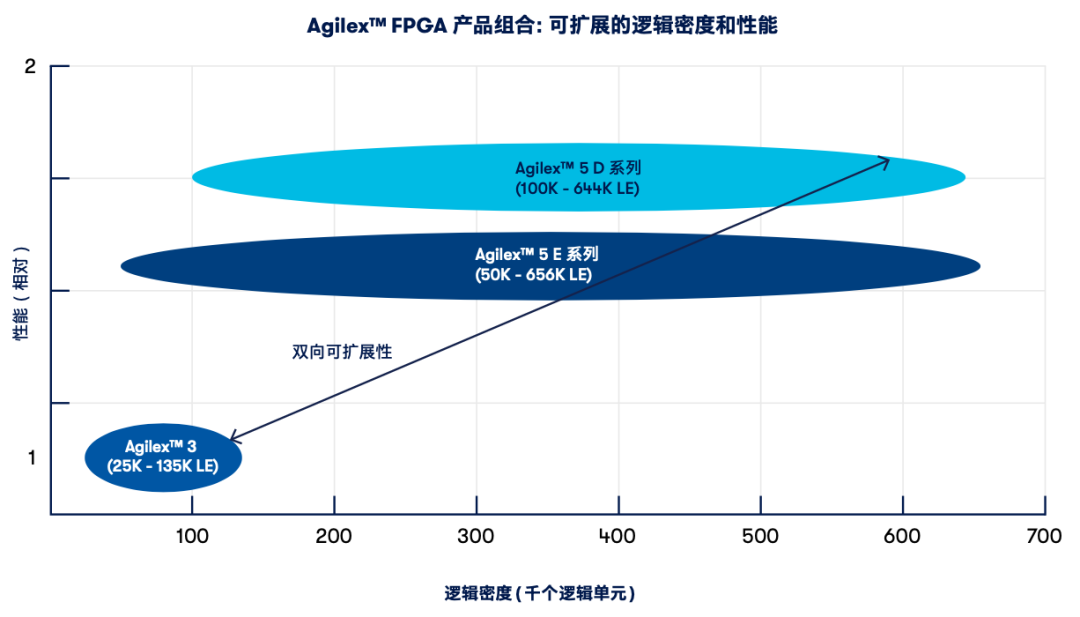

Agilex 5 FPGA 和 SoC以及新推出的Agilex 3 FPGA 和 SoC代表着可编程逻辑技术方面的重大飞跃。这两个设备系列均具备全新功能,可随着设计需求的变

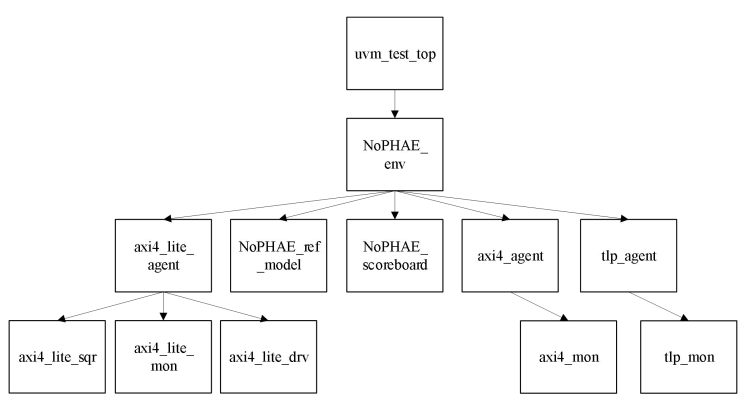

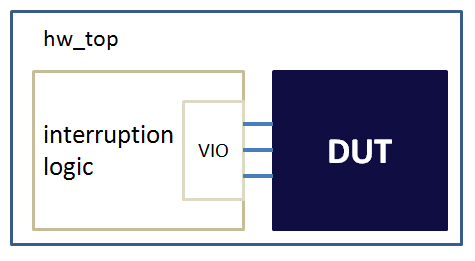

UVM 验证包设计结构如图 1 所示。 UVM 验证包的主要功能是对 DUT 提供激励, 仿真验证对应的功能, 并对测试结果进行自动对比分析与统计。 验证包包含一个NoPH

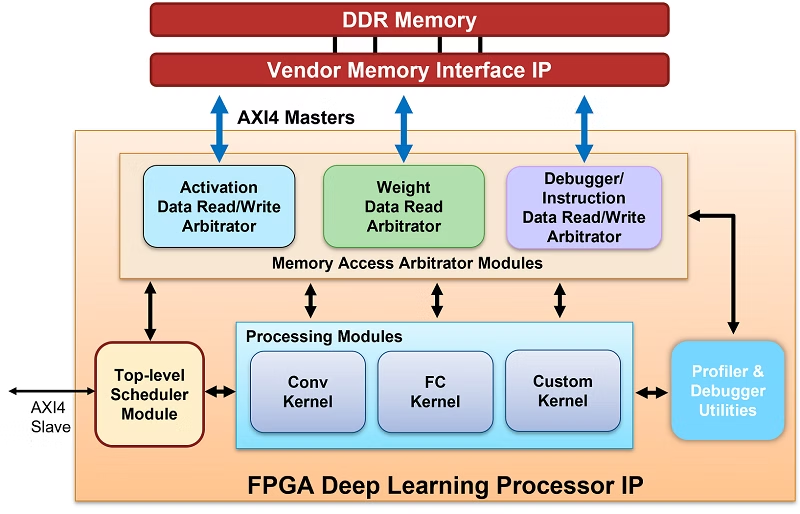

如果你已经在用 MATLAB 做深度学习,那一定知道它的训练和仿真体验非常丝滑。但当模型要真正落地到 FPGA 上时,往往就会卡住:怎么把网络结构和权重优雅地搬到硬件里?

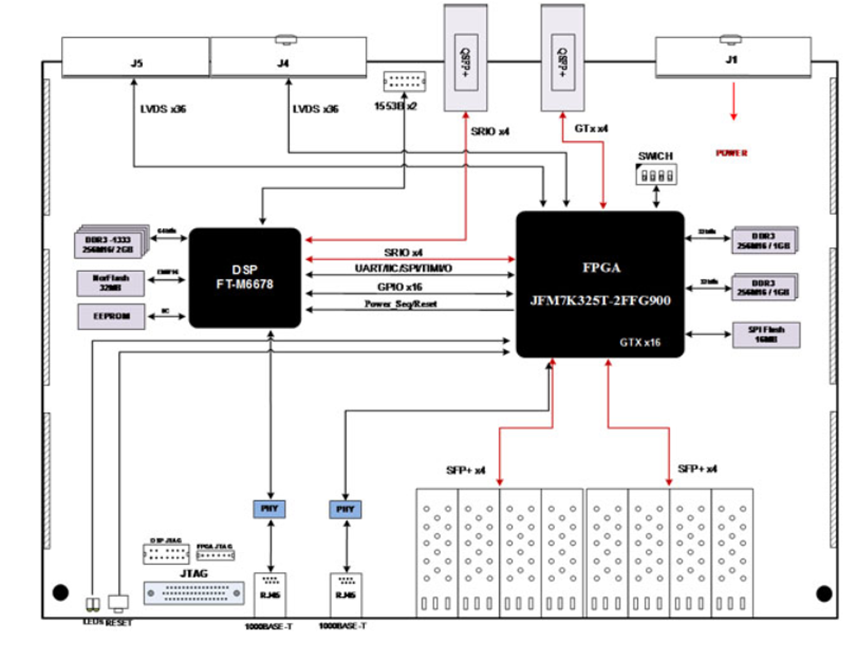

以下文章来源于FPGA算法工程师,作者18线工程师 自中高端FPGA技术成熟以来,FPGA+DSP/ARM架构的硬件设计在众多工业领域得到广泛应用。例如无线通信、图像处

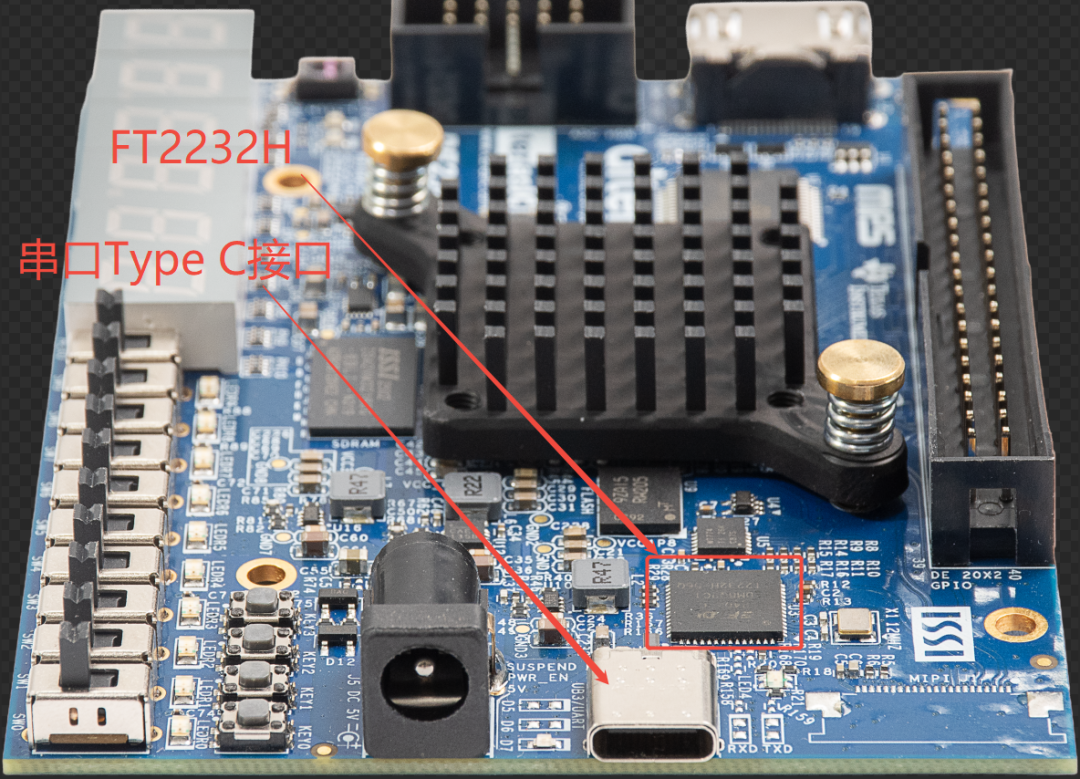

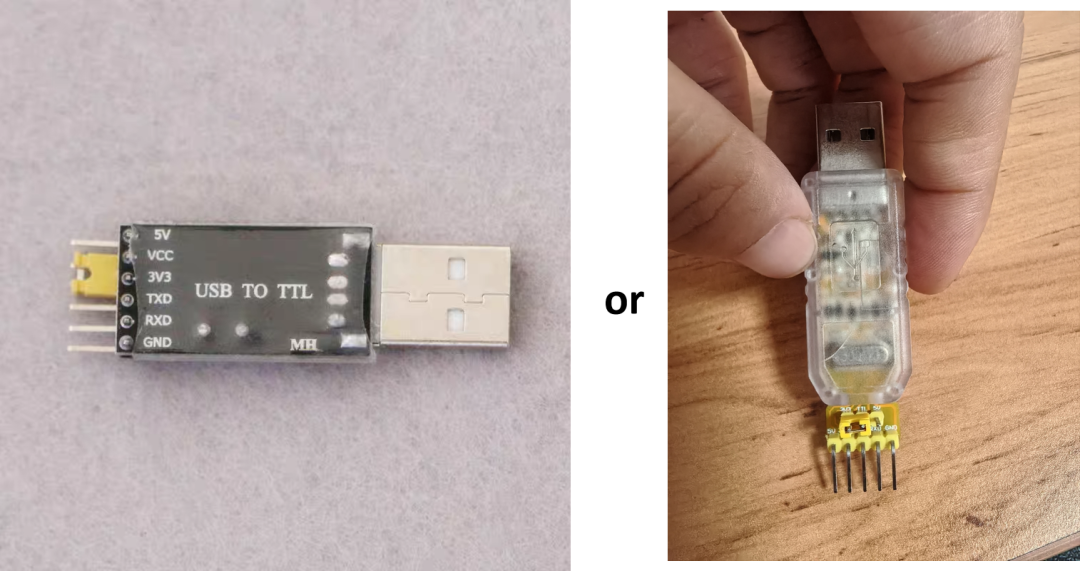

1开发板串口简介 DE23-Lite开发板提供了一个UART通信接口(物理接口是下图的Type C接口),用户能够通过主机与Agilex 3 FPGA进行串口通信。

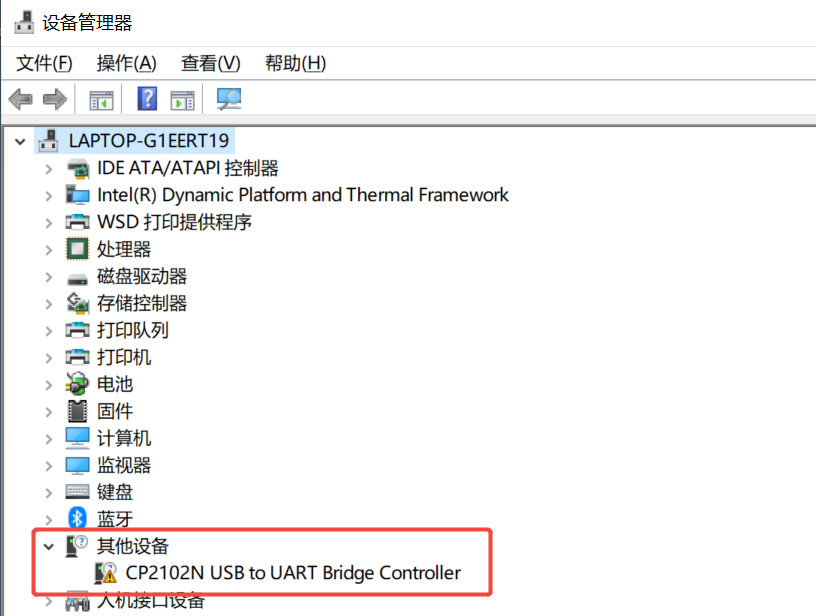

本文详细介绍基于Terasic FPGA开发板TSP(又名C5P和OSK)和其板载CP2102N USB-UART桥接芯片的串口通信系统设计与实现。系统采用Verilog

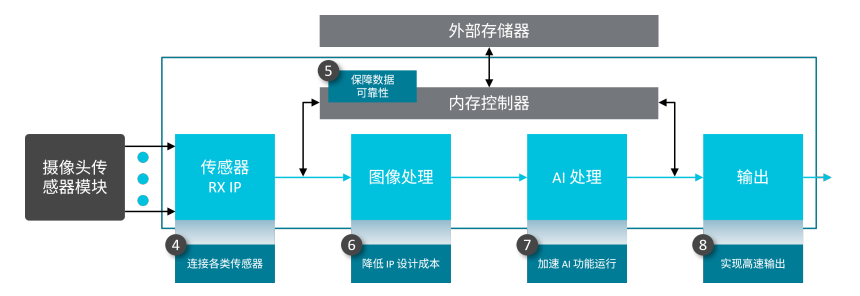

作者:Wayne Lyons AMD 汽车业务高级总监 2024 年至 2030 年间,高度自动化汽车每年的出货量将以 41% 的复合年增长率增长。这种快速增长导致

本文适用于DE10-Standard、T-Core、DE1-SOC以及DE10-Nano等有GPIO引脚外扩的FPGA开发板。 串口通信协议基础知识请参考:1-串行通信

10月28日-30日,“2025深圳机器视觉展暨机器视觉技术及工业应用研讨会(Vision China 深圳)”在深圳国际会展中心盛大举办,本次展会聚焦机器视觉技术在电子制

如果对处于全速(at-speed)运行下的FPGA调试,工程师在现有通用“能力技术”基础上,再增加“硬件断点”功能,那么对高速运行FPGA,也就拥有像调试软件程序类似的完整

概述 如今,工业行业对生产力和自动化的追求不断升级,推动先进机器视觉系统需求持续增长。 机器视觉摄像头既需要满足低成本、低功耗与紧凑尺寸等要求,又需要兼容全新的传感

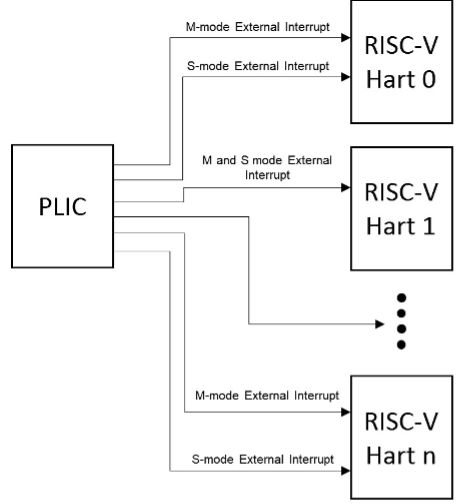

随着 RISC -V处理器在 FPGA 领域的广泛应用,易灵思 FPGA 的 Sapphire RISC-V 内核凭借软硬核的灵活支持,为开发者提供多样选择。本文深入探讨

简介:本文介绍了一个基于FPGA的内存到串行数据传输模块,该模块设计用来高效地处理存储器中的数据并传输至串行接口。项目中自定义的“datamover_mm2s_fpga_”

简介:本例程详细介绍了如何在FPGA上实现Serial RapidIO(SRIO)通信协议,并通过Verilog语言进行编程设计。SRIO作为一种高速、低延迟的串行互连技术

Quartus Prime 专业版 25.3 现已正式发布, FPGA AI 套件 25.3 版本同步亮相。新版软件实现了 FPGA 设计效率的重大飞跃,带来了更智能的工具

简介:Xilinx FPGA因其高性能和低延迟,常用于串行通信接口设计。本文深入分析了Aurora、PCI Express和Serial RapidIO这三种在Xilinx

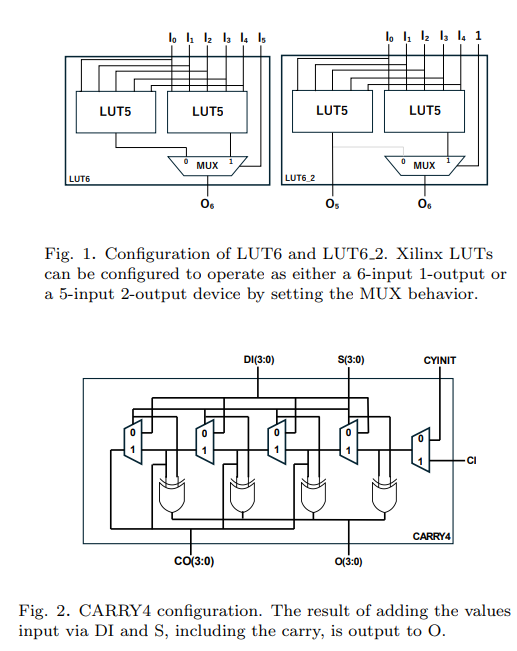

以下文章来源于OpenFPGA,作者碎碎思 ——来自 Shinshu University 的最新设计揭示低位宽算术硬件化的新途径 原标题:Hardware-Effi

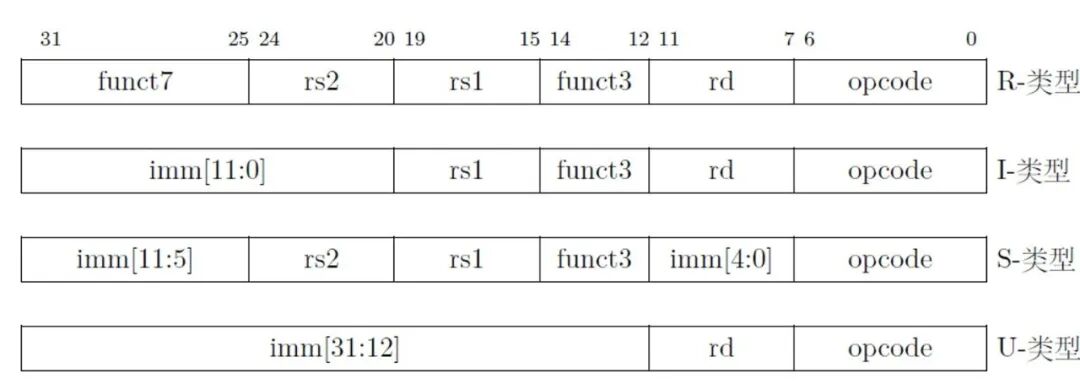

RISC-V(Reduced Instruction Set Computing-V)是一个开源指令集架构(ISA),它的设计目标是提供一个简洁、可扩展且高效的指令集,适用

Agilex 5 D 系列 FPGA 和 SoC 家族全面升级,为中端 FPGA 应用能力带来巨大飞跃——逻辑单元、内存、DSP/AI算力提升高达 2.5 倍,外存带宽提升