2025紫光同创FPGA技术研讨会:Logos2/Titan2方案助力智能化升级

“2025紫光同创FPGA技术研讨会”深圳站&广州站即将盛大启航!作为紫光同创生态合作伙伴,小眼睛科技将携多个基于紫光同创FPGA方案亮相,此次展示的解决方案覆盖了工业

关于「嵌入式与微控制器系统」的技术文章、设计资料与工程师讨论,持续更新。

“2025紫光同创FPGA技术研讨会”深圳站&广州站即将盛大启航!作为紫光同创生态合作伙伴,小眼睛科技将携多个基于紫光同创FPGA方案亮相,此次展示的解决方案覆盖了工业

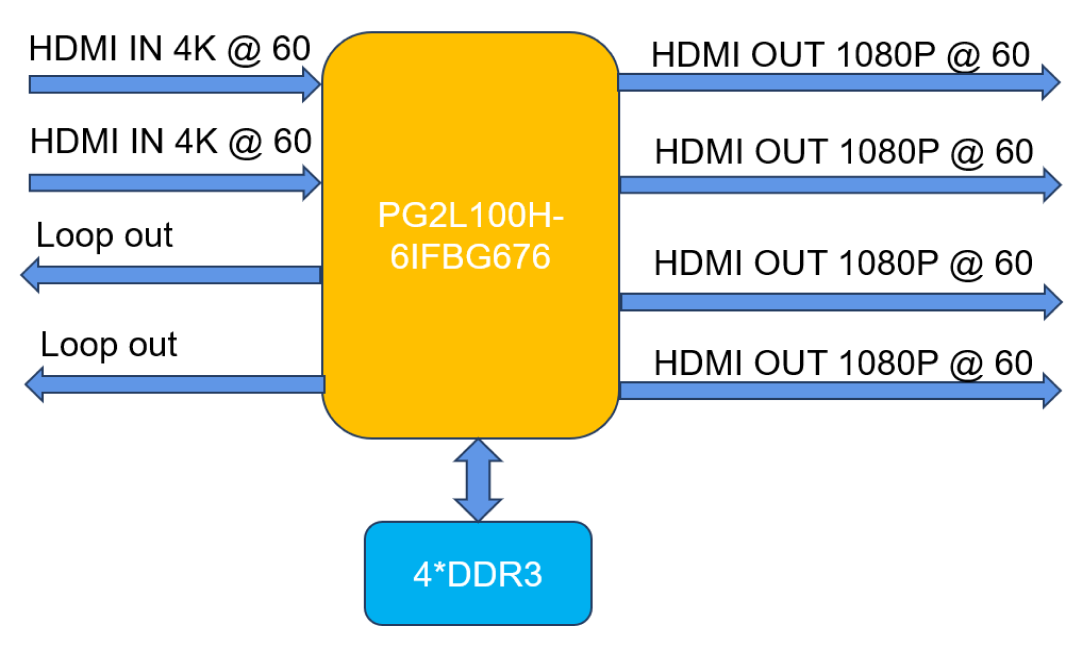

国产芯片的崛起与创新组合RK3568:强大性能的核心引擎紫光同创PG2L50H灵活定制的硬件利器强强联合 聚势而生RK3568+紫光同创PG2L50HRK3568与紫光同创PG

第1节 什么是 FPGA FPGA 的全称为 Field-Programmable Gate Array,即现场可编程门阵列。 FPGA 是在 PAL、 GAL、 CP

本篇文章来自 FPGA 大神、Ardiuvo & Hackster.IO 知名博主 Adam Taylor。在这里感谢 Adam Taylor 对 ALINX 产品

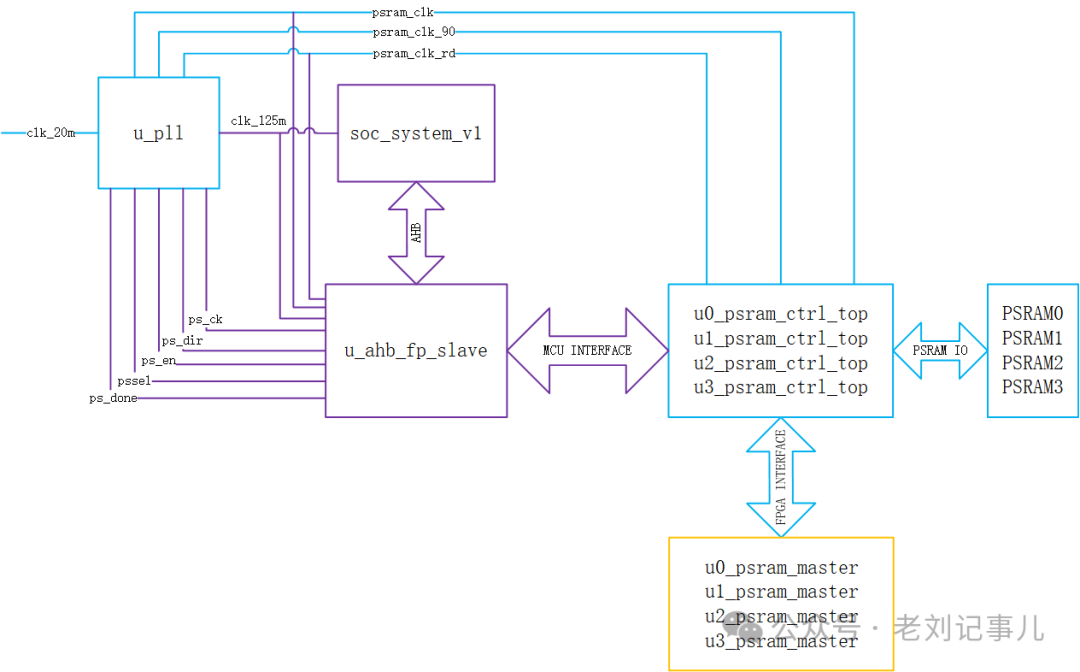

来源:老刘记事儿 最近有客户反映国产FPGA京微齐力P2器件内部合封的pSRAM控制器读写效率很高,能达80%以上,而且合封了4片8bit位宽pSRAM芯片,按250M

在工业通信领域,技术革新与突破始终是推动行业发展的核心动力。今天,为大家带来基于DSMC/FlexBus并口的RK3576J与FPGA通信方案,核心板国产化率高达100%,

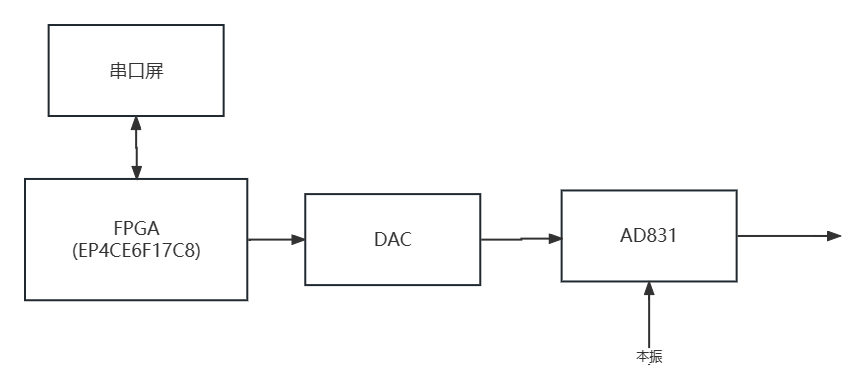

摘要:本系统由FPGA、串口屏、DAC模块和AD831组成。FPGA通过调用宏功能模块NCO,按照输入时钟50MHz,产生相应频率正弦信号输出,共产生两路,一路为调制信号,

PolarFireCore器件价格降低30%,同时保留了经典PolarFire系列市场领先的能效、安全性和可靠性 当前市场中,物料清单(BOM)成本持续攀升,开发者需在

“之前的文章嵌入式基础构架 from andrew@labs介绍了大型嵌入式项目的构架,本文将深入介绍 MCU 到 FPGA 的内存映射方案。” 首先回顾,我为未

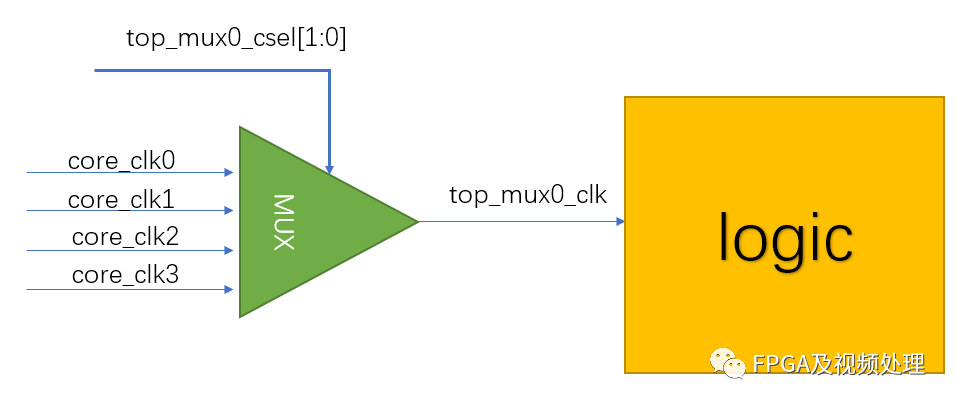

在trion要实现一个4选1时钟复用或许比较麻烦。但是在钛鑫上已经给出了解决方案。这里以Ti60F225为例来介绍如何实现下面的4选择1时钟选择功能。 在FPGA

近年来,在政策驱动、国产化等趋势下,国内对FPGA相关人才的需求激增,培养出具备创新思维、坚实的理论基础与实践能力的人才是当前行业发展的重要目标之一。 作为国产FPGA

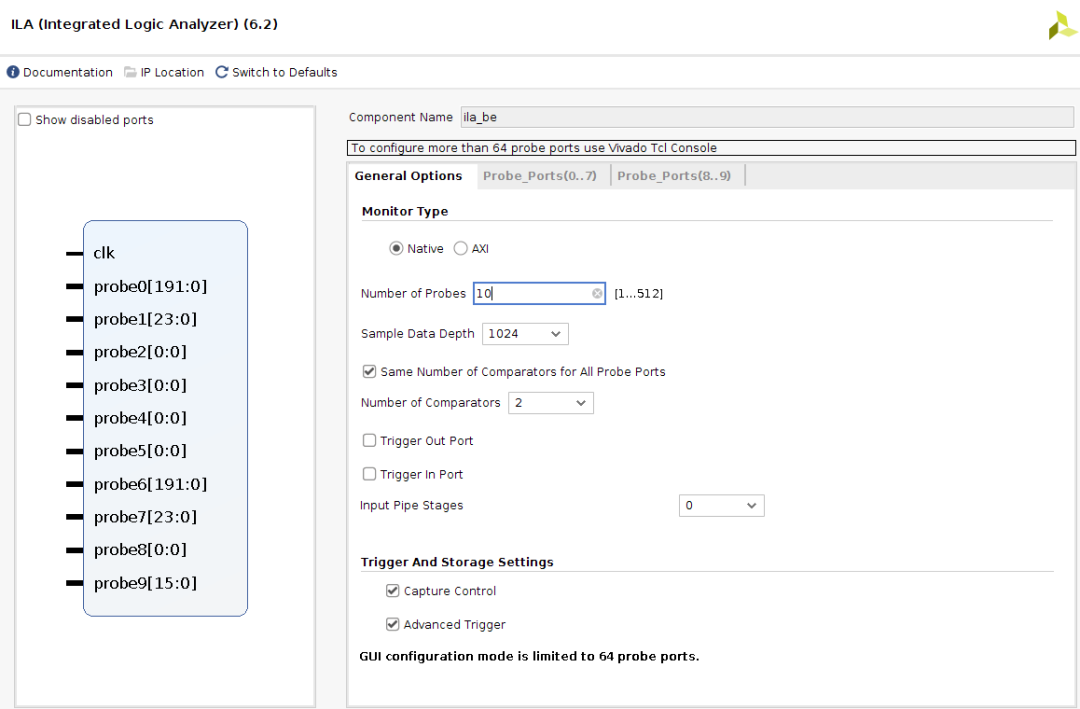

在Vivado中,VIO(Virtual Input/Output)是一种用于调试和测试FPGA设计的IP核,它允许设计者通过JTAG接口实时读取和写入FPGA内部的寄存器

确保对长生命周期应用的持续供货支持 罗彻斯特电子与Lattice达成合作,向全球客户供应精选的Lattice现场可编程门阵列产品(FPGA)。 Lattice作为全

作者:Ryan Koehn AMD Versal 自适应 SoC 高级产品线经理 去年,我们推出了 AMD 第二代 Versal AI Edge 系列和第二代 Ve

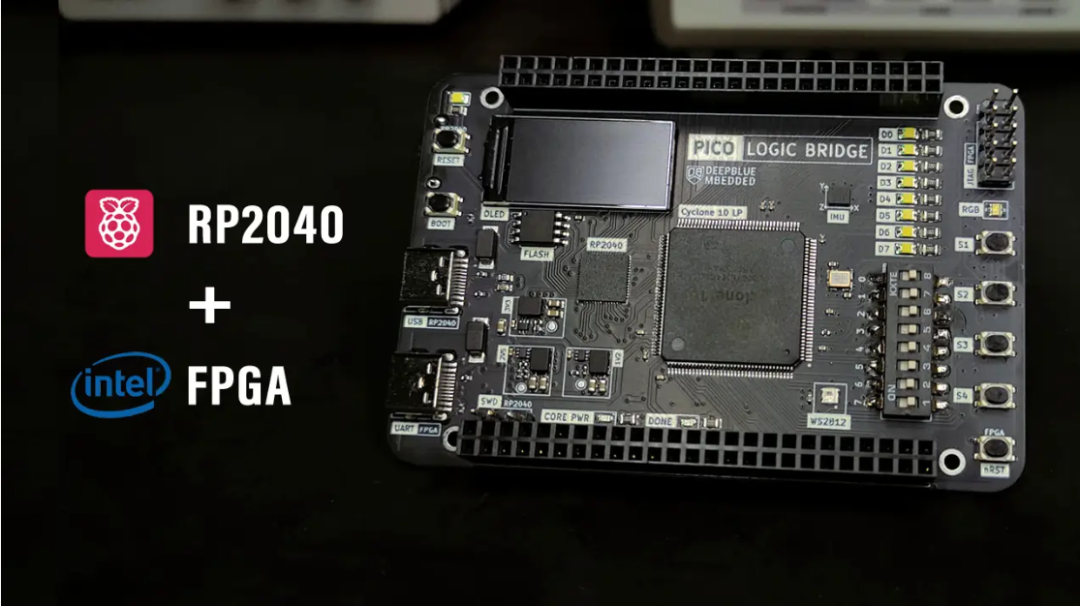

“在本文中,我将向大家展示一个结合了树莓派Pico (RP2040) 与 Cyclone 10 FPGA 的PCB设计项目。我将解释项目中的一些设计决策

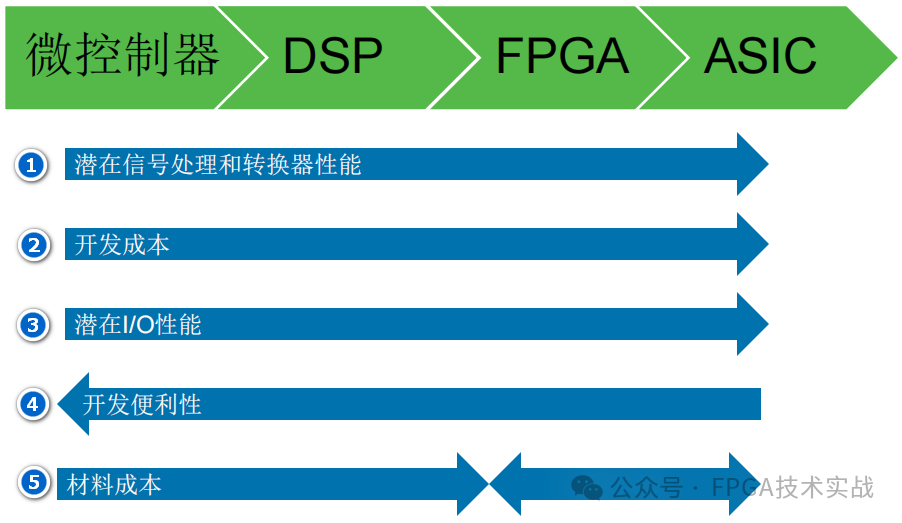

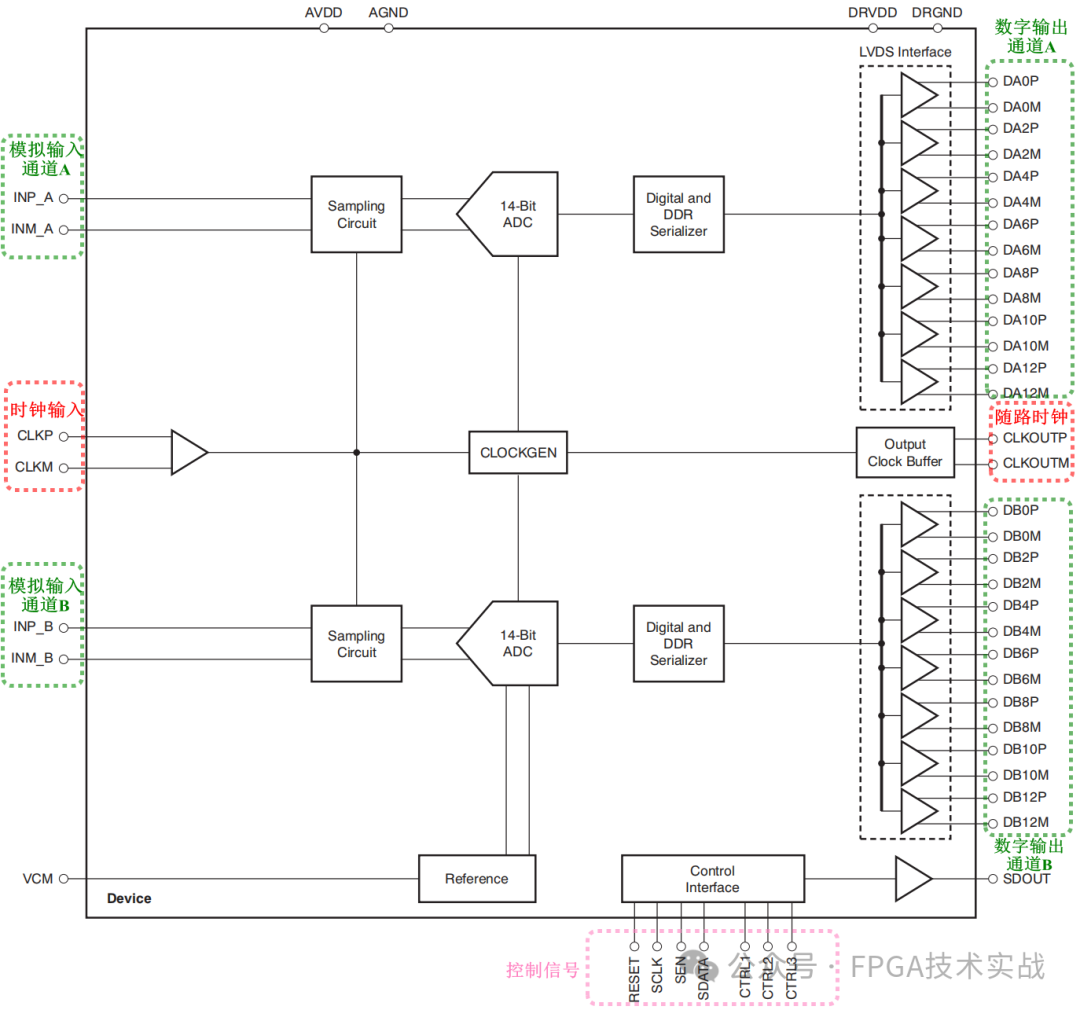

引言:本文介绍FPGA与高速ADC接口方式和标准以及JESD204与FPGA高速串行接口。 1. 高速ADC与处理器互联需要权衡的因素 如图1所示,ADC模数转换器

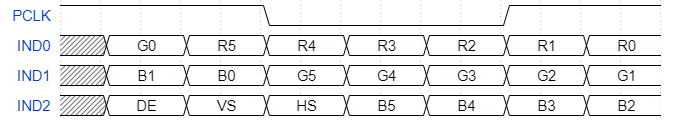

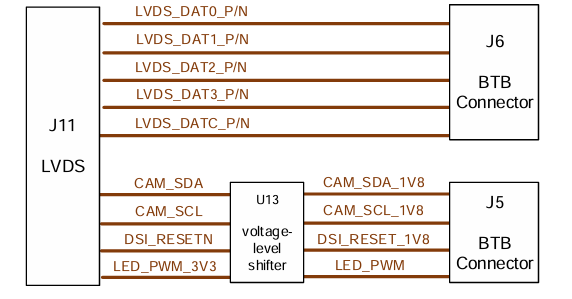

实现将SC130GS采集的黑白图像数据缓存进DDR3,并以1024*600@60的视频时序输出到LVDS 屏幕显示。其中,DDR3工作频率为600MHz,SC130GS输

引言:本文以TI的ADS4249(ADC)和DAC3482(DAC)之间的接口为例,介绍Altera FPGA与ADC/DAC之间的DDR LVDS接口设计以及时序约束详细

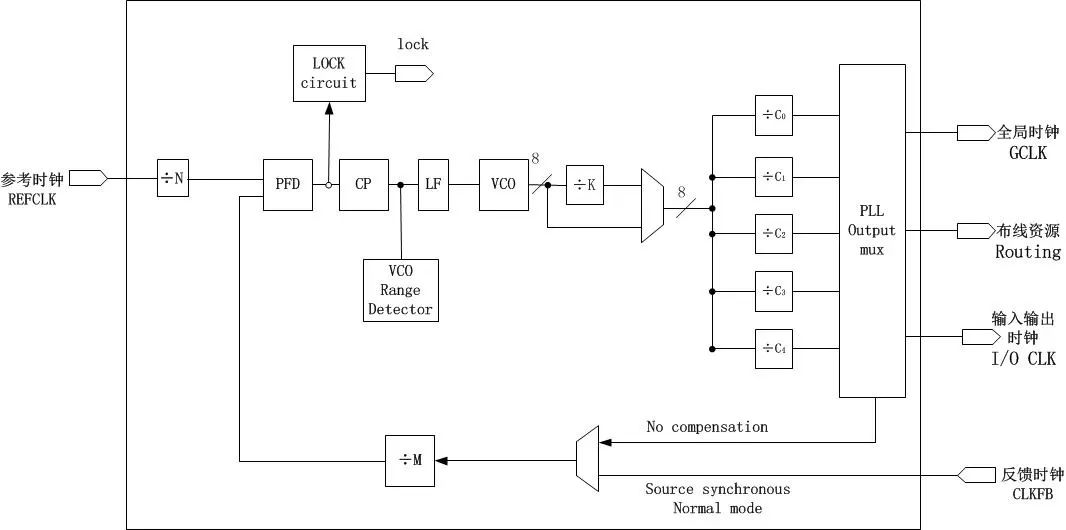

No.1引言 随着现代电子系统的不断发展,时钟管理成为影响系统性能、稳定性和电磁兼容性(EMI)的关键因素之一。在FPGA设计中,PLL因其高精度、灵活性和可编程性而得

AI 正在向边缘迁移 从聊天机器人、内容生成到高级数据分析,AI 已无处不在。过去,大多数 AI 处理都在云端完成。然而,随着模型功能日益强大以及对实时洞察的需求持续增