罗彻斯特电子与Lattice合作:提供长生命周期FPGA支持

确保对长生命周期应用的持续供货支持 罗彻斯特电子与Lattice达成合作,向全球客户供应精选的Lattice现场可编程门阵列产品(FPGA)。 Lattice作为全

关于「FPGA」的技术文章、设计资料与工程师讨论,持续更新。

确保对长生命周期应用的持续供货支持 罗彻斯特电子与Lattice达成合作,向全球客户供应精选的Lattice现场可编程门阵列产品(FPGA)。 Lattice作为全

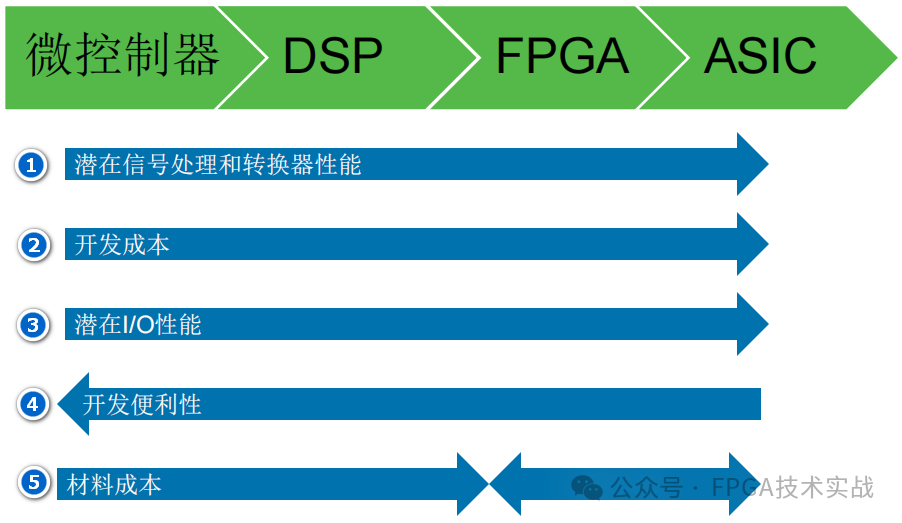

引言:本文介绍FPGA与高速ADC接口方式和标准以及JESD204与FPGA高速串行接口。 1. 高速ADC与处理器互联需要权衡的因素 如图1所示,ADC模数转换器

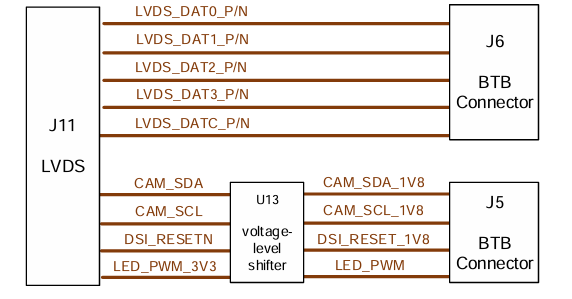

实现将SC130GS采集的黑白图像数据缓存进DDR3,并以1024*600@60的视频时序输出到LVDS 屏幕显示。其中,DDR3工作频率为600MHz,SC130GS输

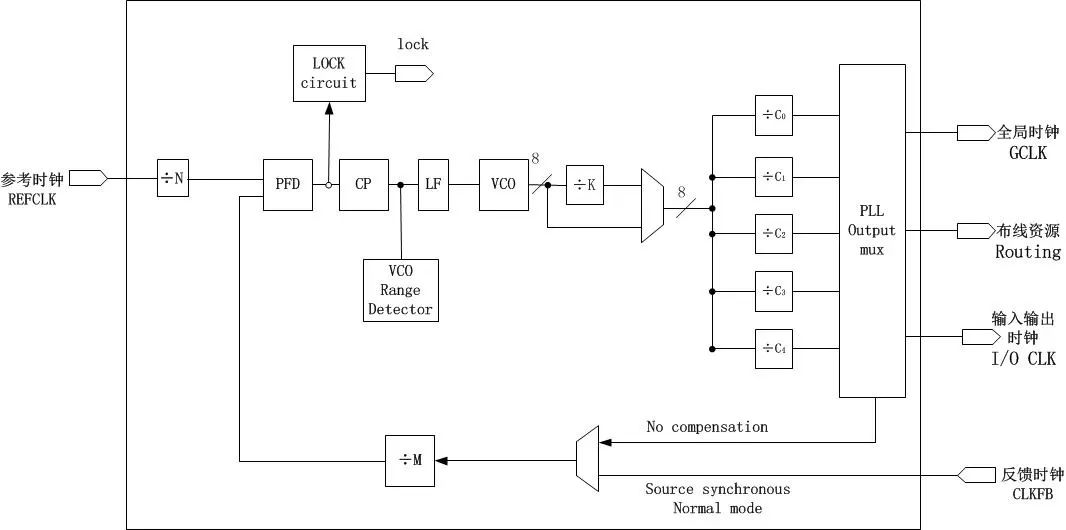

No.1引言 随着现代电子系统的不断发展,时钟管理成为影响系统性能、稳定性和电磁兼容性(EMI)的关键因素之一。在FPGA设计中,PLL因其高精度、灵活性和可编程性而得

AI 正在向边缘迁移 从聊天机器人、内容生成到高级数据分析,AI 已无处不在。过去,大多数 AI 处理都在云端完成。然而,随着模型功能日益强大以及对实时洞察的需求持续增

电子发烧友网报道(文/黄晶晶)赛灵思(Xilinx)推出的第一款FPGA芯片XC2064于1985年6月问世,它有600个门,64个可配置逻辑块,运行频率为70MHz。这款

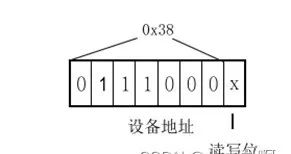

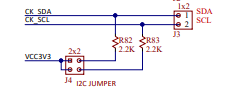

概念 传感器输出经过标定的数字信号输出,通过标准的I2C接口传输数据; 相对湿度的分辨率在0.024%RH,工作范围为0~100%RH; 温度值的分辨率在0.0

近日,被誉为 “全球移动通信行业发展风向标” 的 2025世界移动通信大会(MWC上海)在上海新国际博览中心圆满落幕。本届大会以 “开启智能互联新纪元” 为主题,吸引全球创

近日,“2025智多晶FPGA技术研讨会”在武汉成功举办。本次交流会以“智绘新篇 晶质领航”为主题,智多晶专业技术团队在会上揭晓了公司匠心打造的多款FPGA芯片新产品、多项

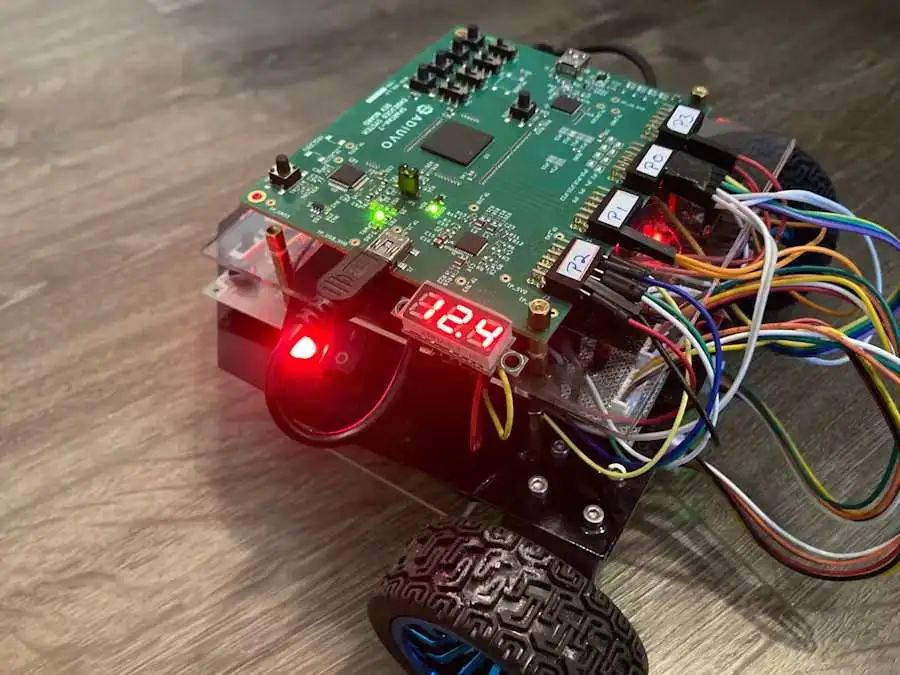

借助Verilog,在FPGA中实现了带编码器的两台电机的电机控制系统的RTL级设计。 介绍 借助硬件描述语言 (HDL) Verilog 和 AMD Viv

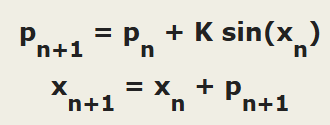

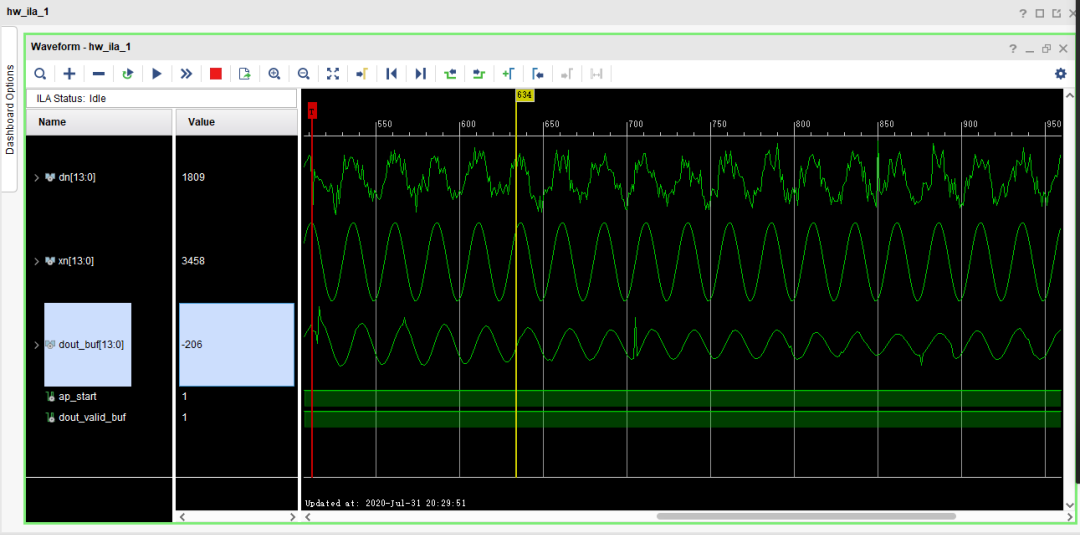

引言 今天继续常春藤名校之一——康奈尔大学的FPGA课程ECE 5760典型案例分享:基于DE1-SOC开发板的Chirikov标准映射求解器。 1. 项目概述

2025年7月1日至3日,欧洲 FPGA大会在德国慕尼黑盛大举行。作为FPGA领域的年度盛会,此次大会吸引了来自全球各地的企业、专家与学者,共同探讨FPGA技术的前沿趋势与应用

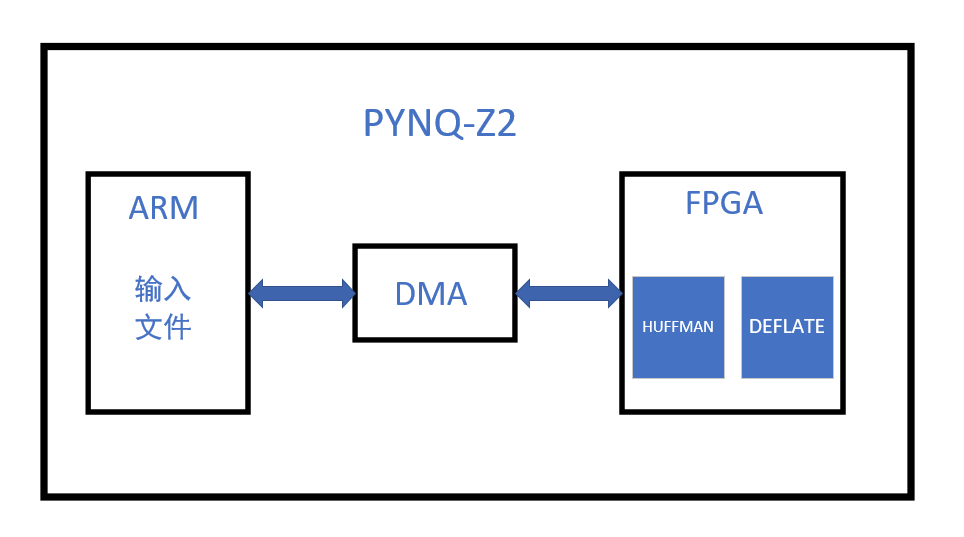

第一部分 设计概述 /Design Introduction 1.1设计目的 本设计中,计划实现对文件的压缩及解压,同时优化压缩中所涉及的信号处理和计算密集型

第一部分 设计概述 /Design Introduction 1.1设计目的与应用 随着人工智能的发展,神经网络正被逐步应用于智能安防、自动驾驶、医疗等各行各

第一部分 设计概述 自适应滤波是近几十年发展起来的信号处理理论的的新分支。随着人们在该领域研究的不断深入,自适应处理的理论和技术日趋完善,其应用领域也越来越广泛。自适

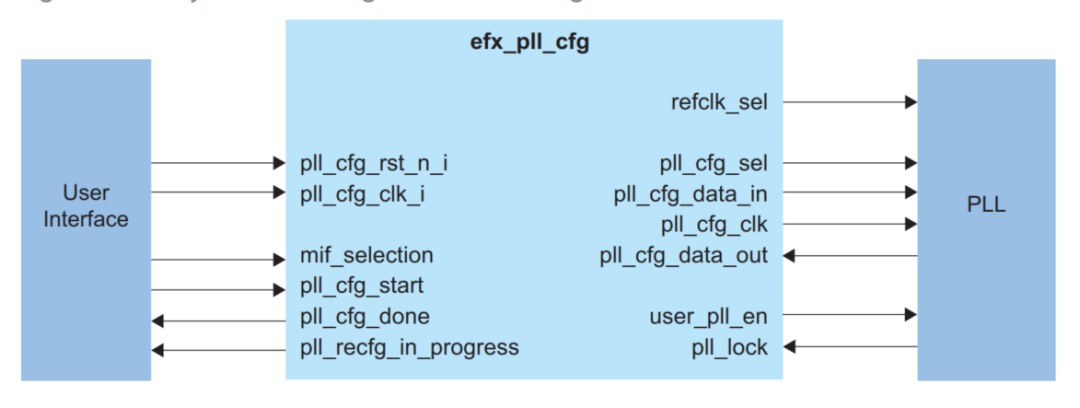

TJ375已经支持PLL的动态配置。打开PLL在Advance Settings中的Dynamic Reconfiguration中勾选Enable就可以了。最大可以支持8

来源:OpenFPGA;;作者:碎碎思 在本文中,我们将介绍如何构建带有VGA输出的低分辨率热成像。该解决方案基于Melexis MLX90640红外阵列、FPGA S

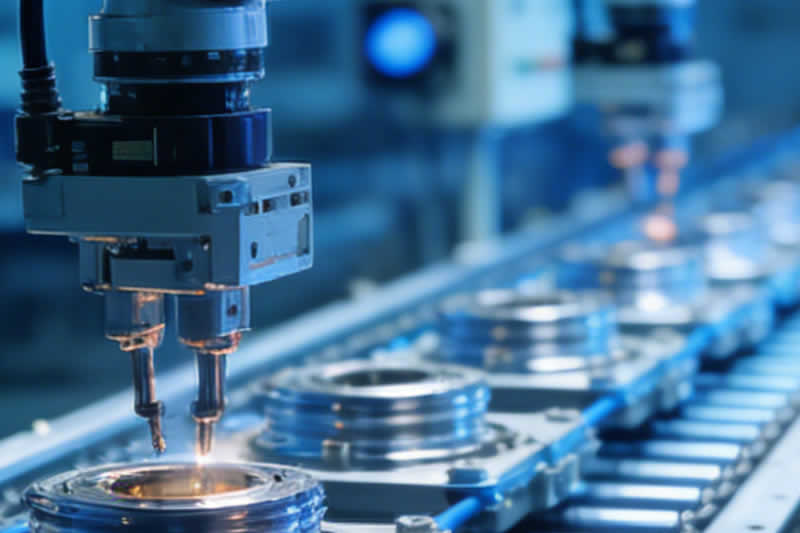

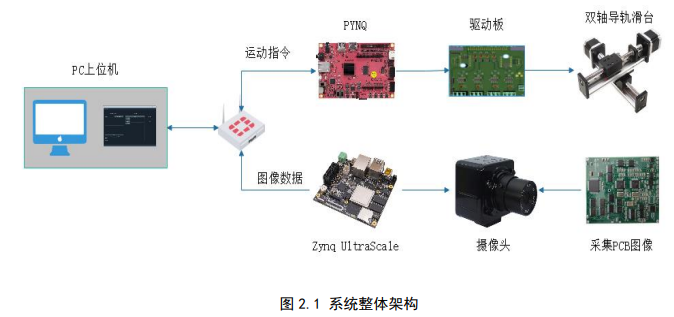

第一部分 设计概述 1.1 设计目的 作为电子产品最重要的组成部分,印刷电路板(PCB)的设计日趋复杂和器件尺寸的缩小,促使对 SMT 可靠性提出了更高的要求。因此

FPGA 在机器学习中的应用 随着机器学习和人工智能技术的迅猛发展,传统的中央处理单元(CPU)和图形处理单元(GPU)已经无法满足高效处理大规模数据和复杂模型的需求。

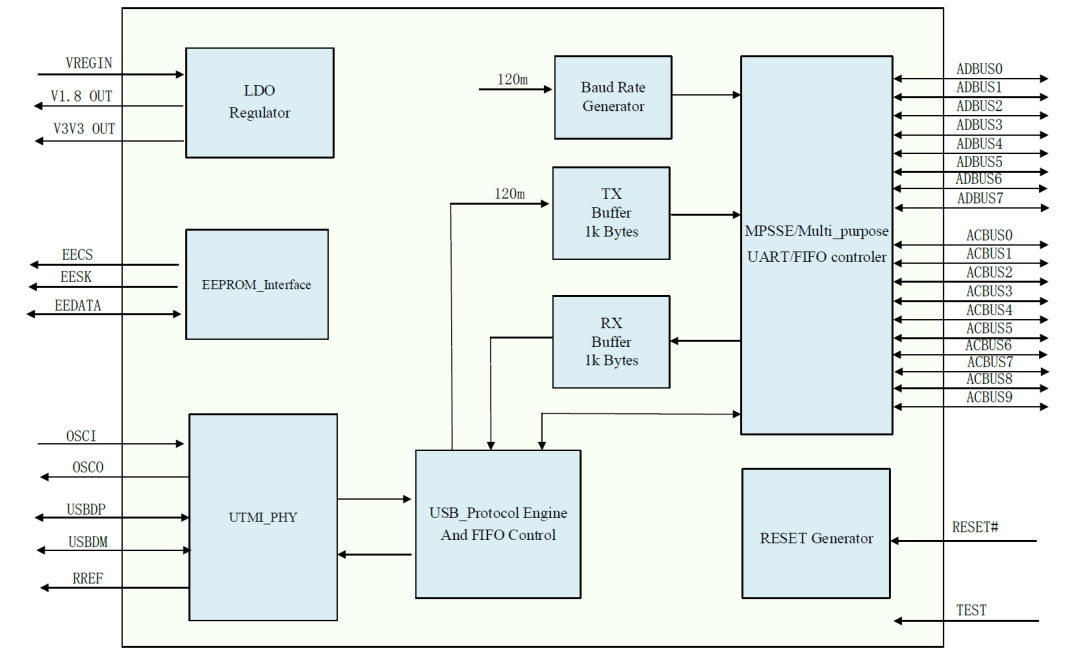

USB英文全称 Universal Serial Bus,即通用串行总线,是一个外部总线标准,用于规范电脑与外部设备的连接和通讯。 FTDI 公司的USB2.0 芯片F