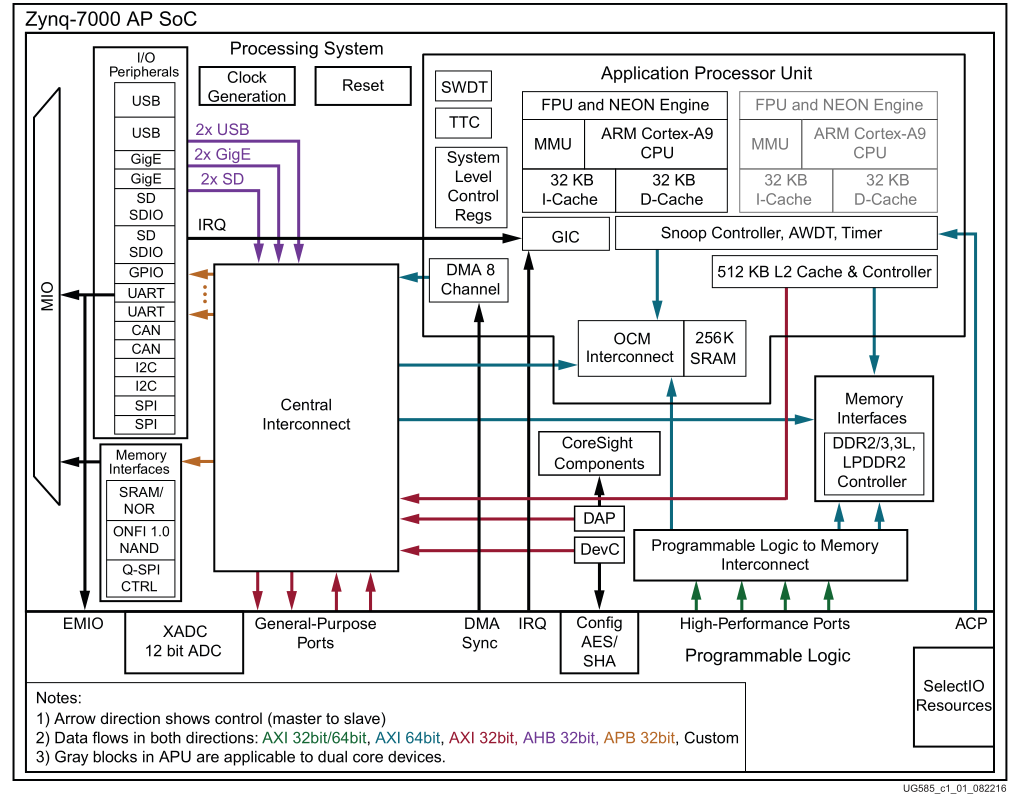

Zynq全可编程片上系统详解:高性能ARM+FPGA集成方案

以下文章来源于郝旭帅电子设计团队,作者郝旭帅 本篇主要是Zynq全可编程片上系统详解。 1. 什么是 Zynq? Zynq 是由赛灵思(Xilinx,现为 AM

关于「Xilinx (赛灵思)」的技术文章、设计资料与工程师讨论,持续更新。

以下文章来源于郝旭帅电子设计团队,作者郝旭帅 本篇主要是Zynq全可编程片上系统详解。 1. 什么是 Zynq? Zynq 是由赛灵思(Xilinx,现为 AM

以下文章来源于OpenFPGA,作者碎碎思 在之前文章中,我们介绍了如何使用 XSCT 工具通过 JTAG 在 Zynq SoC 上启动嵌入式 Linux 镜像(从 JT

简介:本文介绍如何利用FPGA和DMA技术处理来自AD9280和AD9708 ADC的数据。首先,探讨了这两种ADC的特点及其与FPGA的接口兼容性。接着,详细说明了使用X

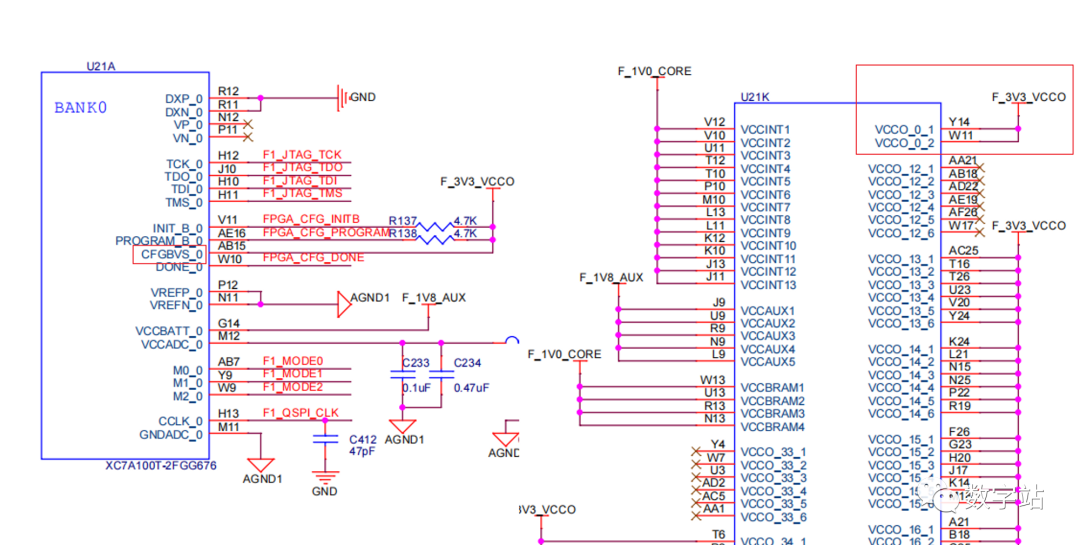

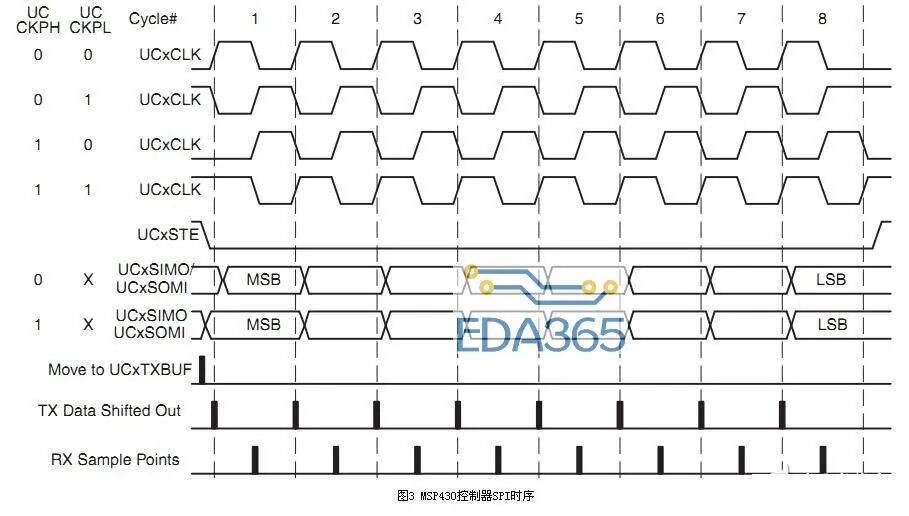

以下文章来源于数字站 本文旨在通过讲解不同模式的原理图连接方式,进而配置用到引脚的含义(手册上相关引脚含义有四、五页,通过本文理解基本上能够记住所有引脚含义以及使用场景

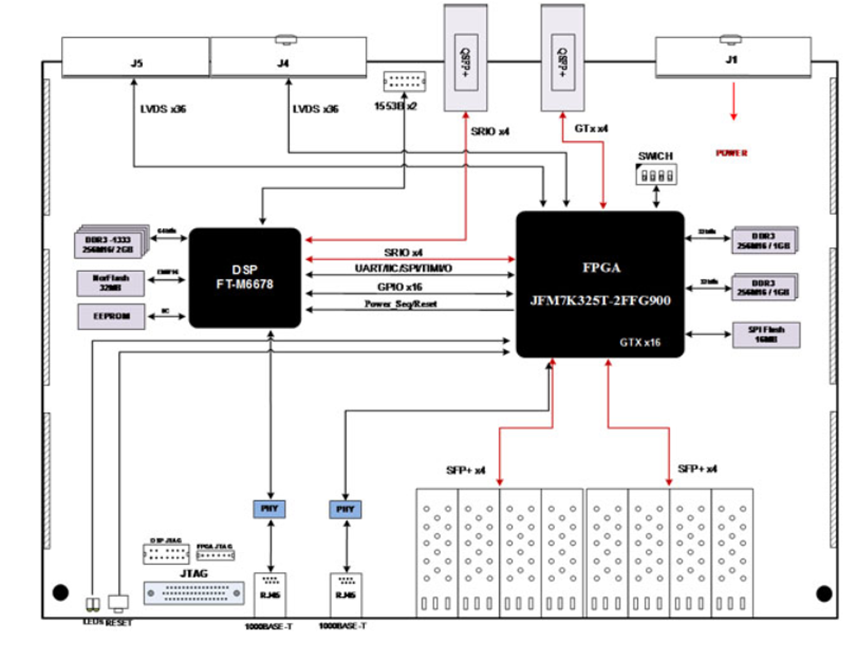

以下文章来源于FPGA算法工程师,作者18线工程师 自中高端FPGA技术成熟以来,FPGA+DSP/ARM架构的硬件设计在众多工业领域得到广泛应用。例如无线通信、图像处

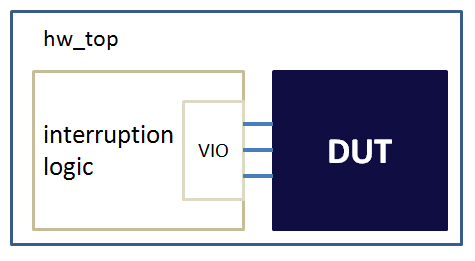

如果对处于全速(at-speed)运行下的FPGA调试,工程师在现有通用“能力技术”基础上,再增加“硬件断点”功能,那么对高速运行FPGA,也就拥有像调试软件程序类似的完整

简介:Xilinx FPGA因其高性能和低延迟,常用于串行通信接口设计。本文深入分析了Aurora、PCI Express和Serial RapidIO这三种在Xilinx

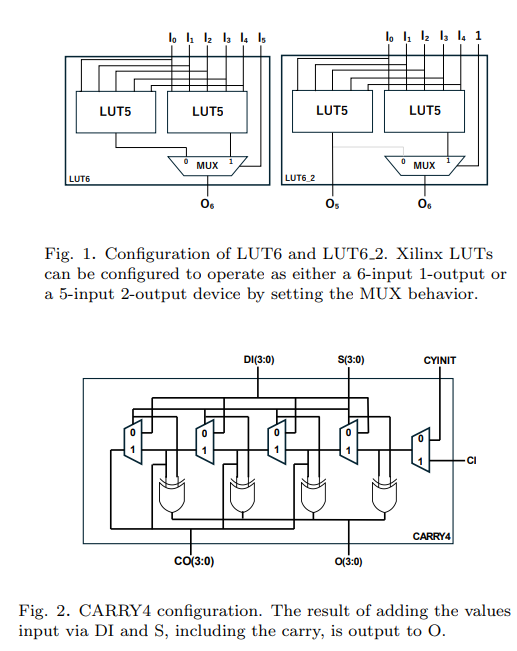

以下文章来源于OpenFPGA,作者碎碎思 ——来自 Shinshu University 的最新设计揭示低位宽算术硬件化的新途径 原标题:Hardware-Effi

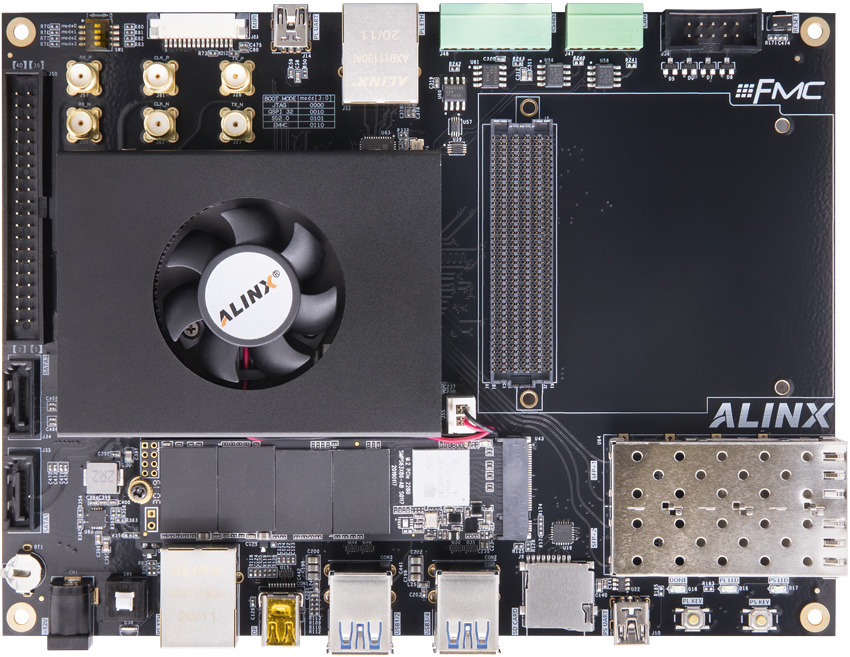

本教程在 Ubuntu22.04.1 虚拟机中安装了 Xilinx 2024.1 的开发环境,基于该环境从源码编译 PYNQ 3.1.2 工程,生成能够在 ALINX AX

以下文章来源于OpenFPGA,作者碎碎思 在各类行业与应用中,经常能看到许多 FPGA 设计。一个非常常见的现象是:设计者常常用复杂的有限状态机(FSM)来实现 I²