芯片设计中的ESD防护设计介绍

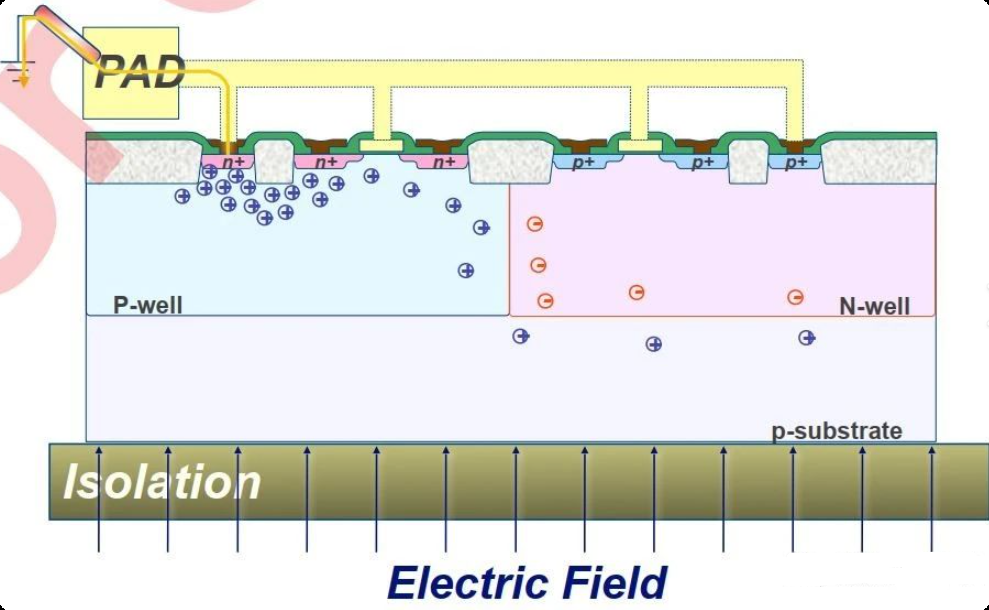

本文主要讲述芯片设计中的ESD防护设计介绍。 在集成电路(IC)的设计、制造、封装、测试及应用全流程中,静电放电(ESD)是最常见且破坏性极强的隐患之一。ESD放电时间虽仅为纳秒至微秒级,但瞬时峰值电流可达数十安培,足以击穿芯片内部的精密结构。因此,芯片设计时需要集成专用的ESD防护电路,在输入/输出引脚、电源引脚附近形成低阻抗放电通路,将静电能量旁路到地,避免核心电路受损。 ESD防护设计的核心

关于「MOS 管」的技术文章、设计资料与工程师讨论,持续更新。

本文主要讲述芯片设计中的ESD防护设计介绍。 在集成电路(IC)的设计、制造、封装、测试及应用全流程中,静电放电(ESD)是最常见且破坏性极强的隐患之一。ESD放电时间虽仅为纳秒至微秒级,但瞬时峰值电流可达数十安培,足以击穿芯片内部的精密结构。因此,芯片设计时需要集成专用的ESD防护电路,在输入/输出引脚、电源引脚附近形成低阻抗放电通路,将静电能量旁路到地,避免核心电路受损。 ESD防护设计的核心