用Python给Verilog设计自仿(一):Cocotb环境初探

1前言 很多FPGA/IC工程师擅长设计,但在仿真方面较为薄弱。我认为主要问题在于,完整的仿真实现学习成本较高,如学习UVM需要掌握大量新的内容。而单纯使用Verilog自仿又难以满足需求,以报文仿真为例,我们需要解析报文,若仅依赖Verilog自仿,就相当于要自己编写一个报文解析模块,工作量非常庞大。而Python在数据处理方面则更加高效,如果加以利用,完全可以快速构建一个完整的仿真模型。Coc

关于「仿真验证」的技术文章、设计资料与工程师讨论,持续更新。

1前言 很多FPGA/IC工程师擅长设计,但在仿真方面较为薄弱。我认为主要问题在于,完整的仿真实现学习成本较高,如学习UVM需要掌握大量新的内容。而单纯使用Verilog自仿又难以满足需求,以报文仿真为例,我们需要解析报文,若仅依赖Verilog自仿,就相当于要自己编写一个报文解析模块,工作量非常庞大。而Python在数据处理方面则更加高效,如果加以利用,完全可以快速构建一个完整的仿真模型。Coc

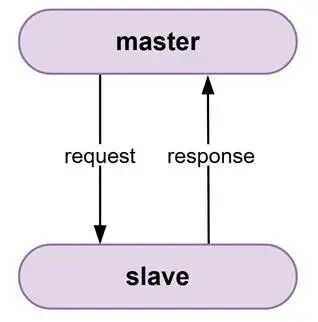

1 前言 2 模型介绍 如图1为该死锁模型,看起来是不是很简单,参与者就两个:master和slave。Master发起request需要slave做一些事情,slave反馈回response告知master这件事做的怎么样了。但就是这样简单的通信场景没有配合好就暗含死锁风险。 图1 死锁模型 为什么这个模型会死锁呢?比如master和slave都比较拧巴,master一定要让slave做某件事