用Python给Verilog设计自仿进阶:仿真器是如何工作的?一文看懂时序模型

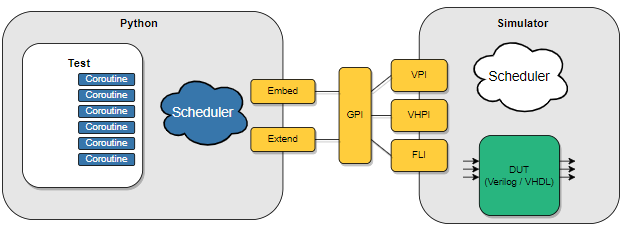

很多FPGA/IC工程师擅长设计,但在仿真方面较为薄弱。我认为主要问题在于,完整的仿真实现学习成本较高,如学习UVM需要掌握大量新的内容。而单纯使用Verilog自仿又难以满足需求,以报文仿真为例,我们需要解析报文,若仅依赖Verilog自仿,就相当于要自己编写一个报文解析模块,工作量非常庞大。而Python在数据处理方面则更加高效,如果加以利用,完全可以快速构建一个完整的仿真模型。Cocotb

关于「时序模型」的技术文章、设计资料与工程师讨论,持续更新。

很多FPGA/IC工程师擅长设计,但在仿真方面较为薄弱。我认为主要问题在于,完整的仿真实现学习成本较高,如学习UVM需要掌握大量新的内容。而单纯使用Verilog自仿又难以满足需求,以报文仿真为例,我们需要解析报文,若仅依赖Verilog自仿,就相当于要自己编写一个报文解析模块,工作量非常庞大。而Python在数据处理方面则更加高效,如果加以利用,完全可以快速构建一个完整的仿真模型。Cocotb