睿擎平台 FPGA 高速通信:DSMC 总线读写实战

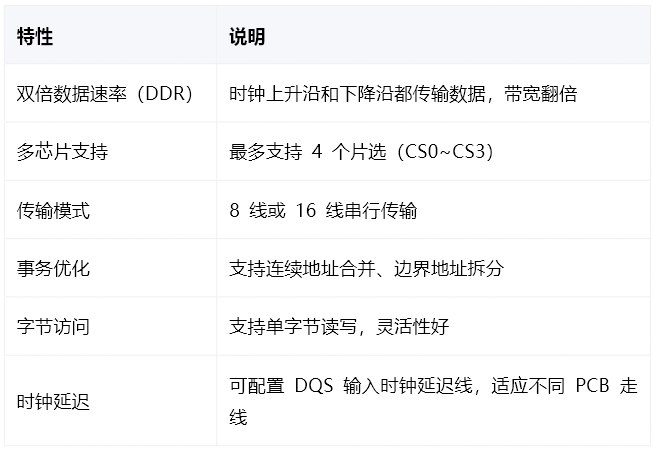

在工业控制和数据采集场景中,处理器与 FPGA 之间的高速数据交换是一个常见需求。传统方案通常采用 SPI(速度受限,一般 < 10Mbps)或 PCIE(带宽高但引脚多、设计复杂)。有没有一种方案,既能达到 几十 MB/s 的带宽,又只需要少量引脚,设计简单? 今天分享一个基于 睿擎派 RC3506 的方案——利用 RK3506 芯片内置的 DSMC(Double Data Rate Se

关于「RK3506」的技术文章、设计资料与工程师讨论,持续更新。

在工业控制和数据采集场景中,处理器与 FPGA 之间的高速数据交换是一个常见需求。传统方案通常采用 SPI(速度受限,一般 < 10Mbps)或 PCIE(带宽高但引脚多、设计复杂)。有没有一种方案,既能达到 几十 MB/s 的带宽,又只需要少量引脚,设计简单? 今天分享一个基于 睿擎派 RC3506 的方案——利用 RK3506 芯片内置的 DSMC(Double Data Rate Se