用Python给Verilog设计自仿(11):仿真的玄学问题——协程、阻塞、 事件驱动、时间驱动

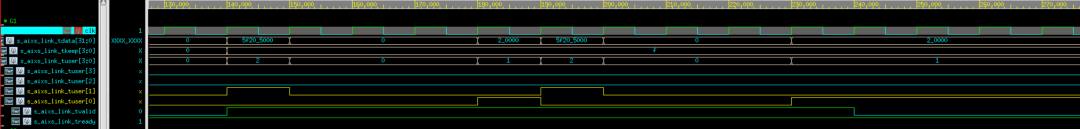

前言 在使用 cocotb 编写测试时,很多人可能都会遇到一些让人困惑的现象:比如说,你明明在发送一帧完整数据之后,加了 await RisingEdge(clk) 想等待 5 个周期再发下一帧,但在波形上却发现帧与帧之间并没有间隔;或者你在别的地方加了 Timer 也没起作用更甚至cocotb直接卡住不动了;又或者明明指定了发包数,却提前结束了。 这些现象的背后,其实不是 cocotb 出了问题