vcs+verdi仿真Verilog代码

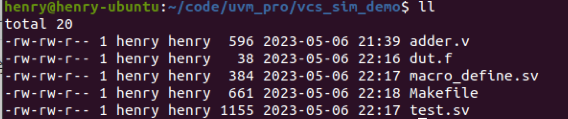

我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。 源文件内容如下: //adder.v module adder( input clk, input rst, input [9:0] A, input [9:0] B, output reg [10:0] C ); always @ ( pose

关于「Verdi」的技术文章、设计资料与工程师讨论,持续更新。

我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。 源文件内容如下: //adder.v module adder( input clk, input rst, input [9:0] A, input [9:0] B, output reg [10:0] C ); always @ ( pose

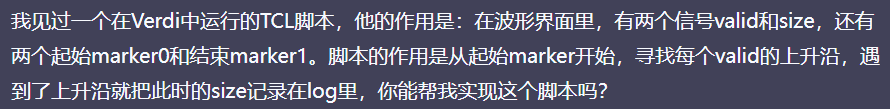

这个脚本在多年之前我就想做出来的,算是很执念的一件事。但是无奈自己的tcl编程能力和Verdi相关指令行掌握的太弱了,尝试了几次都没有成功。而这次我决定借助大模型力量再试一次,所以对着DS描述了这个脚本的行为: 但是后面想了想,描述的不够准确,于是进行了第二次描述: 其实想要的效果就是这样的(完成版): 讲真当年看到这个脚本的实现效果时真的是迷得我走不动道,所以这次必须要实现出来。 要在Ve