用Python给Verilog设计自仿(11):协程、阻塞勘误及AXIS开源验证剖析

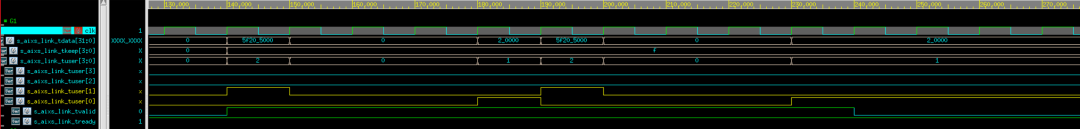

前言 在上一篇文章中,我们提到相同协程是阻塞的,不同协程是并发的这一说法。然而,这种理解存在偏差,所以第一个现象并不像我们之前想象的那样。今天,我们将专门梳理协程的概念,深入剖析其本质,以纠正上次关于协程与阻塞的说明。 案例说明 下面我将介绍一种非常典型的现象 for i in range(2): await device_to_host_source.send(frame) for

关于「AXI」的技术文章、设计资料与工程师讨论,持续更新。

前言 在上一篇文章中,我们提到相同协程是阻塞的,不同协程是并发的这一说法。然而,这种理解存在偏差,所以第一个现象并不像我们之前想象的那样。今天,我们将专门梳理协程的概念,深入剖析其本质,以纠正上次关于协程与阻塞的说明。 案例说明 下面我将介绍一种非常典型的现象 for i in range(2): await device_to_host_source.send(frame) for

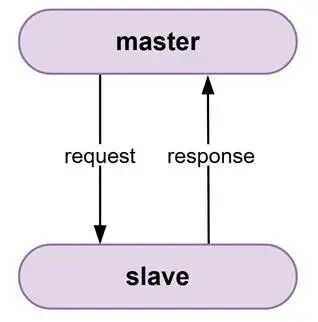

1 前言 2 模型介绍 如图1为该死锁模型,看起来是不是很简单,参与者就两个:master和slave。Master发起request需要slave做一些事情,slave反馈回response告知master这件事做的怎么样了。但就是这样简单的通信场景没有配合好就暗含死锁风险。 图1 死锁模型 为什么这个模型会死锁呢?比如master和slave都比较拧巴,master一定要让slave做某件事