用Python给Verilog设计自仿(一):Cocotb环境初探

1前言 很多FPGA/IC工程师擅长设计,但在仿真方面较为薄弱。我认为主要问题在于,完整的仿真实现学习成本较高,如学习UVM需要掌握大量新的内容。而单纯使用Verilog自仿又难以满足需求,以报文仿真为例,我们需要解析报文,若仅依赖Verilog自仿,就相当于要自己编写一个报文解析模块,工作量非常庞大。而Python在数据处理方面则更加高效,如果加以利用,完全可以快速构建一个完整的仿真模型。Coc

关于「Cocotb」的技术文章、设计资料与工程师讨论,持续更新。

1前言 很多FPGA/IC工程师擅长设计,但在仿真方面较为薄弱。我认为主要问题在于,完整的仿真实现学习成本较高,如学习UVM需要掌握大量新的内容。而单纯使用Verilog自仿又难以满足需求,以报文仿真为例,我们需要解析报文,若仅依赖Verilog自仿,就相当于要自己编写一个报文解析模块,工作量非常庞大。而Python在数据处理方面则更加高效,如果加以利用,完全可以快速构建一个完整的仿真模型。Coc

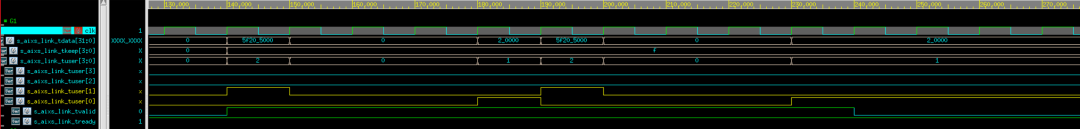

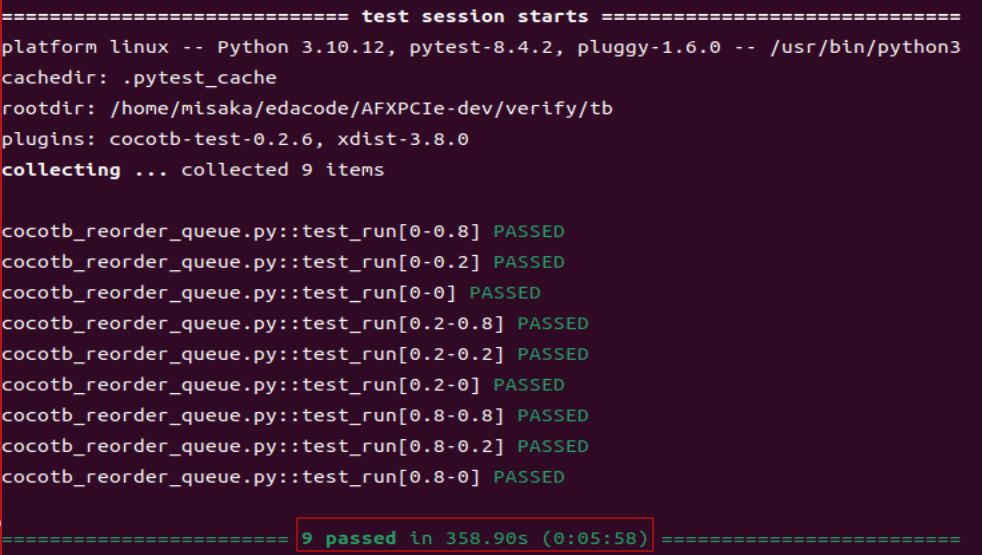

前言 在上一篇文章中,我们提到相同协程是阻塞的,不同协程是并发的这一说法。然而,这种理解存在偏差,所以第一个现象并不像我们之前想象的那样。今天,我们将专门梳理协程的概念,深入剖析其本质,以纠正上次关于协程与阻塞的说明。 案例说明 下面我将介绍一种非常典型的现象 for i in range(2): await device_to_host_source.send(frame) for

前言 在使用 cocotb 编写测试时,很多人可能都会遇到一些让人困惑的现象:比如说,你明明在发送一帧完整数据之后,加了 await RisingEdge(clk) 想等待 5 个周期再发下一帧,但在波形上却发现帧与帧之间并没有间隔;或者你在别的地方加了 Timer 也没起作用更甚至cocotb直接卡住不动了;又或者明明指定了发包数,却提前结束了。 这些现象的背后,其实不是 cocotb 出了问题

对于许多FPGA/IC工程师而言,设计实现游刃有余,验证仿真却常成短板——传统验证方法面临两难困局:学习UVM需投入大量时间成本,而纯Verilog自仿又会陷入重复造轮子的低效循环。以通信协议仿真为例,仅报文解析就需要重写整套解析逻辑,相当于用Verilog再实现一次协议栈,耗时费力。此时,Python的生态优势便锋芒尽显。其丰富的字符串处理库可直接解析报文,配合Cocotb框架,仅需少量Pyth