FPGA漫谈PCI-E:TLP包

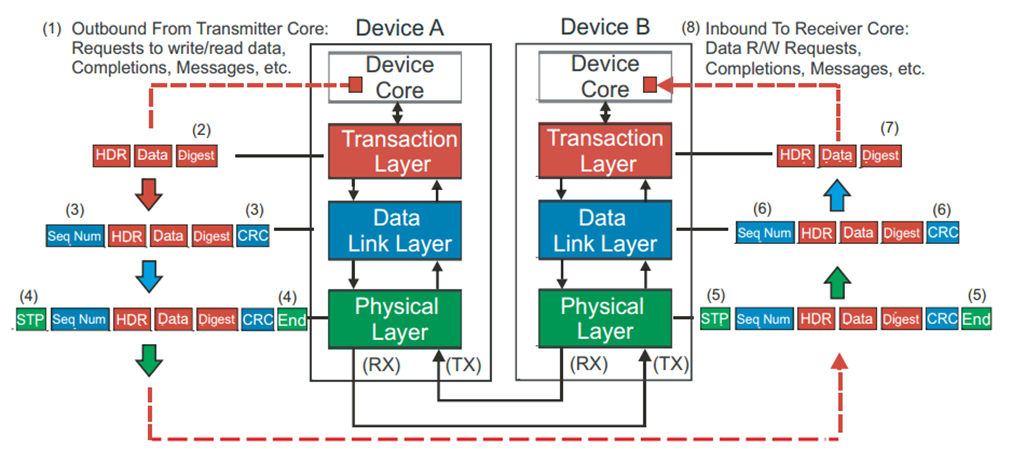

前言 本系列不会从零讲PCIe,也不会照搬规范条款,标准文档已经够厚,这里更像是一份工程师视角下的PCIe手边笔记 , 以更简洁的方式记录PCIe的关键点。 TLP包 由于PCIe-DMA的实现始终在事务层通过TLP包完成,因此深入理解TLP包的构成至关重要。 TLP包所在位置 在PCIe协议的传输层中,TLP包的结构相较于链路层与物理层的报文而言,最为简单清晰。 TLP的结构 TLP的结构

关于「DMA」的技术文章、设计资料与工程师讨论,持续更新。

前言 本系列不会从零讲PCIe,也不会照搬规范条款,标准文档已经够厚,这里更像是一份工程师视角下的PCIe手边笔记 , 以更简洁的方式记录PCIe的关键点。 TLP包 由于PCIe-DMA的实现始终在事务层通过TLP包完成,因此深入理解TLP包的构成至关重要。 TLP包所在位置 在PCIe协议的传输层中,TLP包的结构相较于链路层与物理层的报文而言,最为简单清晰。 TLP的结构 TLP的结构

经过前面的折腾,设计好了自己的测试开发板 搭建好了开发环境, 然后正式开始进行功能测试了,测试顺序先从简单的开始吧,一步一步来 前言 1、ADC采样示例测试 1.1 DMA连续采样 1.2 单次采样 1.3 测试源码 2、 ESP32-C3 ADC相关介绍 2.1 实际电压的计算 2.2 连续采样步骤 2.3 单步采样步骤 2.4 ADC使用注意事项 前

前言 开源 AFX-SATA-DMA 控制器:高速存储接口的完整实现(附源码) SATA 的开源并不是我的主要目的。这个项目最初的出发点,其实是想借此验证和实践 cocotb 仿真的完整流程,以及构建一套自主可控的 FPGA 开发工具链。可以说,是为了这点醋,才包了这顿饺子。不过既然 SATA 协议都已经实现出来了,索性就把它开源出来。开源的好处是双向的:对大家来说,可以借此深入学习SATA 协议

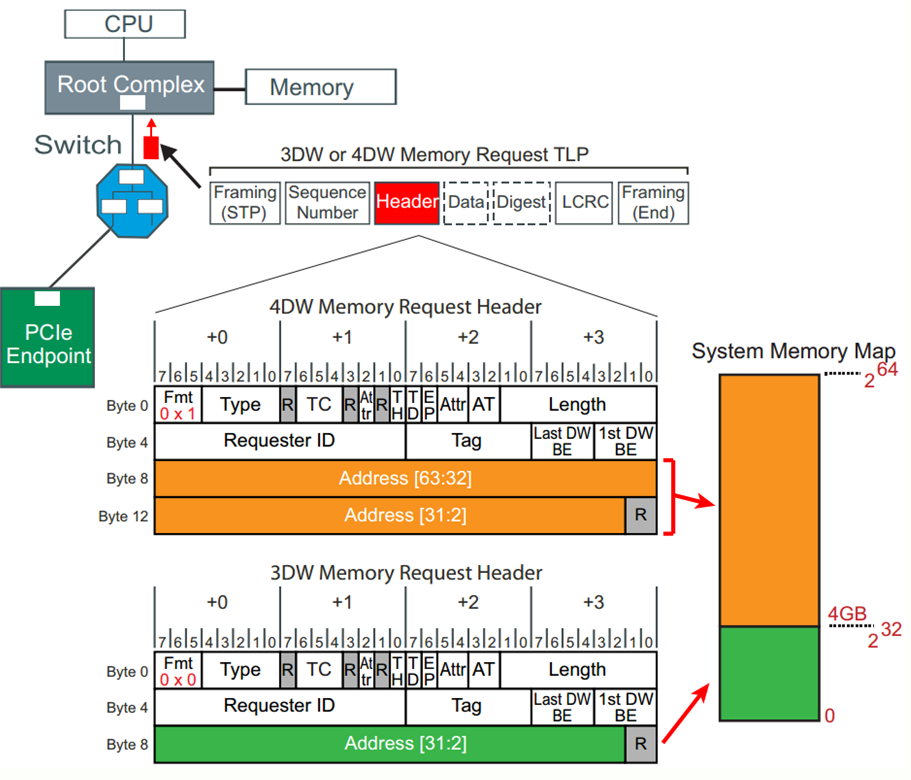

DMA与MMIO的读写操作均通过三种基本报文实现:MWr(写请求)、MRd(读请求)和CPLD(完成带数据)。 MMIO的读写机制较为简单:写操作直接发起一次MWr请求;读操作则先发起MRd请求,然后等待一个包含数据的CPLD报文作为响应。 相比之下,DMA的读写行为则复杂得多,但其原理依然可以理解。 Request Memory请求包在传输时需遵循以下规范 4KB 地址边界限制 Memor