从 IP 开始,学习数字逻辑:FIFO 篇(下)

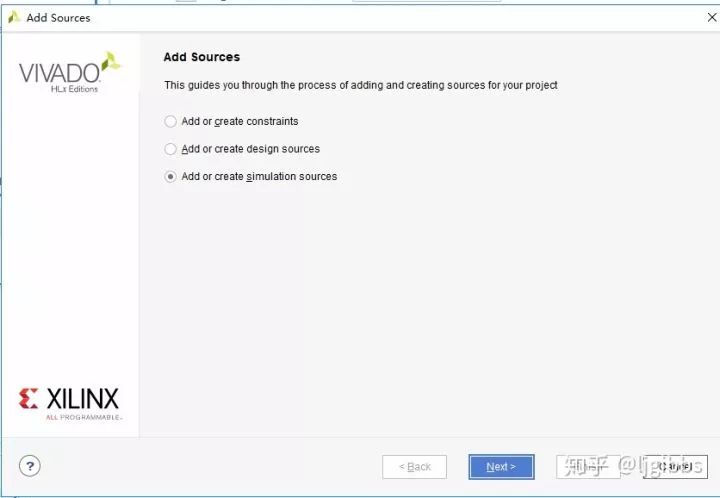

为 FIFO 编写 testbench 在使用各种手段测试我们的 FIFO ip 之前,我们首先得写一个 testbench。testbench 是什么,Vivado 会告诉你就是一个普通的 v 文件。在这个 v 文件中,实例化需要被测试的模块,然后写一些激励语句: FIFO,好好干,年底升职加薪。。 激励是不可能这么激励的。激励语句指的是为待测试模块的输入端口信号指定电平状态

关于「FIFO」的技术文章、设计资料与工程师讨论,持续更新。

为 FIFO 编写 testbench 在使用各种手段测试我们的 FIFO ip 之前,我们首先得写一个 testbench。testbench 是什么,Vivado 会告诉你就是一个普通的 v 文件。在这个 v 文件中,实例化需要被测试的模块,然后写一些激励语句: FIFO,好好干,年底升职加薪。。 激励是不可能这么激励的。激励语句指的是为待测试模块的输入端口信号指定电平状态

学生期间,做的设计比较小或者偏向 demo 类型,那么 ip 核是会占据设计的很大一部分。但使用 ip 核本身对学习者来说就很有意义。通过 ip 的使用,会了解一个工程如何组织,如何阅读手册,如何通过仿真结果优化修改自己的设计。本系列就会通过使用一系列的基础 ip,讨论如何组织工程,阅读手册,编写基础的粘合逻辑,testbench 以及功能仿真。 使用 ip 对于数字逻辑方面的工

管道(pipe)应用的一大局限是没有名字,只能用于具有亲缘关系进程之间的通信。而命名管道,也称FIFO,实质是一种文件类型,通过FIFO可以用于任何两个进程间的通信。 命名管道的创建 命令方式 在shell中可以使用mkfifo命令创建一个命名管道,格式为: mkfifo [option] name 其中option选项用于选择创建FIFO的模式,使用形式为-m mode,mode为八进制模式,创

本期文章目录 ZYNQ | 学习路线 ZYNQ 点击阅读 ZYNQ 关于Timing Exception Design #约束 点击阅读 码农的假期 Verilog有什么奇技淫巧? Verilog #ASIC 点击阅读 硅农 基于CORDIC的加减乘除及三角函数实现 CORDIC 点击阅读 探究FPGA 读书笔记 | Design Rot -1 IC设计 点击阅读 icsoc 构建ic知识体系

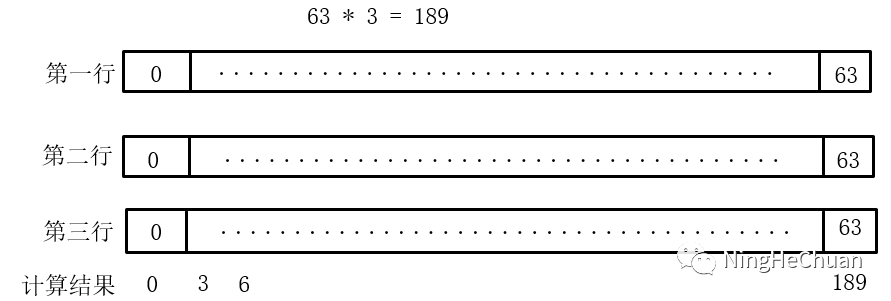

实验:FPGA**计算3**行同列数据之和 实验要求:PC机通过串口发送3行数据(一行有56个数据,3行共有56*3=168个数据)给FPGA,FPGA计算3行同一列数据的和,并将结果通过串口返回给上位机。 实现方法:使用两个FIFO IP Core,将串口接收到的数据进行缓存,当第一个FIFO1的数据存满后,将FIFO1的数据读出来给FIFO2,当FIFO2的数据存满时,当前两个FIFO的数据和