从 IP 开始,学习数字逻辑:FIFO 篇(下)

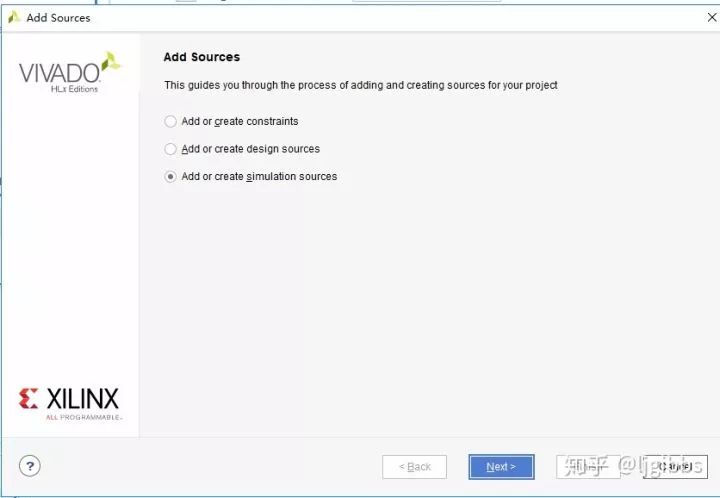

为 FIFO 编写 testbench 在使用各种手段测试我们的 FIFO ip 之前,我们首先得写一个 testbench。testbench 是什么,Vivado 会告诉你就是一个普通的 v 文件。在这个 v 文件中,实例化需要被测试的模块,然后写一些激励语句: FIFO,好好干,年底升职加薪。。 激励是不可能这么激励的。激励语句指的是为待测试模块的输入端口信号指定电平状态

关于「Vivado」的技术文章、设计资料与工程师讨论,持续更新。

为 FIFO 编写 testbench 在使用各种手段测试我们的 FIFO ip 之前,我们首先得写一个 testbench。testbench 是什么,Vivado 会告诉你就是一个普通的 v 文件。在这个 v 文件中,实例化需要被测试的模块,然后写一些激励语句: FIFO,好好干,年底升职加薪。。 激励是不可能这么激励的。激励语句指的是为待测试模块的输入端口信号指定电平状态

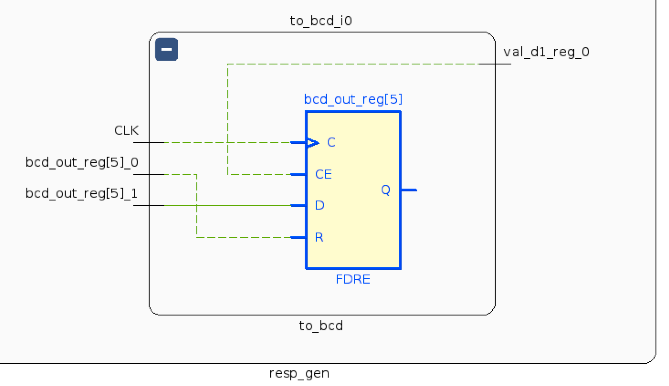

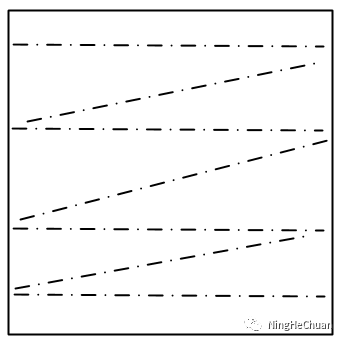

前言:本文章为FPGA问答系列,我们会定期整理FPGA交流群(包括其他FPGA博主的群)里面有价值的问题,并汇总成文章,如果问题多的话就每周整理一期,如果问题少就每两周整理一期,一方面是希望能帮到不经常看群消息的小伙伴,另一方面也算是我们的技术积累。 Q:Vivado Schematic中的实线和虚线有什么区别? A:以下图为例:下面的schematic种,有实线也有虚线 image-20230

学生期间,做的设计比较小或者偏向 demo 类型,那么 ip 核是会占据设计的很大一部分。但使用 ip 核本身对学习者来说就很有意义。通过 ip 的使用,会了解一个工程如何组织,如何阅读手册,如何通过仿真结果优化修改自己的设计。本系列就会通过使用一系列的基础 ip,讨论如何组织工程,阅读手册,编写基础的粘合逻辑,testbench 以及功能仿真。 使用 ip 对于数字逻辑方面的工

之前学习了半年的图像处理,所以计划将自己学过的几个图像处理的基础算法,做过的设计记录下来,在OpenHW论坛上发表,计划是这样的,用VGA做显示,使用PC端上位机通过串口发送一幅图片数据到FPGA开发板,FPGA接收数据并做处理最终发送给VGA显示屏显示,计划要写的算法有彩色图像转灰度、均值/中值滤波、Sobel边缘检测等。那么现在这是第一篇,先来写VGA显示的驱动、以及将一幅图片显示到VGA显示

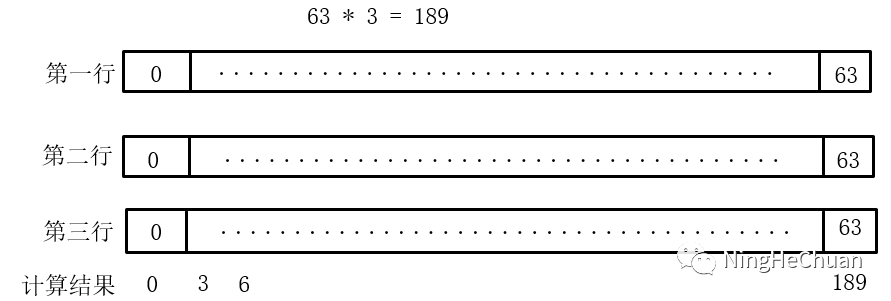

实验:FPGA**计算3**行同列数据之和 实验要求:PC机通过串口发送3行数据(一行有56个数据,3行共有56*3=168个数据)给FPGA,FPGA计算3行同一列数据的和,并将结果通过串口返回给上位机。 实现方法:使用两个FIFO IP Core,将串口接收到的数据进行缓存,当第一个FIFO1的数据存满后,将FIFO1的数据读出来给FIFO2,当FIFO2的数据存满时,当前两个FIFO的数据和

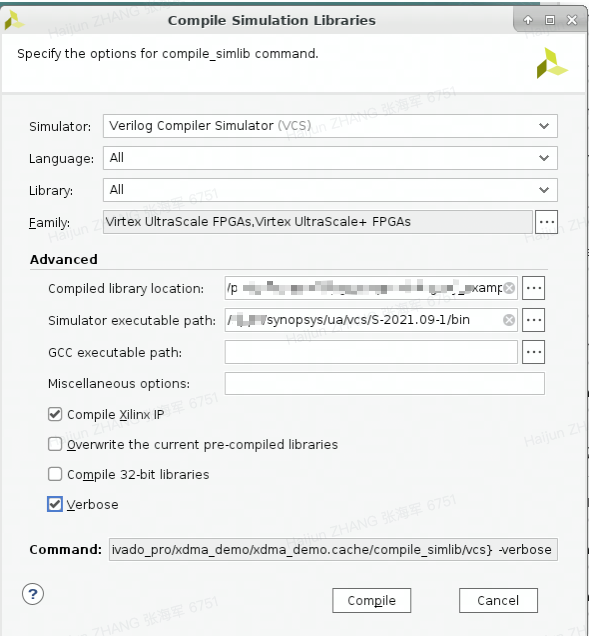

VCS+Verdi的组合是EDA仿真中必备神器,以前只会用Vivado自带的仿真器或者Modelsim来进行仿真,但用了VCS+Verdi后,就不想再用vivado自带的仿真器了,Verdi看波形、追信号实在是快太多了。 首先就是要用VCS把xilinx的仿真库都编译一遍,这样才能用vcs进行仿真。 打开vivado,在Tools下面有个Compile Simulation Libraries.

ZYNQ算是Xilinx的一款比较高端的板子了,上面有以太网接口、USB2.0/OTG、HDMI双向接口,SD卡槽,而且板子内部还嵌入了ARM,上面可以跑linux,价格也不菲。刚开始查了一下手册了解到板子晶振是50Mhz,然后试了半天就是没有把VGA驱动起来,后来在仔细查了一下手册,这款板子在某种情况下板子提供的是125Mhz引脚为L16,然而我不知道怎么用50Mhz,那就直接