case里边居然还有个inside

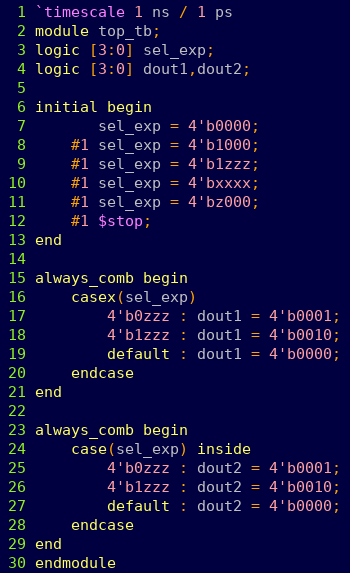

在SystemVerilog中,经常会用到casex和casez等多分支选择结构,用以忽略case_expression与case_item中x和z的比较,相关内容详见《硅芯思见:【80】casez和casex谁是谁》,但本文介绍SystemVerilog引入的“case inside”结构(推荐使用)与casex和casez还是有一定的区别的,这主要是因为casex和casez会将x或者z作为不

关于「SystemVerilog」的技术文章、设计资料与工程师讨论,持续更新。

在SystemVerilog中,经常会用到casex和casez等多分支选择结构,用以忽略case_expression与case_item中x和z的比较,相关内容详见《硅芯思见:【80】casez和casex谁是谁》,但本文介绍SystemVerilog引入的“case inside”结构(推荐使用)与casex和casez还是有一定的区别的,这主要是因为casex和casez会将x或者z作为不

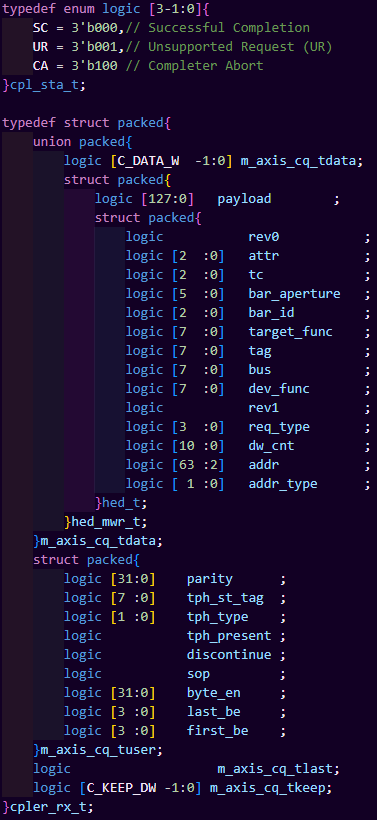

• 前言 • SV的优劣 • 最方便的信号类型(logic) • 定义复杂信号的优雅方式(struct) • 最省心的状态机利器(enum) • 提前发现多驱 • 让数据结构更清爽的秘诀(typedef) • 最常用的批量信号写法(packed array) • 模块通信的终极级懒人包(interface) • 最优雅的头文件(package) • 最懂工程师意图的过程块定义(always)