在SystemVerilog中,经常会用到casex和casez等多分支选择结构,用以忽略case_expression与case_item中x和z的比较,相关内容详见《硅芯思见:【80】casez和casex谁是谁》,但本文介绍SystemVerilog引入的“case inside”结构(推荐使用)与casex和casez还是有一定的区别的,这主要是因为casex和casez会将x或者z作为不关心态(don’t care)进行处理,即不会将case表达式和case分支项表达式中对应的包含x或者z的位进行比较。而“case inside”则不会将case表达式中的x或者z作为不关心态(don’t care)进行处理,但case分支项表达式中对应的包含x或者z仍会作为不关心态(don’t care)。所以,在处理相同的case表达式时,两者变现出的结果可能会不同。

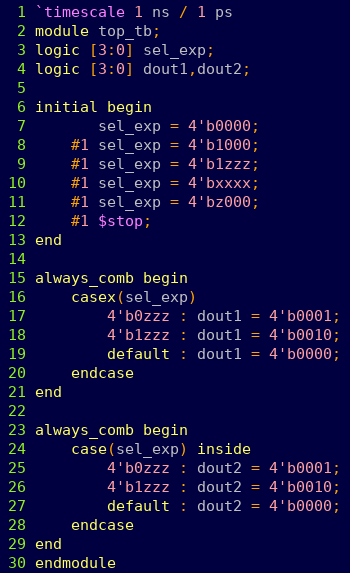

【示例】

【仿真结果】

示例中,当sel_exp为4’b0000时,“casex”结构和“case inside”结果的输出都是1,“casex”结构和“case inside”结构在此处输出1是因为case分支项表达式将值为“z”的位都视为不关心态(don’t care),也就是为“z”的位不与case表达式对应位进行比较;

当sel_exp为4’b1000时,“casex”结构和“case inside”结果的输出都是2,输出该结果原因同上;

当sel_exp为4’b1zzz时,“casex”结构和“case inside”结果的输出仍是2,但是这里需要注意,两者匹配的原因是有差异的,“casex”结构在此处输出2是因为case表达式和case分支项表达式将值为“z”的位都视为不关心态(don’t care),而“case inside”结构则是对case表达式和case分支项表达式进行逐位比较所得;

当sel_exp为4’bxxxx时,“casex”结构输出为1,而“case inside”结果的输出都是0,这是因为“casex”结构认为此时case表达式的所有位均为不关心态(don’t care),也就是可以与任何case分支项表达式匹配,但是根据优先级会与第一个分支匹配输出,所以此时输出结果为1。但是“case inside”此时不会认为case表达式的所有位为不关心态,会将其与case分支项表达式逐位比较,因为当前所有分支项只有没有可完全匹配的,所以此时输出为default分支。

通过仿真结果可以看到,case表达式中包含x或者z时,匹配的结果可能与我们期望的不一致,特别是在仿真的过程中,如果电路中出现不期望的x或者z,此时使用“casex”或者“casez”结构可能就会隐藏这种错误,为此,在SystemVerilog中引入了“case inside”结构,“case inside”在将case表达式与case分支表达式进行比较时会将case表达式中的x和z严格与case分支项表达式进行比较,将case分支项表达式中的x和z仍然视为不关心态,即其比较按照比较操作符“==?”进行比较,通过使用case-inside结构可以有效地发现电路中异常x或者z。

这里需要注意“==?”的真值表如下:

| ==? | 右0 | 右1 | 右z | 右x |

|---|---|---|---|---|

| 左0 | 1 | 0 | 1 | 1 |

| 左1 | 0 | 1 | 1 | 1 |

| 左z | x | x | 1 | 1 |

| 左x | x | x | 1 | 1 |

可见,“case inside”是一种单向(one-way)的且非对称(asymmetric)的遮掩,仅对case分支项表达式中的x、z和?进行遮掩,不对case表达式中的x、z和?进行遮掩,因此建议在在可综合的RTL代码中使用“case inside”代替“casex”或者“casez”来预防设计问题,避免匹配出错等问题的出现,确保电路的行为尽可能与期望一致。

除此可以用于普通的匹配操作外,“case inside”还可用于范围匹配。例如,

【示例】

【仿真结果】

示例中,当sel_mem的取值为0~3时,输出“RAM Selected!”;当sel_mem的取值为4~5时,输出“RO Selected!”;当sel_mem的取值为6~7时,输出“FLASH Selected!”。可见,通过该方法可以方便的构建一定范围的选择,而一般的case结构,则需要case表达式与case分支项表达式需要精确匹配,很难快捷的实现这种范围式的匹配。因为分支项表达式中可以使用z、x和?,所以,在使用这种范围匹配时可以结合分支项表达式中的z、x和?进行一些特定范围的匹配操作。

总之,“case inside” 对比传统的“casex”和“casez”,可以减少因模糊处理未知数而潜在引入的缺陷,是一种更安全可靠的设计方案,有助于在设计阶段尽早发现问题,从而提高整体设计质量,比较适用于协议处理、状态机设计、地址译码等需要复杂条件匹配的场景。

评论区

登录后即可参与讨论

立即登录