MLX90640热成像与FPGA结合:VGA输出详解

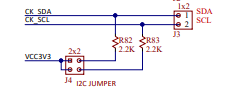

来源:OpenFPGA;;作者:碎碎思 在本文中,我们将介绍如何构建带有VGA输出的低分辨率热成像。该解决方案基于Melexis MLX90640红外阵列、FPGA S7 50开发板(AMD-Xilinx Spartan-7 FPGA,带VGA输出)。 Sparkfun Melexis MLX90640 红

纳米网半导体产业频道 — 提供半导体产业领域最新资讯、技术文章和行业动态。

来源:OpenFPGA;;作者:碎碎思 在本文中,我们将介绍如何构建带有VGA输出的低分辨率热成像。该解决方案基于Melexis MLX90640红外阵列、FPGA S7 50开发板(AMD-Xilinx Spartan-7 FPGA,带VGA输出)。 Sparkfun Melexis MLX90640 红

在边缘智能日益复杂的应用场景中,系统协同能力已成为性能的新衡量维度。 ALINX 近期发布的 BZ10 异构多处理采集计算开发板在这方面的表现十分亮眼。 ( AMD Zynq UltraScale+ ZU7EV 开发平台 BZ10) 一颗芯片,融合多种算力架构 ZU7EV=FPGA+ARM+G

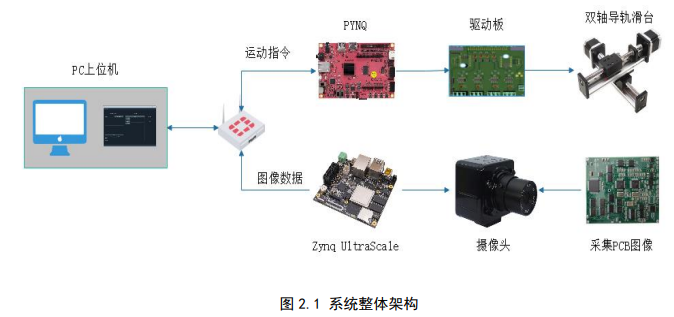

第一部分 设计概述 1.1 设计目的 作为电子产品最重要的组成部分,印刷电路板(PCB)的设计日趋复杂和器件尺寸的缩小,促使对 SMT 可靠性提出了更高的要求。因此对于 SMT 电路板的检测研究具有深刻的现实意义和经济价值。 在 SMT 工艺中,贴片器件焊点的好坏会严重影响 PCB 板的质量。轻则会导致

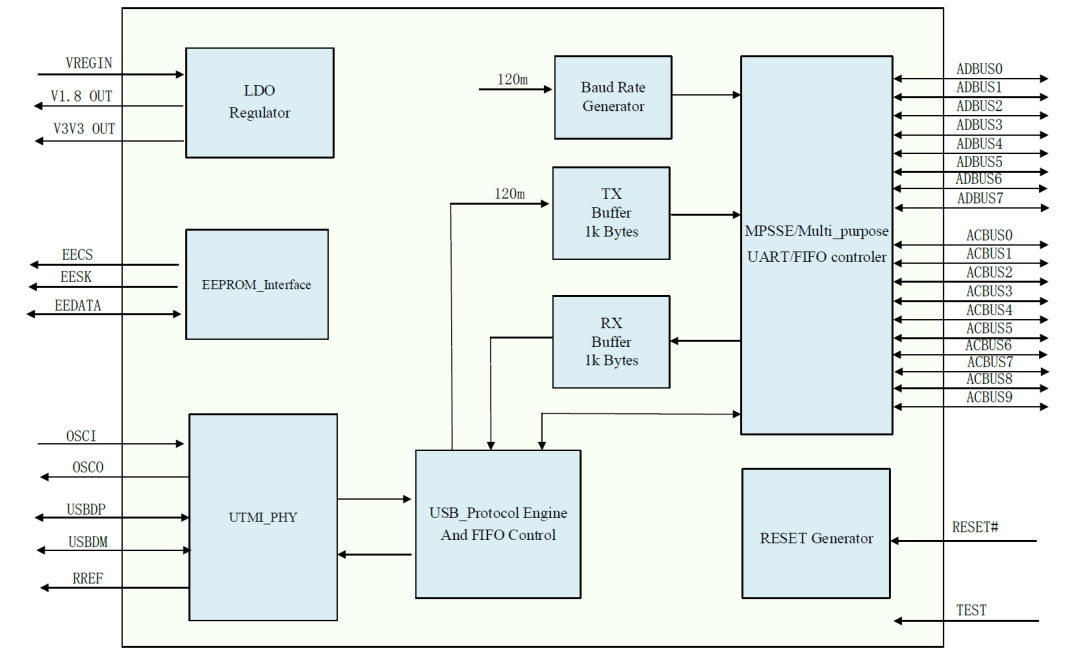

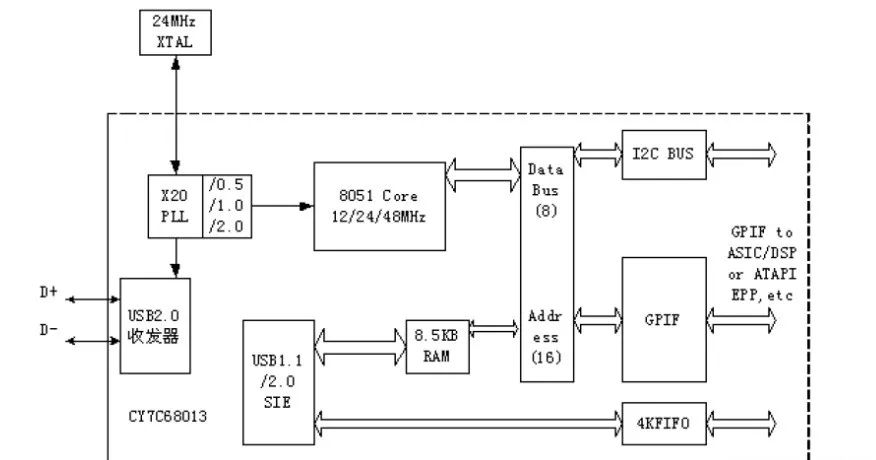

USB英文全称 Universal Serial Bus,即通用串行总线,是一个外部总线标准,用于规范电脑与外部设备的连接和通讯。 FTDI 公司的USB2.0 芯片FT232H 进行USB 通信 FH232H芯片在内部不仅完成了USB 硬件接口差分电平转换,还封装了USB 的相关协议,留出数据交互接口

近日,由国产FPGA领军企业易灵思与南京大学集成电路学院联合举办的“深度学习与硬件加速”暑期课程圆满结课。本次课程为期5天(7月7日至7月11日),面向大三本科生,旨在通过理论与实践结合的方式,帮助学生掌握FPGA硬件加速与TinyML的前沿技术,培养集成电路与人工智能交叉领域的创新人才。 课程亮点:理论与实践

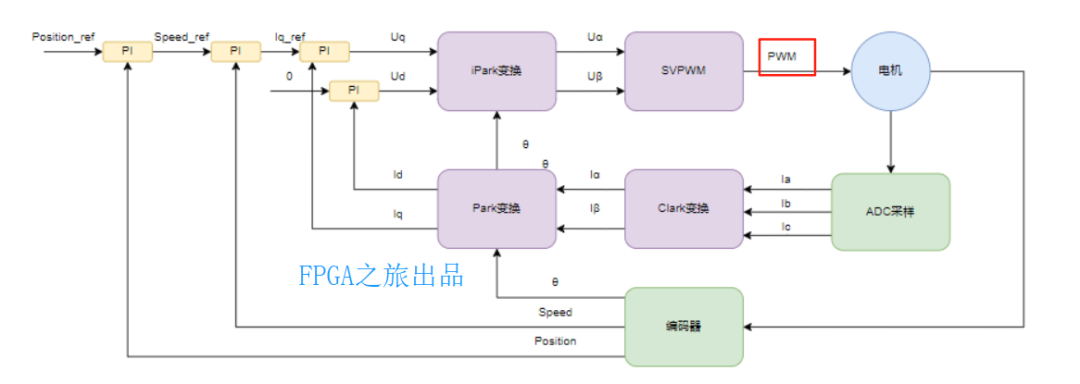

一.简介 哈喽,大家好,从今天开始正式带领大家从零到一,在FPGA平台上实现FOC算法,整个算法的框架如下图所示,如果大家对算法的原理不是特别清楚的话,可以先去百度上学习一下,本教程着重介绍实现过程,弱化原理的介绍。那么本文将从PWM模块开始进入FOC算法中去。 二. PWM模块设计 我们知道有些

该公司为关键基础架构提供高性能、高成本效益解决方案,确保无缝过渡到量子安全加密 Sitehop 是一家致力于提高网络安全与性能的网络安全技术公司。其 SAFE 系列产品线包括旨在保护关键网络动态数据安全的硬件强制加密和解密系统。这些系统以其超低时延、高带宽和极低功耗而著称。 Sitehop 的技术能以低时延

1. FFT有什么用? FFT(快速傅里叶变换)是离散傅里叶变换(DFT)的高效实现算法,它的核心作用是快速将信号从时域转换到频域,从而简化信号分析和处理的过程。 自然界的信号(如声音、图像、电磁波等)通常以时域形式存在(即随时间变化的波形),但很多特性(如频率成分、谐波分布)在频域中更易分析 FFT

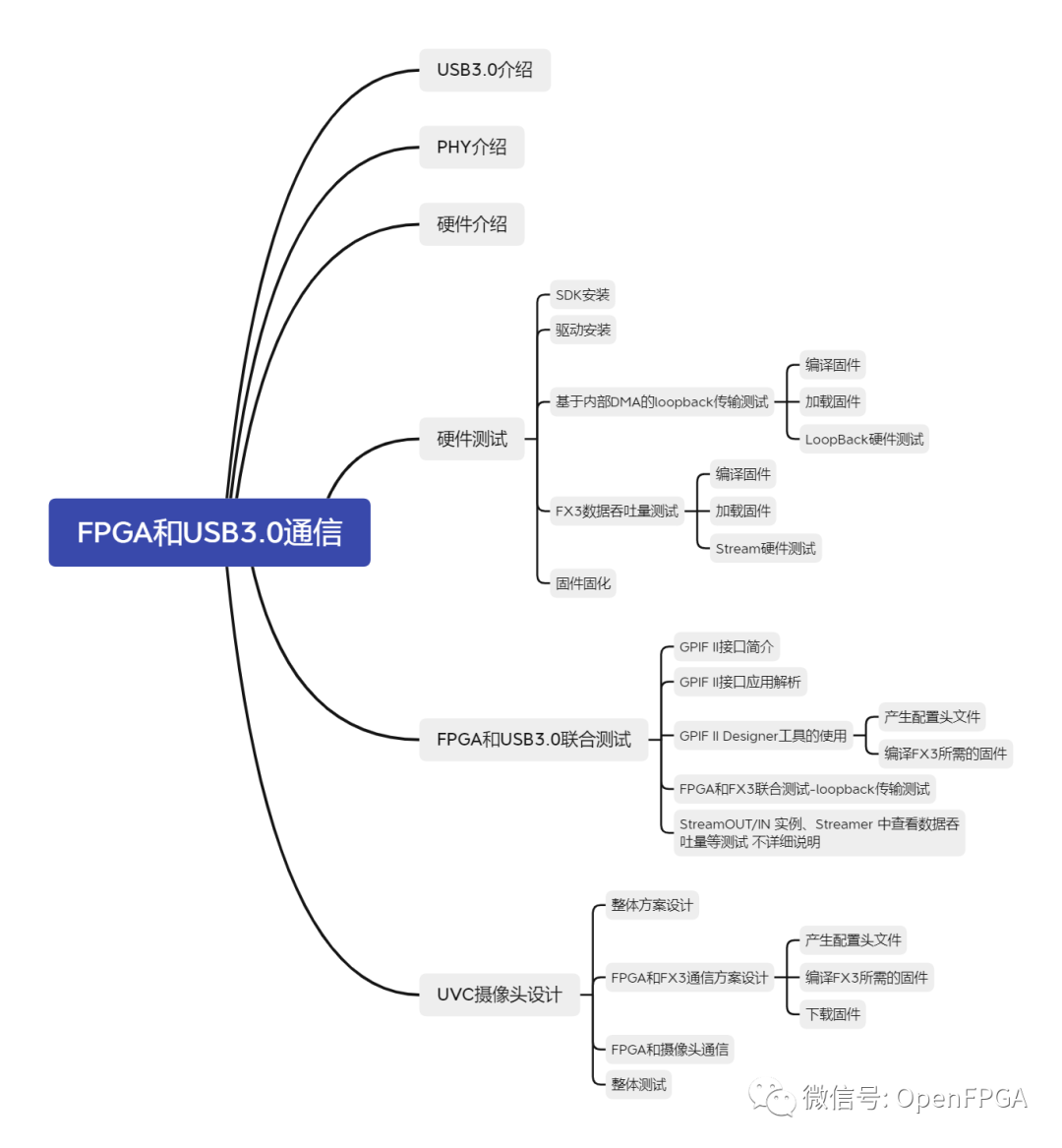

以下文章来源于OpenFPGA,作者碎碎思 FPGA和USB3.0通信-UVC摄像机 本次演示用的是USB3.0芯片-CYPRESS CYUSB3014(下称 FX3),该芯片是标准的USB3.0 PHY,可以大大简化使用USB通信时FPGA的设计,主需要使用状态机进行FIFO的读写控制即可,同时该芯

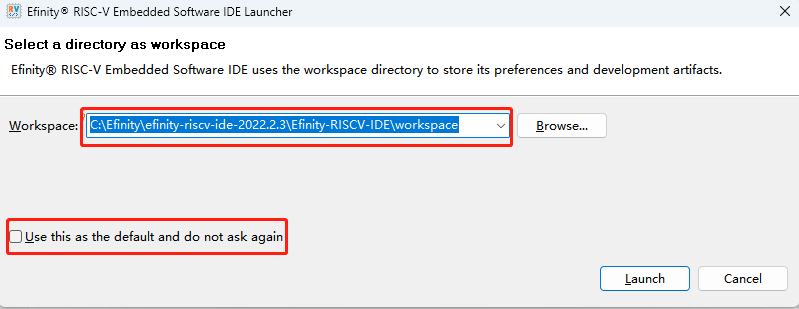

一、Efinity工程 io_memoryClk是与存储器接口共用的时钟,需要连接正确。 UART 由于钛金系列是有片上晶振的,所以有些客户可能会选择片上晶振作为SOC的系统时钟或者选择片上晶振作为PLL的参考时钟,再由该PLL的输出时钟作为SOC的系统时钟,但是由于片上晶振频率偏差比较大

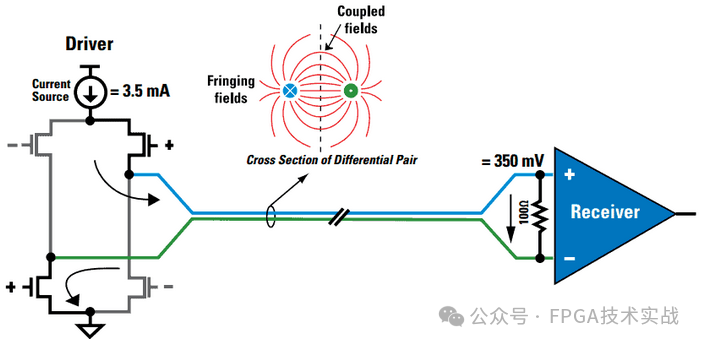

来源:FPGA技术实战 引言:本文描述了ADC和FPGA之间LVDS接口设计需要考虑的因素,包括LVDS数据标准、LVDS接口数据时序违例解决方法以及硬件设计要点。 1. LVDS简介 1.1 什么是LVDS? LVDS(低压差分信号)标准是业界流行的差分数据传输标准,它是双线、低摆幅差分信号。其优

简介:本文介绍如何利用FPGA和DMA技术处理来自AD9280和AD9708 ADC的数据。首先,探讨了这两种ADC的特点及其与FPGA的接口兼容性。接着,详细说明了使用Xilinx VIVADO环境下DMA IP核来实现高效数据传输的步骤,包括创建项目、配置ADC接口、添加和连接DMA IP核、设计控制逻辑、生成

近日,上海松江举办的“2025中国科创领袖大会暨科创板开市六周年峰会”上,“科创板开市六周年评选”榜单揭晓,安路科技凭借在FPGA领域的持续突破与创新成果,荣膺“2025最具创新力科创板上市公司”称号。这一殊荣,是对安路科技以创新为引擎,驱动国产FPGA技术自立自强与产业化应用的高度认可。 作为国内FPGA领域

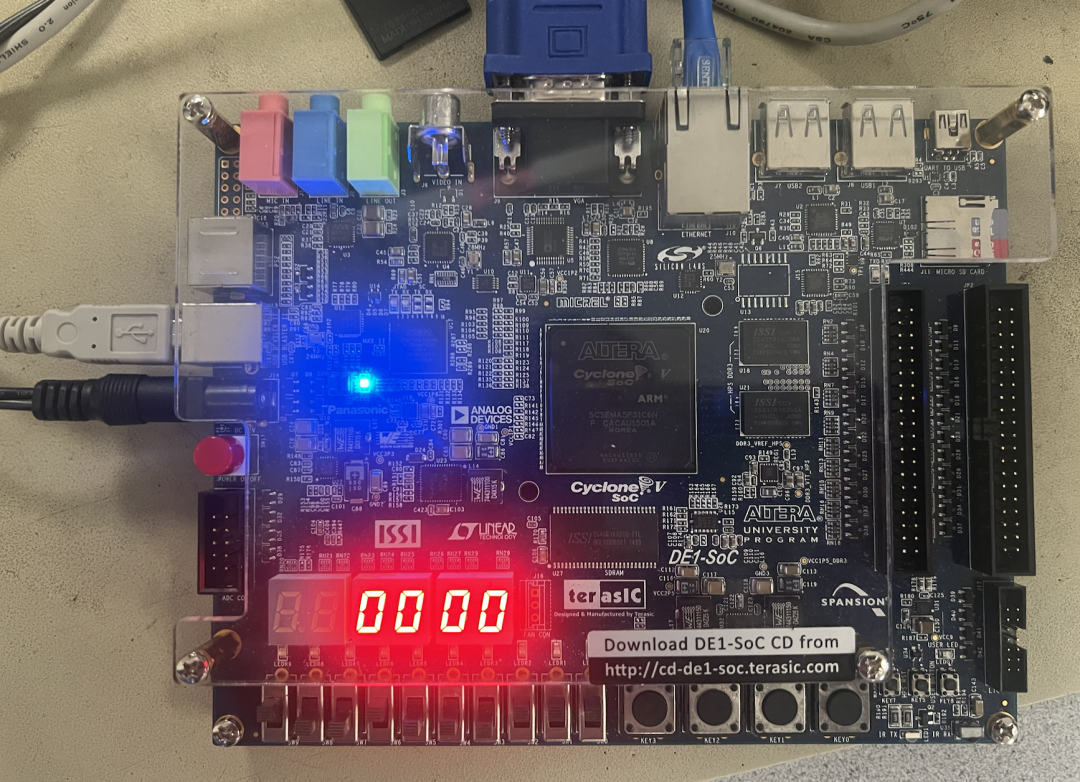

引言 今天继续常春藤名校之一——康奈尔大学的FPGA课程ECE 5760典型案例分享:基于DE1-SOC开发板的太空射击游戏。 1. 项目概述 项目说明 该项目是在DE1-SoC FPGA平台上开发一个名为“太空射击”的实时游戏,利用系统的ARM+FPGA功能,“太空射击”使用内存映射I/O在VGA

USB通信 你也许会有疑问,明明有这么多通信方式和数据传输(SPI、I2C、UART、以太网)为什么偏偏使用USB呢? 原因有很多,如下: 1. 高速数据传输能力 高带宽 :USB接口提供了较高的数据传输速率,尤其是随着USB版本的升级(如USB 3.0及更高版本),其理论速度可达5 Gbps甚至更

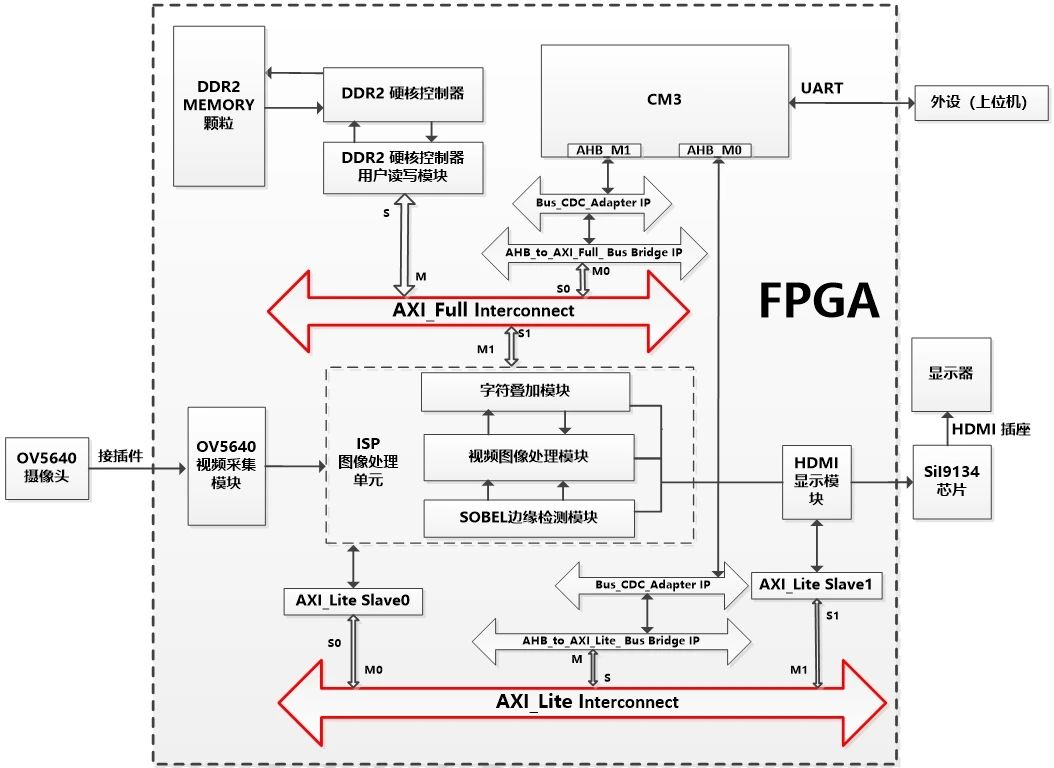

01引言 在图像与视频处理领域,灵活、高效、低延迟的解决方案一直是行业追求的目标。西安智多晶微电子有限公司推出的AXI视频通讯DEMO方案,基于智多晶SA5Z-30-D1-8U213C FPGA器件,通过FPGA逻辑与内嵌CM3硬核的协同工作,结合DDR2高速存储,实现了从图像采集、处理到显示的全流程优化。本文

随着工业自动化、机器人及汽车系统日益精密,经认证的功能安全和实时控制性能已成为不可或缺的必要条件。Altera 和 MathWorks 联袂呈现的双轴电机控制系统,不仅通过 TÜV 认证达到Cat. 3 PLd 安全等级,更以Agilex 5 SoC FPGA为核心载体,巧妙融合基于模型的开发方式与灵活且可移植的安

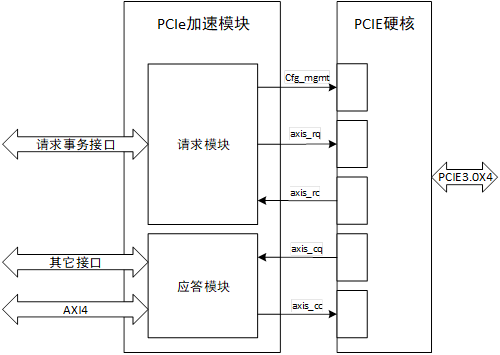

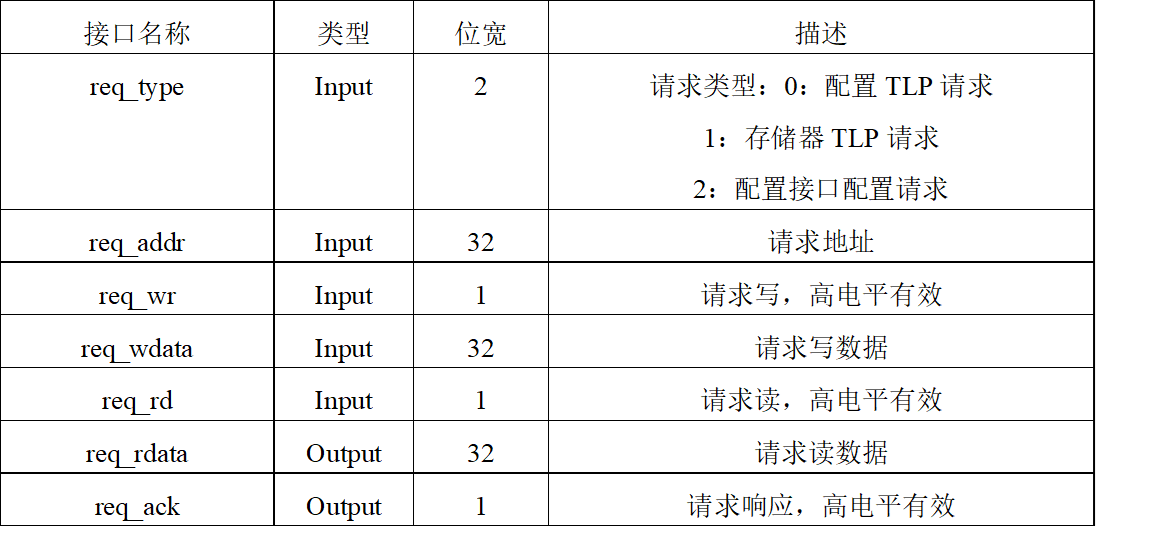

PCIe加速模块负责实现PCIe传输层任务的处理,同时与NVMe层进行任务交互。如图1所示,PCIe加速模块按照请求发起方分为请求模块和应答模块。请求模块负责将内部请求事务转化为配置管理接口信号或axis请求方请求接口信号(axis_rq),以及解析axis请求方完成接口信号(axis_rc);应答模块负责接收ax

请求模块的具体任务是将系统的请求转换成为axis接口形式的TLP或配置管理接口信号。这些请求主要包含初始化配置请求和门铃写请求,初始化配置请求由初始化模块发起,当配置请求的总线号为0时,请求通过Cfg_mgmt接口发送给PCIE硬核,当配置请求的总线号不为0时,请求以PCIe配置请求TLP的格式从axis_rq接口

上篇和中篇,我们介绍了FPGA的四大特点,以及这些特点所带来的市场和应用机会,概述如下:硬件可编程:通信网络,芯片验证等;并行和实时:视频图像处理,AI推理等;高集成度:工业机器人,激光雷达等;新工艺新接口:视频接口,测试测量等。有那么多的机会,FPGA怎么不上天呢?其实FPGA真上天了,在每一台火星车上,几乎都有宇航