高云GW5AT-LV60开发套件:LVDS屏显示与Camera详解

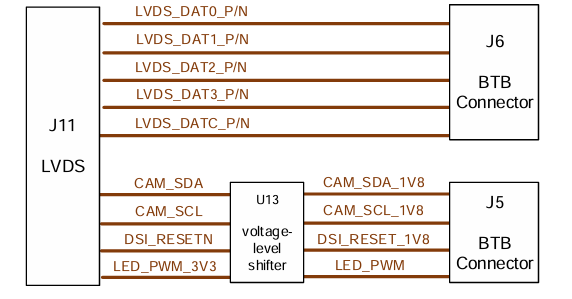

实现将SC130GS采集的黑白图像数据缓存进DDR3,并以1024*600@60的视频时序输出到LVDS 屏幕显示。其中,DDR3工作频率为600MHz,SC130GS输入的图像数据大小为1280*1024,帧率为 60帧,数据格式为RAW10。 底板提供了一个LVDS显示接口,采用40P 0.5mm间距的

纳米网半导体产业频道 — 提供半导体产业领域最新资讯、技术文章和行业动态。

实现将SC130GS采集的黑白图像数据缓存进DDR3,并以1024*600@60的视频时序输出到LVDS 屏幕显示。其中,DDR3工作频率为600MHz,SC130GS输入的图像数据大小为1280*1024,帧率为 60帧,数据格式为RAW10。 底板提供了一个LVDS显示接口,采用40P 0.5mm间距的

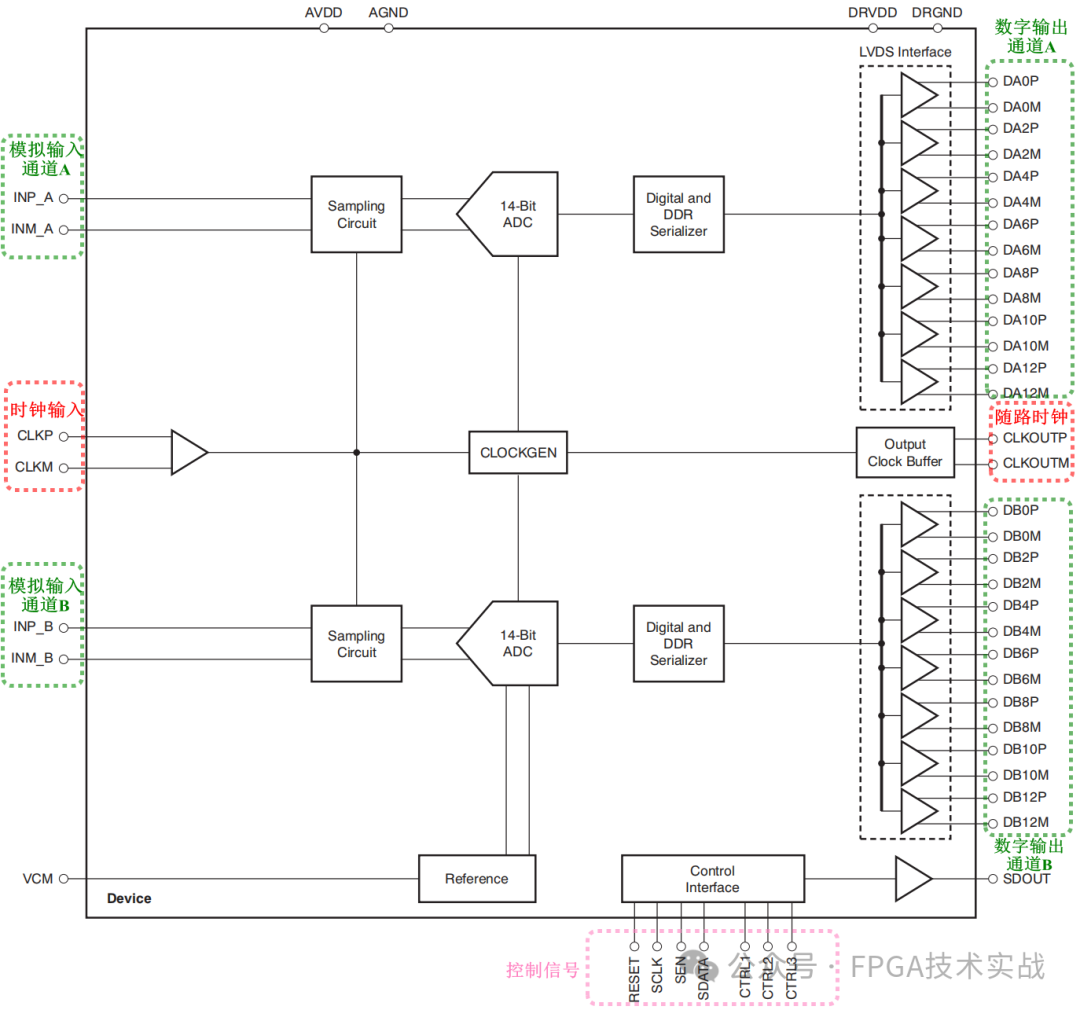

引言:本文以TI的ADS4249(ADC)和DAC3482(DAC)之间的接口为例,介绍Altera FPGA与ADC/DAC之间的DDR LVDS接口设计以及时序约束详细设计。本文介绍的实例可方便扩展到具有类似接口格式的其他高速数据转换器设计。 1.概述 ADS4249是一款双通道、14位、250MSPS

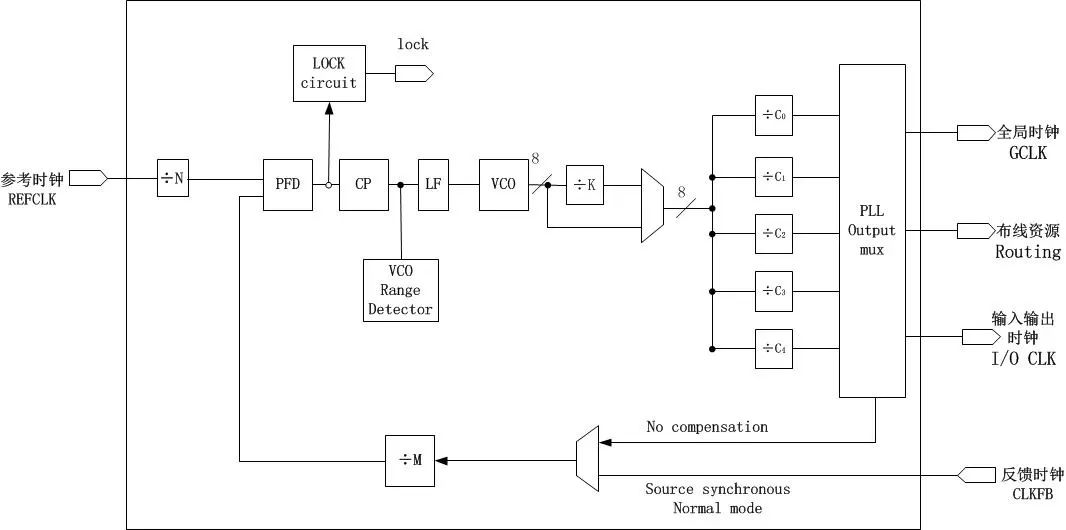

No.1引言 随着现代电子系统的不断发展,时钟管理成为影响系统性能、稳定性和电磁兼容性(EMI)的关键因素之一。在FPGA设计中,PLL因其高精度、灵活性和可编程性而得到广泛应用,本文将深入探讨PLL技术在FPGA中的动态调频与展频功能应用。 No.2PLL技术基础 PLL(Phase-Locked L

AI 正在向边缘迁移 从聊天机器人、内容生成到高级数据分析,AI 已无处不在。过去,大多数 AI 处理都在云端完成。然而,随着模型功能日益强大以及对实时洞察的需求持续增长,AI 正在向边缘转移。智能摄像头和传感器中的卷积神经网络 (CNN) 已印证这一趋势。 但面对大语言模型 (LLM) 等新一代 AI 技术,

电子发烧友网报道(文/黄晶晶)赛灵思(Xilinx)推出的第一款FPGA芯片XC2064于1985年6月问世,它有600个门,64个可配置逻辑块,运行频率为70MHz。这款现场可编程门阵列FPGA使得工程师能够灵活地自定义芯片功能,而无需等待芯片从晶圆厂制造返回。它大大提升了芯片的开发速度,缩短了产品上市时间。AM

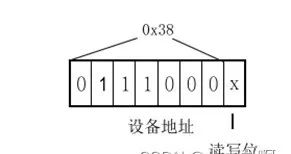

概念 传感器输出经过标定的数字信号输出,通过标准的I2C接口传输数据; 相对湿度的分辨率在0.024%RH,工作范围为0~100%RH; 温度值的分辨率在0.01℃,工作范围为-40~85℃; AHT10的供电范围为1.8~3.6V,推荐使用3.3V供电; 接口包含了完全静态逻辑,因而不存在最小

近日,被誉为 “全球移动通信行业发展风向标” 的 2025世界移动通信大会(MWC上海)在上海新国际博览中心圆满落幕。本届大会以 “开启智能互联新纪元” 为主题,吸引全球创新企业及政策制定者齐聚。紫光同创是唯一一家亮相本次大会的国产FPGA厂商,携手多家合作伙伴及终端客户,向全球科技先锋们多层次地展示公司在通信领域

01Veloce proFPGA Veloce proFPGA 平台提供三类主板:Uno、Duo 和 Quad。这些主板支持轻松插入和混用不同类型的现场可编程门阵列 (FPGA) 模块以及外围存储器和协议接口板。作为使用案例的一个例子,工程师可以从 proFPGA Uno 系统开始进行 IP 或子片上系统 (S

近日,“2025智多晶FPGA技术研讨会”在武汉成功举办。本次交流会以“智绘新篇 晶质领航”为主题,智多晶专业技术团队在会上揭晓了公司匠心打造的多款FPGA芯片新产品、多项新应用方案。 会议期间,数十名专业观众同智多晶专业技术团队进行深度交流与讨论,不断激发和碰撞出新的火花。而在Demo展台周围,参观的人流更是

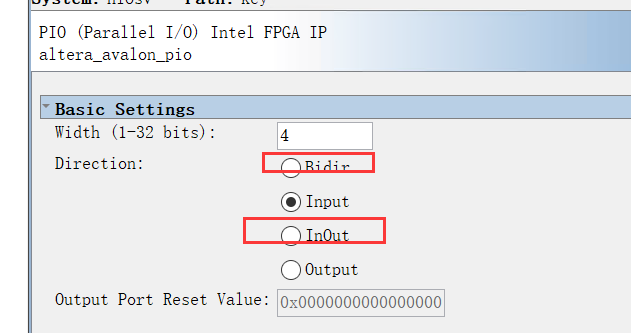

PIO IP是FPGA 设计中比较简单常用的IP, 当设置PIO IP的Direction的时候,可以看到有如下4个选项: Input代表这组IO是输入引脚,Output代表这组IO是输出引脚,这些很好理解,但Bidir和InOut都表示双向的意思,它们有什么区别吗? 参考28.4.1.2. Dire

本文作者:AMD 工程师 Sandy Macnamara 本文讲述了AMD UltraScale /UltraScale+ FPGA 原生模式下,异步模式与同步模式的对比及其对时钟设置的影响。 在 UltraScale/UltraScale+ 中引入了 RXTX_BITSLICE。该原语用于捕获和接收 XP

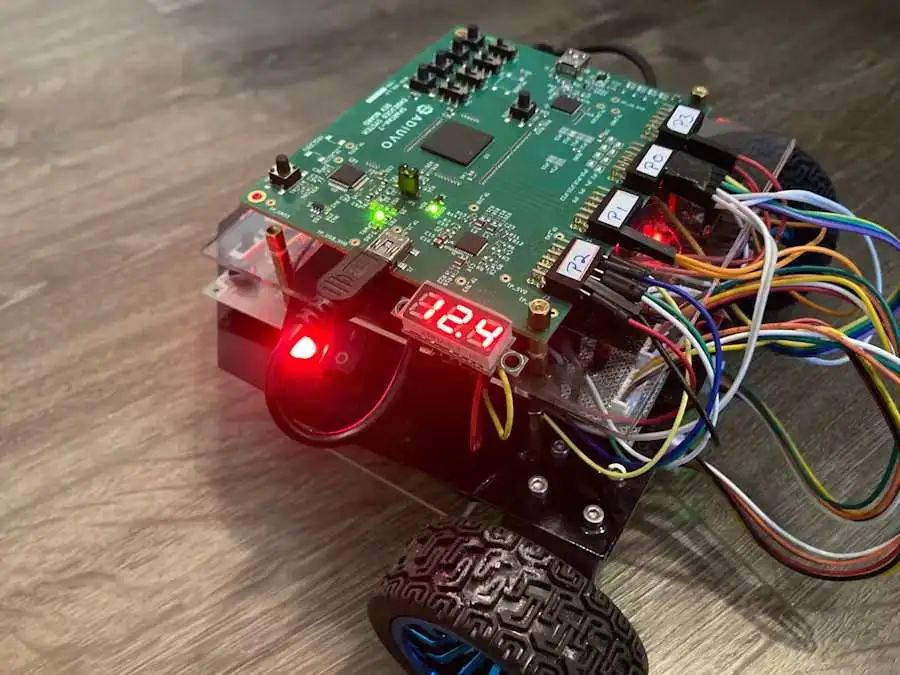

借助Verilog,在FPGA中实现了带编码器的两台电机的电机控制系统的RTL级设计。 介绍 借助硬件描述语言 (HDL) Verilog 和 AMD Vivado 设计套件,在 AMD Spartan-7 FPGA 中实现带编码器的两个电机的控制器系统的 RTL 设计。 在这个项目中,使用了搭载

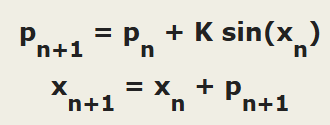

引言 今天继续常春藤名校之一——康奈尔大学的FPGA课程ECE 5760典型案例分享:基于DE1-SOC开发板的Chirikov标准映射求解器。 1. 项目概述 项目说明 该项目是在友晶DE1-SOC开发板实现Chirikov标准映射的求解器,并将其应用于图像加密和解密的概念验证。 2. Chi

2025年7月1日至3日,欧洲 FPGA大会在德国慕尼黑盛大举行。作为FPGA领域的年度盛会,此次大会吸引了来自全球各地的企业、专家与学者,共同探讨FPGA技术的前沿趋势与应用创新。我们有幸参与其中,收获颇丰。欧洲FPGA大会概况欧洲FPGA大会已成为欧洲地区可编程逻辑器件领域的权威专业会议。今年的大会在慕尼黑的NH慕

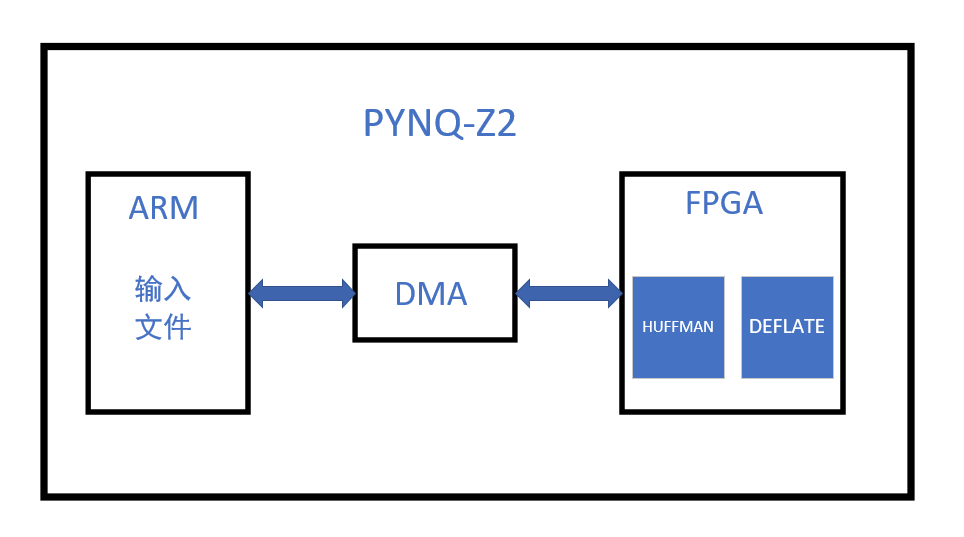

第一部分 设计概述 /Design Introduction 1.1设计目的 本设计中,计划实现对文件的压缩及解压,同时优化压缩中所涉及的信号处理和计算密集型功能,实现对其的加速处理。本设计的最终目标是证明在充分并行化的硬件体系结构 FPGA 上实现该算法时,可以大大提高该算法的速度。我们将首先使用C

第一部分 设计概述 /Design Introduction 1.1设计目的与应用 随着人工智能的发展,神经网络正被逐步应用于智能安防、自动驾驶、医疗等各行各业。目标识别作为人工智能的一项重要应用也拥有着巨大的前景,随着深度学习的普及和框架的成熟,卷积神经网络模型的识别精度越来越高。有名的LeNet-

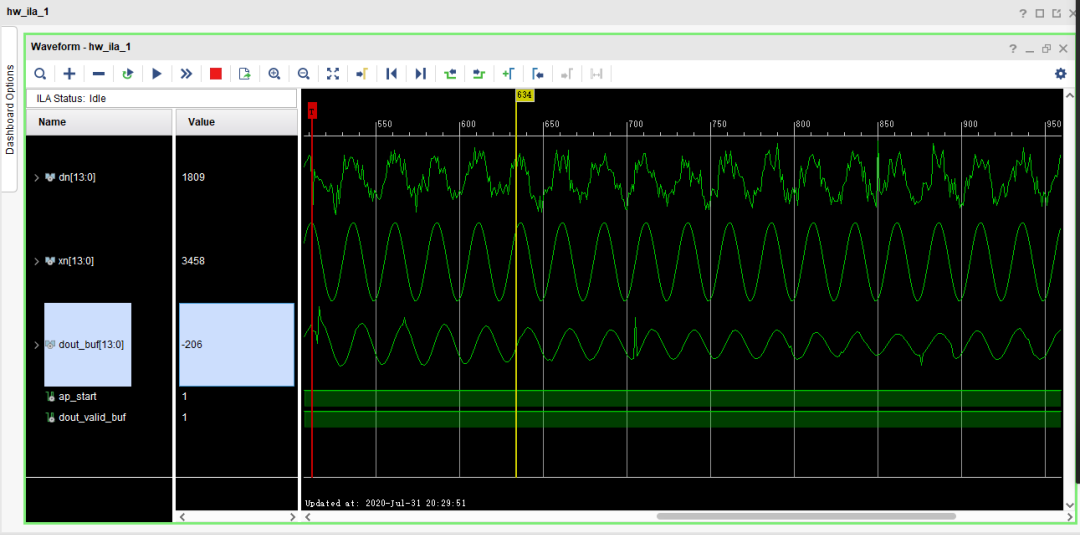

第一部分 设计概述 自适应滤波是近几十年发展起来的信号处理理论的的新分支。随着人们在该领域研究的不断深入,自适应处理的理论和技术日趋完善,其应用领域也越来越广泛。自适应滤波在通信、控制、语言分析和综合、地震信号处理、雷达和声呐波束形成,以及医学诊断等诸多科学领域均有着广泛的应用,也正是这些应用又反过来推动了自

如何为您的应用选择更理想的 DRAM? 对于嵌入式系统工程师而言,选择合适的 DRAM 至关重要,需综合考虑带宽、时延与功耗限制。在近期发布的白皮书中,我们详细比较了主要的内存类型(包括 DDR4、DDR5、LPDDR4 和 LPDDR5),并针对视频处理和 AI 推理等高吞吐量应用提供了实用的选择建议。

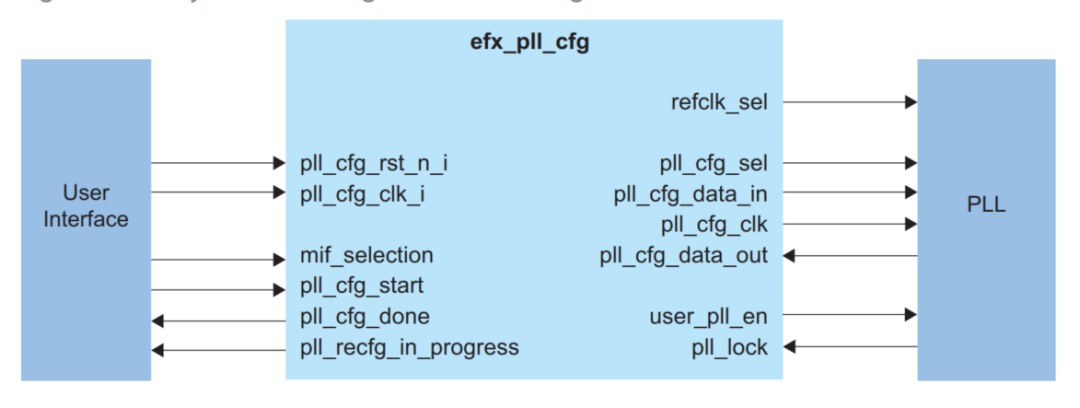

TJ375已经支持PLL的动态配置。打开PLL在Advance Settings中的Dynamic Reconfiguration中勾选Enable就可以了。最大可以支持85组配置参数。动态配置框图如下: (1)在interface中打开动态配置功能 使用PLL动态配置功能需要打开PLL的reset和

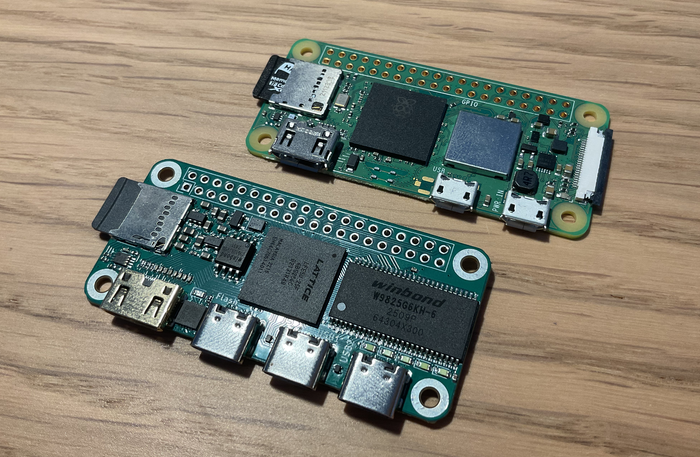

“Icepi Zero 是一款 Raspberry Pi Zero 尺寸的便携式 FPGA 开发板,基于 Lattice ECP5。” Made with KiCad 系列将支持新的展示方式。直接将以下链接复制到浏览器中(或点击“阅读原文”):https://ww