在当今高风险挑战的现代电路设计领域,工程师正面临着前所未有的压力——日益紧迫的项目交付期限与更繁重的工作负荷,使传统耗时费力的手动电磁(EM)调优成为难以承受的瓶颈。未来的趋势,属于自主化、AI 赋能的优化技术。

Cadence 诚邀您参加本次线上研讨会,我们将展示一套尖端的工作流程,全面革新您在无源器件设计中的实践方式。会议将演示 Cadence EMX Designer、EMX Planar

近日,楷登电子 Cadence 宣布,地平线征程® 6(J6)已成功将 Tensilica Vision DSP 集成至其系统级芯片中,并实现了规模化量产。Cadence Tensilica 将为搭载地平线 J6 系列的多款主机厂车型提供技术支持。此里程碑标志着 Cadence 与地平线进一步深化合作,双方共同推动面向大众市场的智能辅助驾驶解决方案成功落地。

地平线征程系列是地平线智能驾驶系统的核

创立不到两年的量引科技,正凭借一枚枚高性能光芯片突破国外技术垄断,打通AI时代数据传输的高速通道。从完成数千万天使轮融资到布局国际前沿赛道,这家初创企业的快速崛起,既是自身技术创新的突围,更是国产高端光芯片产业突破的生动缩影。

| 打通数据传输“高速路”

“光芯片就像是AI时代数据驶入高速通道的‘入口站’,光纤则是承载数据的‘高速公路’。只有依靠高性能光芯片,海量数据才能以光速实现高效传输。”量引

Cadence ChipStack AI Super Agent 集成 Google Gemini 模型,加速新一代代理驱动型设计自动化

中国上海,2026 年 4 月 24 日 —— 半导体与系统设计 AI 计算软件领域的行业领导者楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布与 Google Cloud 达成战略合作,利用 Google Cloud 上的 Gemini

此次合作升级整合了代理式 AI、物理仿真及数字孪生,旨在全面加速工程设计进程,为半导体、物理 AI 系统与 AI 工厂带来新一轮生产力提升

中国上海,2026 年 4 月 23 日 —— 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布扩大与 NVIDIA 的合作,共同推出涵盖代理式 AI、物理仿真与数字孪生的加速解决方案,以解锁更高水平的生产力,加速从半导体设计、物理 AI

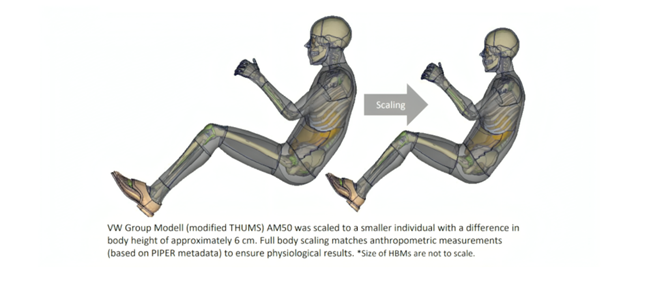

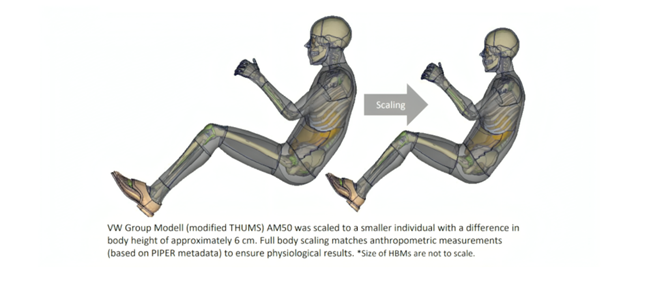

人体模型(HBM)的研究应用日益广泛,并正逐渐被纳入汽车评估规程之中,例如欧洲新车安全评鉴协会(Euro NCAP)的乘员和行人保护规程。目前主要有两种类型的人体模型被使用:一种是全球人体模型联盟(GHBMC)开发的模型,另一种是丰田公司开发的全面人体安全模型(THUMS)。这两种模型都包含了所有人体主要解剖结构,并已通过大量实验数据集的验证。每种模型都包含了与各种碰撞测试假人相对应的模型,例如

近日,国内RISC-V AI芯片创企奕行智能正式完成15亿元B轮融资,创下国内RISC-V领域最大融资纪录,标志着RISC-V架构在AI高性能计算与数据中心场景的产业价值得到进一步验证。

本轮融资阵容堪称豪华,由北京经开区产业升级基金(亦国投)、北京高精尖产业发展投资基金、北京信息产业发展投资基金、北京人工智能产业投资基金联合领投,和利资本、伯藜创投、赛意产业基金、龙江基金、青檀资本、九坤创投等新

在 IC25.1 版本中, Virtuoso ADE Artist 基于 Virtuoso ADE Assembler、Virtuoso Variation Option 以及 WiCkeD(WCD)工具的全部功能,提供一个统一的技术访问入口,并融合了全新的高级 AI/ML 功能,极大提升了设计效率,为工程师带来更高效、更智能的设计体验。

本次研讨会将了解学习 IC25.1 Virtuoso A

半导体生态系统是一个高度复杂、互相关联的框架,其中包括各种行业、技术和机构,旨在促进半导体器件的设计、制造、分销和应用。设计和知识产权 (IP) 提供商是该框架的组成部分,在经历了各种大幅演变之后,这些提供商已成为当代芯片开发中不可或缺的参与者。

随着上世纪 80 年代电子设计自动化 (EDA) 工具的出现,以及上世纪 90 年代半导体 IP 产业的发展,片上系统 (SoC) 设计越来越依赖于可复

没有什么比一套真实可用的系统更能建立信任。

这正是我们在拉斯维加斯 CES 2026 展会上展示的核心理念 —— 我们成功演示了业内首创的 3nm eUSB2V2 PHY IP,并与 eUSB2V2 控制器 IP 在完整的端到端系统中协同运行。最终实现了实时、真实场景下的 eUSB2V2 数据通路,传输速率高达 4.8 Gbps,充分展现了这一全新 USB 接口协议的广阔前景。

01

本次演示的重

在 IC25.1 版本中, Virtuoso ADE Artist 基于 Virtuoso ADE Assembler、Virtuoso Variation Option 以及 WiCkeD(WCD)工具的全部功能,提供一个统一的技术访问入口,并融合了全新的高级 AI/ML 功能,极大提升了设计效率,为工程师带来更高效、更智能的设计体验。

本次研讨会将了解学习 IC25.1 Virtuoso A

在 IC25.1 版本中, Virtuoso ADE Artist 基于 Virtuoso ADE Assembler、Virtuoso Variation Option 以及 WiCkeD(WCD)工具的全部功能,提供一个统一的技术访问入口,并融合了全新的高级 AI/ML 功能,极大提升了设计效率,为工程师带来更高效、更智能的设计体验。

本次研讨会将了解学习 IC25.1 Virtuoso A

当前人工智能席卷全球,半导体产业迎来新一轮发展浪潮。与以往依赖制程微缩的发展路径不同,这一轮需要在系统架构、互连技术与数据流动方式等多个层面的全面升级才能满足需求。这使芯片与系统的设计范式正在发生根本性的转变,无论算力规模、数据带宽,还是系统复杂度都远远超出传统设计工具与方法的承载范围。作为半导体产业的基石,EDA/IP 依然是破解当前挑战的关键环节。

在 IIC Shanghai 2026 国际

2026 年 4 月 6 日,在上海交通大学建校 130 周年校友返校日之际,由上海交通大学集成电路学院(信息与电子工程学院)校友会与上海交大集成电路行业校友会联合主办的“XIN 创未来 共谱华章——新一代信息技术下的产业协同和职业发展”行业论坛在思源湖畔顺利举行。

作为上海交通大学 1996 届本科校友,Cadence 全球研发副总裁、三维集成电路设计与分析事业部总经理顾鑫受邀出席论坛,与校地

以前领导给我打电话,说他们做的板子性能达不到预期,怀疑是板上线宽的问题。

虽然我觉得1GHz这个频率,板子的影响应该不至于这么大,但是万一呢?于是,我对领导说,那把PCB发给我,我来仿真一下吧,看看PCB上的线宽是不是有影响。

本来想,就用最原始的方法,把PCB的TOP层和孔的一些信息导出到dxf,然后稍微手工删减一下,再导入ADS,设置个两层板的叠层结构,一仿真,不就完事了。

哪想,拿到PCB以

1.算法简介

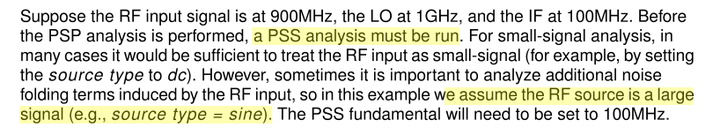

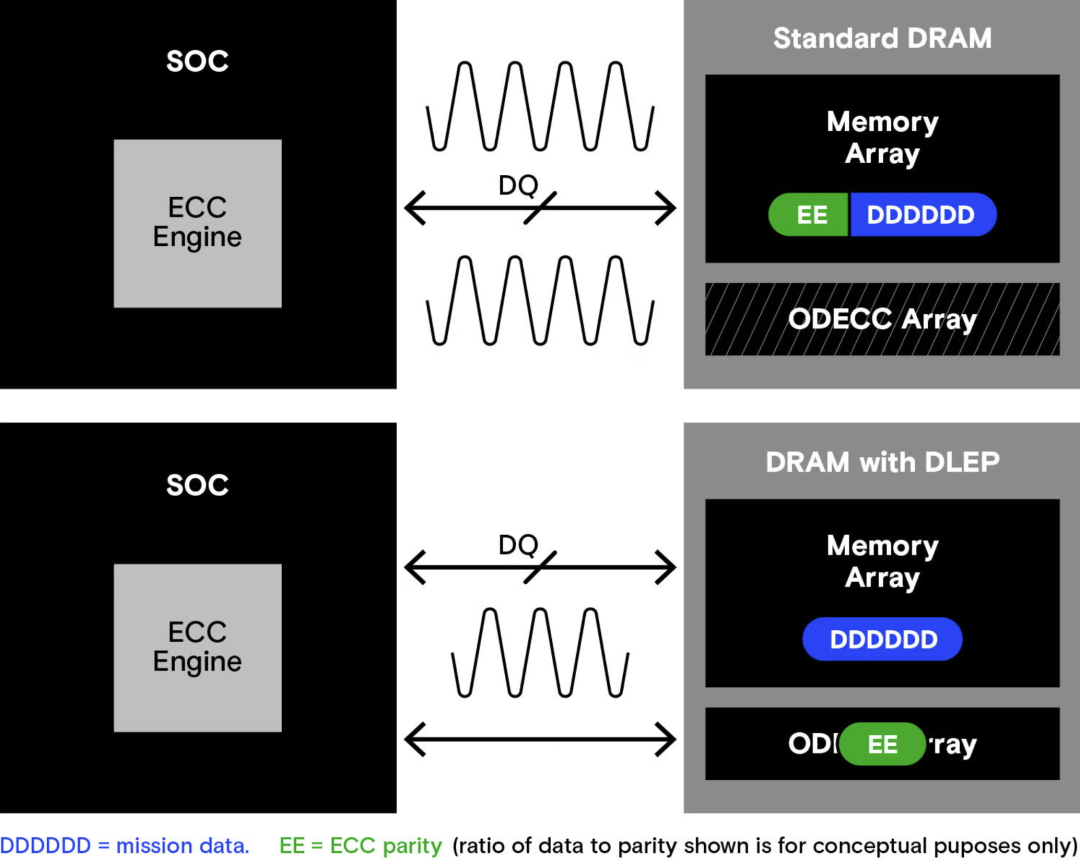

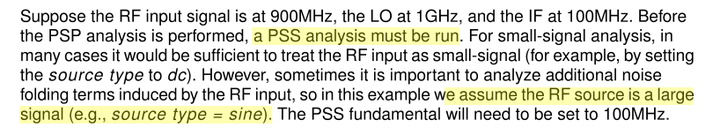

在Cadence SpectrePF 里 ,psp 即 pss+sp,hbsp 即 hb+sp, 二者都是可以仿真含谐波或周期信号的S参数。与sp的区别在于,psp和hbsp仿真的是大信号S参数,sp仿真得到的是小信号S参数

psp 和 hbsp的设置基本一致,得到的结果也接近,最好不要一起跑(笔者一起跑得到的结果有误)。下面以psp为例进行说明。

2.端口设置

在端口设置上,与s