以下文章来源于郝旭帅电子设计团队,作者郝旭帅

本篇主要是DDRX SDRAM中的预取技术说明

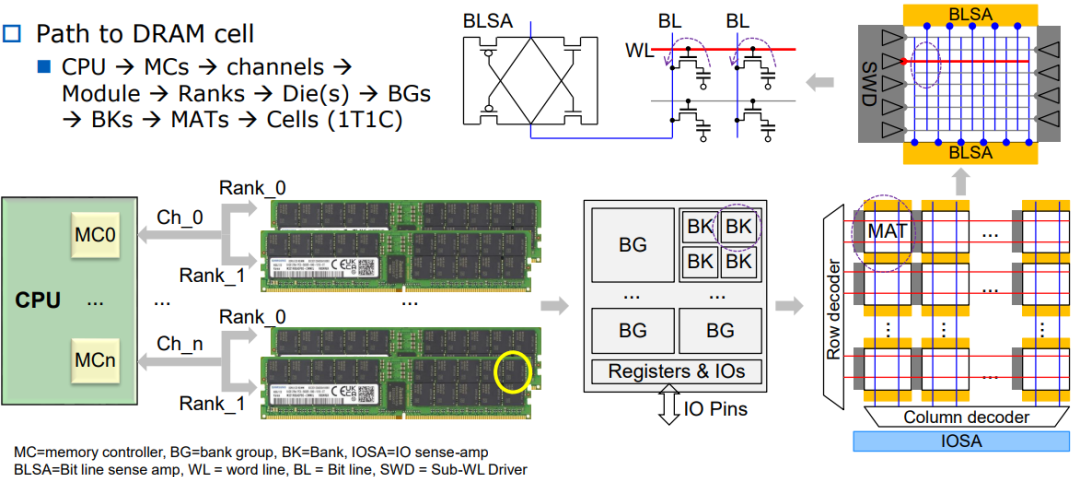

DDRX SDRAM外部接口数据传输率需要不断提高(从DDR到DDR5),内存芯片内部的DRAM存储单元(电容阵列)的物理访问速度有上限,无法随着接口速度的线性增长。

预取(Prefetch)技术是DDR SDRAM实现高速数据传输的关键技术之一。它的基本思想是:在内存核心(存储阵列)和外部数据总线之间设置一个缓冲区,内存核心工作在一个相对较低的频率,而数据总线工作在一个较高的频率,通过一次从存储阵列中读取多个数据(预取),然后在外部数据总线上通过多个时钟周期(或双沿传输)将数据依次传输出去,从而提升数据传输率。

具体来说,DDR SDRAM的预取长度(Prefetch Length)是指每次从存储阵列中读取的数据位数与每次对外传输的数据位数的比值。例如,对于DDR1,预取长度是2n;DDR2是4n;DDR3是8n;DDR4也是8n(但通过Bank Group分组来模拟更高的预取);DDR5则是16n(但通过两个独立的通道实现)。

下面我们详细说明:

1. DDR1 (2n Prefetch) 内存核心(存储阵列)的工作频率是外部数据传输频率的一半。例如,对于DDR-400,外部数据传输频率是400MT/s,内存核心频率是200MHz。 每次从存储阵列中读取2位数据(针对每个数据引脚),然后在外部数据总线上通过两个时钟边沿(上升沿和下降沿)将这两位数据依次传输出去。 这样,在内存核心工作频率不变的情况下,外部数据传输率翻倍。

2. DDR2 (4n Prefetch) 内存核心频率进一步降低,为外部数据传输频率的四分之一。例如,DDR2-800,外部数据传输频率为800MT/s,内存核心频率为200MHz。 每次从存储阵列中读取4位数据,然后在外部数据总线上通过4个时钟边沿(两个时钟周期,因为每个周期有两个边沿)将这4位数据依次传输出去。 这样,在相同的内存核心频率下,DDR2的数据传输率是DDR1的两倍(因为预取长度翻倍)。

3. DDR3 (8n Prefetch) 内存核心频率为外部数据传输频率的八分之一。例如,DDR3-1600,外部数据传输频率为1600MT/s,内存核心频率为200MHz。 每次从存储阵列中读取8位数据,然后在外部数据总线上通过8个时钟边沿(4个时钟周期)将这8位数据依次传输出去。 这样,在相同的内存核心频率下,DDR3的数据传输率是DDR2的两倍,是DDR1的四倍。

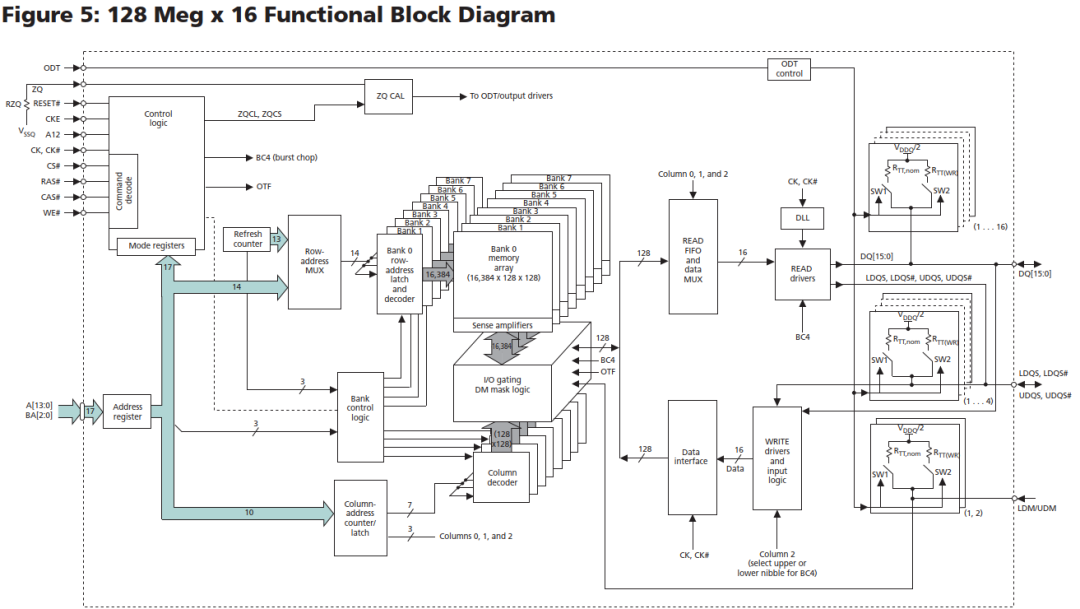

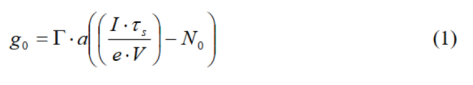

上述结构为ddr3 sdram 内部结构图。8bank,16krow,1kcol,x16.

按照我们正常的理解:

每一个bank应该有16k行,1k列,每个存储空间可以存储16bit。

但是实际上我们通过结构图看到的是:16k行,128列,每个存储空间可以存储128bit。

那也就是说:每次读写都是128位,而接口的宽度是16,相当于读取出来了8个我们认为的存储地址。

所以ddr3的内部就可以以接口速率的1/8运行。

4. DDR4 (8n Prefetch with Bank Group) DDR4也使用8n预取,但是引入了Bank Group(存储体分组)的概念。每个Bank Group可以独立操作,从而可以在不同的Bank Group之间交替执行操作,类似于提高了并行度,从而在保持8n预取的情况下进一步提升了性能。 例如,DDR4-3200,外部数据传输频率为3200MT/s,内存核心频率为400MHz(因为8n预取,核心频率为3200/8=400MHz)。注意,这里核心频率比DDR3的例子高,因为DDR4的速度更高,但预取倍数相同。

5. DDR5 (16n Prefetch) DDR5将预取长度提升到16n,但这是通过两个独立的通道(每个通道40位,其中32位数据位和8位ECC位)来实现的。实际上,每个通道的预取长度可以认为是8n,但整体上,内存核心一次提供16n的数据,然后通过两个通道传输。 例如,DDR5-6400,每个通道的数据传输率是3200MT/s,整体是6400MT/s。内存核心频率为400MHz(假设每个通道是8n预取,那么每个通道的核心频率为3200/8=400MHz,两个通道共享核心阵列,但可以交错访问)。

预取技术的优点:

允许内存核心工作在相对较低的频率,从而降低功耗和制造难度(因为存储阵列的访问速度难以提升)。

通过提高预取长度,可以在不提高内存核心频率的情况下增加外部数据传输率。

预取技术的缺点:

预取长度增加会导致访问延迟(Latency)的增加,因为每次访问需要从存储阵列中读取更多的数据,而且如果访问模式不是顺序的(例如随机访问),那么预取的数据可能用不上,造成浪费。

为了缓解这个问题,DDR4和DDR5引入了Bank Group,通过并行操作来隐藏延迟。

总结:

预取技术是DDR SDRAM实现高速数据传输的核心技术,它通过降低内存核心工作频率并提高每次访问的数据量来实现更高的数据传输率。随着DDR代际的升级,预取长度不断增加,同时通过其他技术(如Bank Group、多通道)来克服预取带来的延迟增加问题。

原文标题:DDRX SDRAM中的预取技术说明

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

评论区

登录后即可参与讨论

立即登录