从平面到立体:晶体管工艺节点的“缩微”之旅

芯片上的“2纳米”真的是指物理尺寸吗?从平面到FinFET,再到如今最前沿的GAA,制程节点已从实测刻度演变为性能勋章。本文带你拆解晶体管如何从二维“躺平”到三维“站立”,揭秘先进制程命名背后那些看不见的物理跨越与等效逻辑。 在芯片技术的宣传中,我们常常听到“5纳米”“3纳米”“2纳米”这样的词汇。很多人以为这指的是晶体管某个部分的实际物理尺寸,其实并不完全如此。从平面晶体管到FinFET,再到G

关于「晶体管」的技术文章、设计资料与工程师讨论,持续更新。

芯片上的“2纳米”真的是指物理尺寸吗?从平面到FinFET,再到如今最前沿的GAA,制程节点已从实测刻度演变为性能勋章。本文带你拆解晶体管如何从二维“躺平”到三维“站立”,揭秘先进制程命名背后那些看不见的物理跨越与等效逻辑。 在芯片技术的宣传中,我们常常听到“5纳米”“3纳米”“2纳米”这样的词汇。很多人以为这指的是晶体管某个部分的实际物理尺寸,其实并不完全如此。从平面晶体管到FinFET,再到G

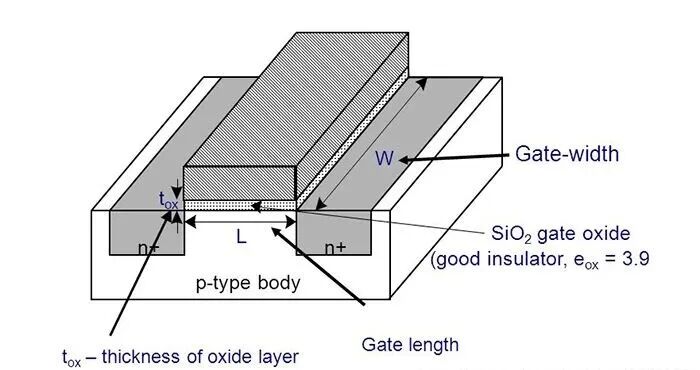

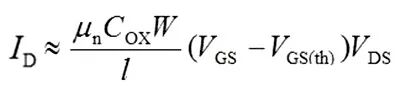

本文介绍了影响晶体管饱和电流的各项因素。 在芯片性能的比拼中,有一个参数几乎成了晶体管速度的代名词——饱和电流(IdSAT)。它衡量的是晶体管完全导通时,从漏极流向源极的最大电流。IdSAT越大,逻辑门的翻转就越快,芯片的主频就越高。那么,这个决定芯片“马力”的关键参数,究竟被哪些制造工艺所左右?我们从最基本的物理公式出发,一层层拆解。 一、IdSAT的“第一性原理”公式对于先进工艺中的短沟道晶

在计算机中,CPU作为中央处理器,内部包含了算术逻辑单元,可以实现数学运算。要计算1+1=2,就需要从微架构级、逻辑门级、晶体管级、物理级等方面进行分析。 从微架构级,加法运算会使用加法器或者半加法器; 半加法器的门级电路如下: 我们知道,芯片内部都是由无数个晶体管组成的,晶体管实现与门比较容易,但实现异或门就会稍复杂,上面的异或门可以使用两个与门和一个或门来构建 当然,我们还可以用其他方式来

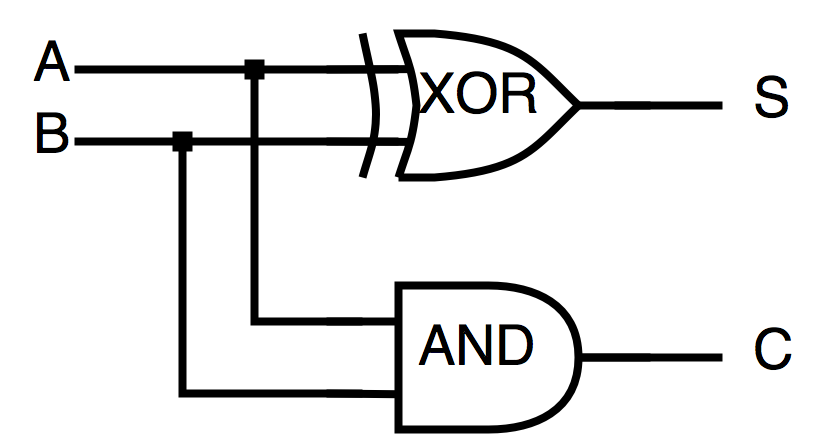

在电源供电设计中,经常出现外接负载电路短路引起供电电路损坏和负载损坏。 因此防短路电路在电路设计中起着保护电路的重要作用。 这次介绍一个简单实用的防短路电路,在实际项目电路设计中可以作为参考。 如图所示:用1个NPN,1个PNP,6个电阻和1个光耦。 当Ui接上电源,晶体管Q2基极电压大于发射集电压,Q2导通;从而Q1基极电压小于发射集电压,Q1导通,Uo=Ui,光耦EL357的1脚和2脚之间压