芯片上的“2纳米”真的是指物理尺寸吗?从平面到FinFET,再到如今最前沿的GAA,制程节点已从实测刻度演变为性能勋章。本文带你拆解晶体管如何从二维“躺平”到三维“站立”,揭秘先进制程命名背后那些看不见的物理跨越与等效逻辑。

在芯片技术的宣传中,我们常常听到“5纳米”“3纳米”“2纳米”这样的词汇。很多人以为这指的是晶体管某个部分的实际物理尺寸,其实并不完全如此。从平面晶体管到FinFET,再到GAA,工艺节点的命名已经从“物理尺度”演变为“等效性能”的代名词。今天我们就来聊聊,这个“纳米”到底是什么意思,以及晶体管是如何一步步“缩”到2纳米的。

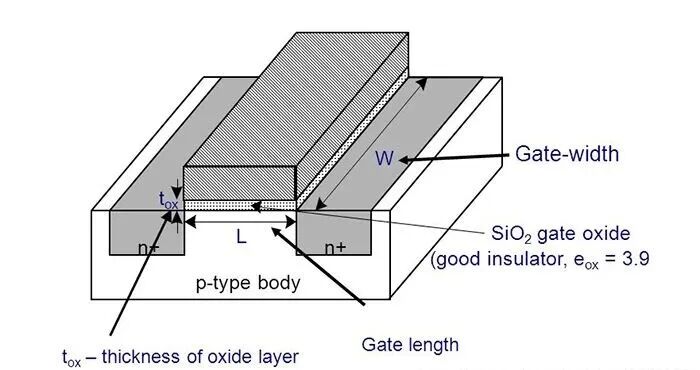

平面晶体管时代:栅长说了算

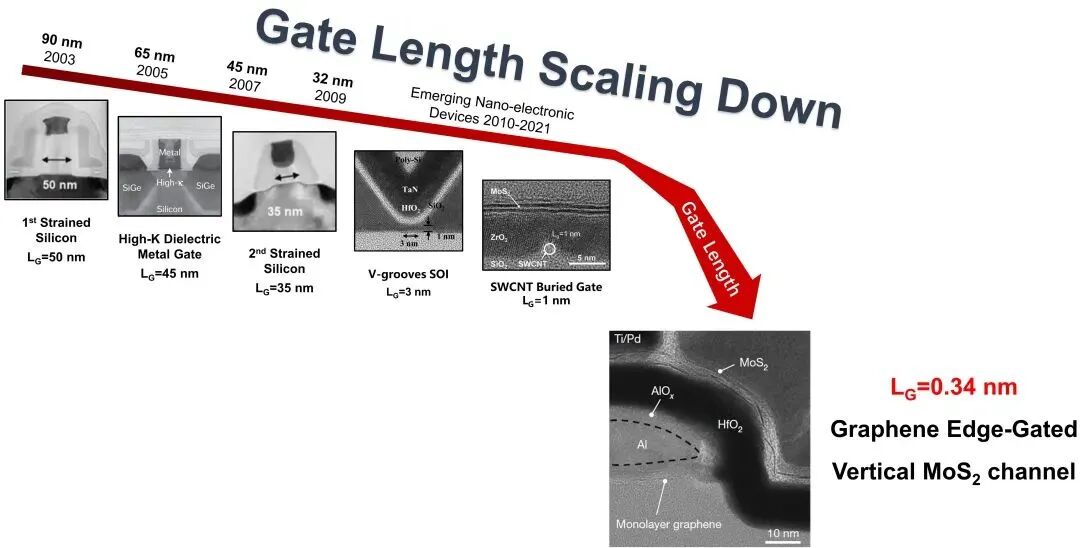

在传统的平面晶体管时代,“纳米”这个数字的含义相对直接——它指的是晶体管的栅极长度,也就是电流从源极流向漏极时,栅极控制的那段沟道长度。平面晶体管的结构很简单:源极和漏极在硅衬底的表面,栅极横跨在它们之间的沟道上方。电流沿着硅表面水平流动,栅极就像一道闸门,通过电压控制沟道的开启和关闭。在这个结构里,栅极长度就是决定晶体管快慢的关键尺寸。栅长越短,电子从源极跑到漏极的路程就越短,开关速度就越快,同时单个晶体管占用的面积也越小。在90纳米、65纳米、45纳米这些节点,工艺节点的数字基本等于晶体管的实际栅长。但随着尺寸不断缩小,物理极限开始出现。当栅长缩短到20纳米左右时,栅极对沟道的控制能力急剧下降,源漏之间的漏电流变得无法接受,晶体管关不住了。这就是著名的“短沟道效应”。

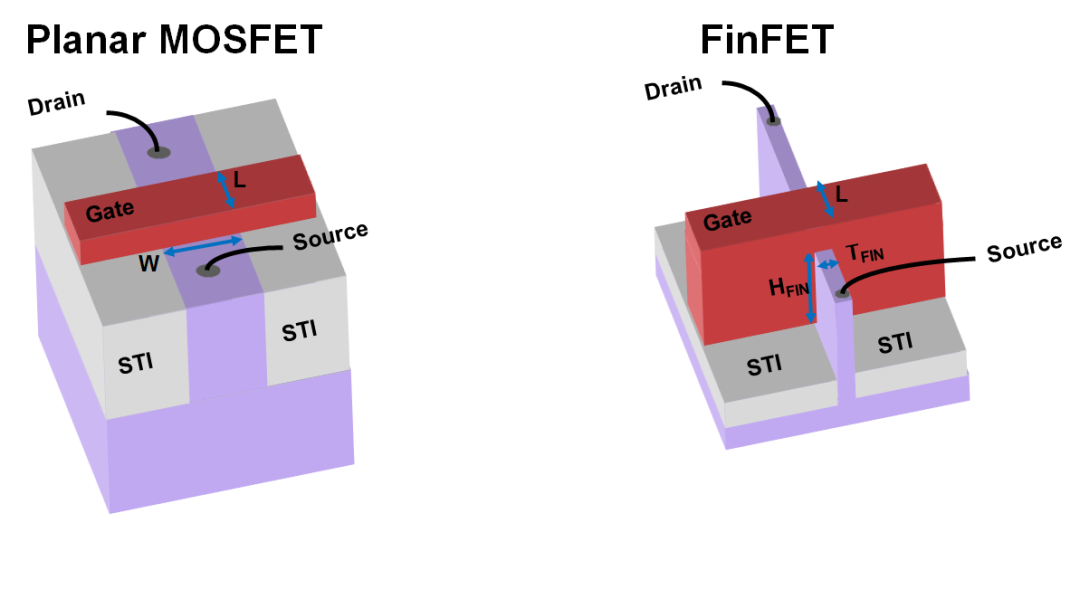

FinFET时代:从二维到三维的飞跃

为了突破平面晶体管的物理极限,工程师们发明了FinFET——鳍式场效应晶体管。它的核心思想很简单:把原本平躺在表面的沟道“竖起来”,让栅极从三面包围它。在FinFET中,源极和漏极不再是硅表面的两个区域,而是硅衬底上凸起的一道“鳍”。这个鳍是垂直的薄片,栅极材料从三个方向包裹着鳍的侧面和顶面。这样一来,即使鳍的宽度(也就是原来意义上的“沟道长度”)被缩得很短,栅极仍然能牢牢控制沟道中的电场,有效抑制漏电流。问题是,到了FinFET时代,“纳米”这个数字就不再直接等于某个物理尺寸了。一个22纳米的FinFET,其栅极实际长度可能在20到30纳米之间,但决定工艺代际的已经不是单纯的栅长,而是等效的晶体管密度和性能。换句话说,22纳米这个数字代表的是“如果采用平面结构,要达到同样的密度和性能,需要的栅长大约是多少”。这是一种等效换算,而非实际测量。

随着FinFET技术演进到14纳米、10纳米、7纳米、5纳米,每一代都在做同一件事:把鳍做得更薄、更高、间距更密,从而在同样的面积上塞进更多的晶体管。7纳米FinFET的鳍片高度可能已经超过宽度的好几倍,这种三维结构让晶体管在物理尺寸没有大幅缩小的情况下,实现了等效微缩。

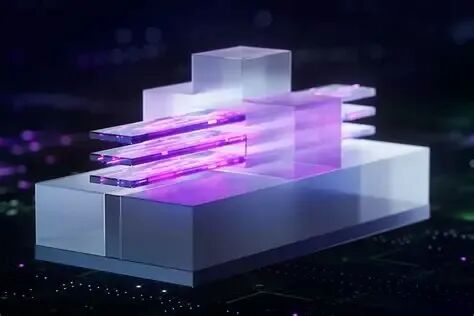

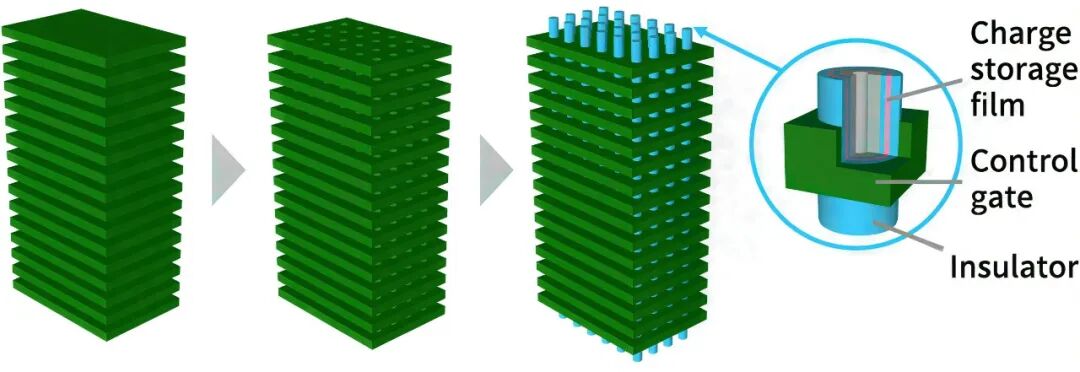

GAA时代:全包围的终极控制

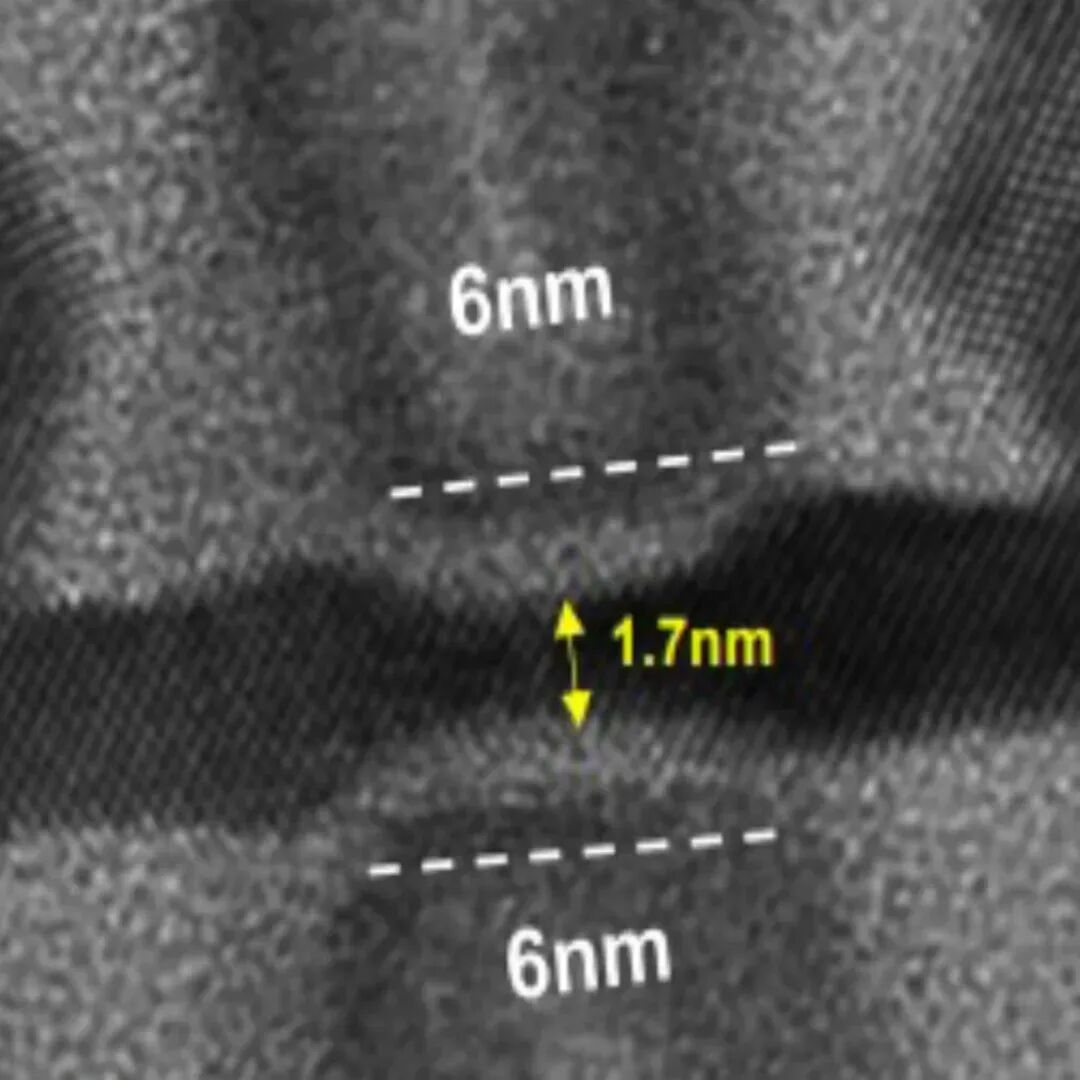

当FinFET推进到3纳米、2纳米节点时,鳍式结构也开始面临极限。鳍片做不了无限薄,也做不了无限高,当鳍的宽度缩小到只有几个原子层时,量子效应开始显现,栅极控制再次变得困难。于是,全环绕栅极晶体管登上了舞台。GAA晶体管把FinFET中那个“鳍”改成了纳米片或纳米线——这些薄片水平悬浮在源漏之间,栅极材料从四面八方把每一根纳米片完全包裹起来。360度的包围意味着栅极对沟道的控制达到了极致,几乎可以杜绝任何漏电路径。在GAA时代,“2纳米”这个数字的含义更加抽象了。它代表的是在性能、功耗和面积三方面的综合表现,相当于平面工艺时代2纳米栅长所能达到的水平。实际的物理尺寸可能是十几纳米,但由于立体结构带来的优越控制能力,其等效密度和性能已经跨越了2纳米这个里程碑。

一等效微缩的本质:从物理到逻辑

为什么工艺节点可以脱离实际尺寸,变成一个“等效”概念?核心原因是晶体管从二维走向了三维。在平面时代,要提升性能,只能缩短栅长、减小面积。这是纯粹的物理微缩。到了FinFET和GAA时代,工程师们多了一个维度——垂直方向。通过把沟道竖起来,或者堆叠多层纳米片,可以在不大幅缩小物理尺寸的前提下,大幅提升单位面积的驱动电流和晶体管密度。举个例子:一个5纳米FinFET,它的鳍可能只有5纳米宽,但高度可能是40纳米。从占用面积看,它可能只相当于平面工艺的几十纳米级别,但从性能看,它已经超过了平面工艺5纳米的理论水平。所以,工艺节点已经不再是单纯描述尺寸的物理量,而是一个衡量技术代际的商标。

2纳米及以后:不再有“实际尺寸”

到了2纳米节点,情况变得更加清晰。无论是台积电的N2、三星的SF2还是英特尔的Intel 20A,它们采用的都是GAA结构(不同公司叫法不同,纳米片、纳米带、环栅等),其物理栅极长度可能在12纳米到18纳米之间,但等效密度和性能已经相当于平面工艺2纳米的水准。在2纳米之后,晶体管会走向互补场效应晶体管——把NMOS和PMOS在垂直方向堆叠起来,进一步压缩面积。届时,工艺节点的数字将更加“符号化”,它代表的将是整个技术平台的综合性能指标,而不是任何一个可测量的物理尺寸。

结语

从平面晶体管的栅长,到FinFET的鳍宽,再到GAA的等效性能,“纳米”这个词的含义已经发生了根本变化。它不再是游标卡尺能测量出的数值,而是一代代工程师在物理极限边缘不断突破的勋章。当你听到“2纳米芯片”时,可以把它理解为一个技术时代的标志:我们不再单纯靠“缩”来推动摩尔定律,而是靠把晶体管从平面“立”起来、从三面“包”起来、从四面“围”起来,在三维空间里寻找继续前进的道路。

评论区

登录后即可参与讨论

立即登录