本文介绍了影响晶体管饱和电流的各项因素。

在芯片性能的比拼中,有一个参数几乎成了晶体管速度的代名词——饱和电流(IdSAT)。它衡量的是晶体管完全导通时,从漏极流向源极的最大电流。IdSAT越大,逻辑门的翻转就越快,芯片的主频就越高。那么,这个决定芯片“马力”的关键参数,究竟被哪些制造工艺所左右?我们从最基本的物理公式出发,一层层拆解。

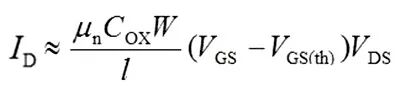

一、IdSAT的“第一性原理”公式对于先进工艺中的短沟道晶体管,饱和电流可以用一个简化的模型来描述:IdSAT = (1/2) × μ × Cox × (W/L) × (Vgs - Vth)^2其中,μ是载流子迁移率,Cox是栅氧化层电容,W是沟道宽度,L是沟道长度,Vgs是栅源电压,Vth是阈值电压。从这个公式可以清晰地看到,提升IdSAT无非两条路:要么增大公式中的“正面因子”(μ、Cox、W/L、Vgs-Vth),要么缩小沟道长度L。而芯片制造中的每一道关键工艺,都在精准地调控这些因子。

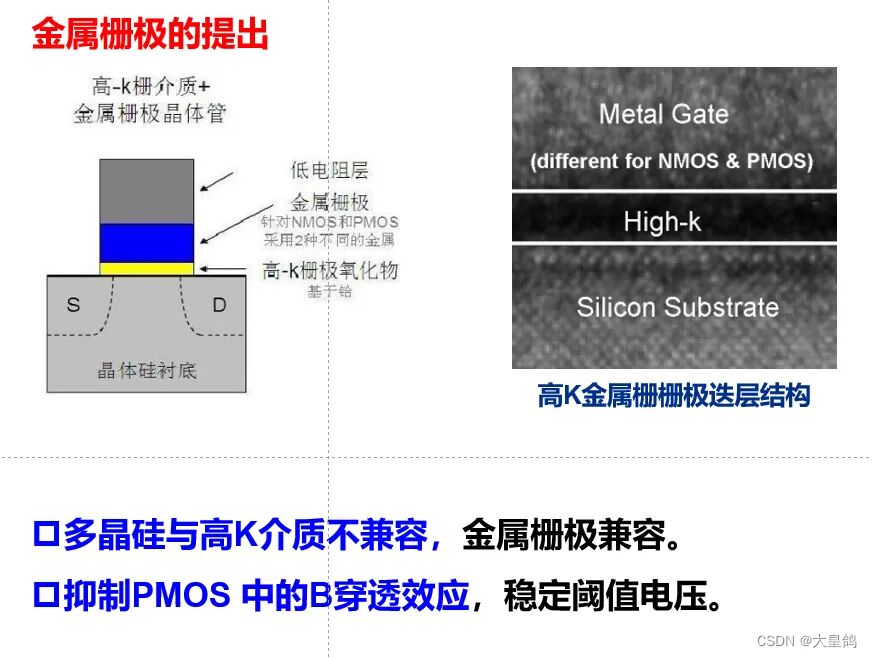

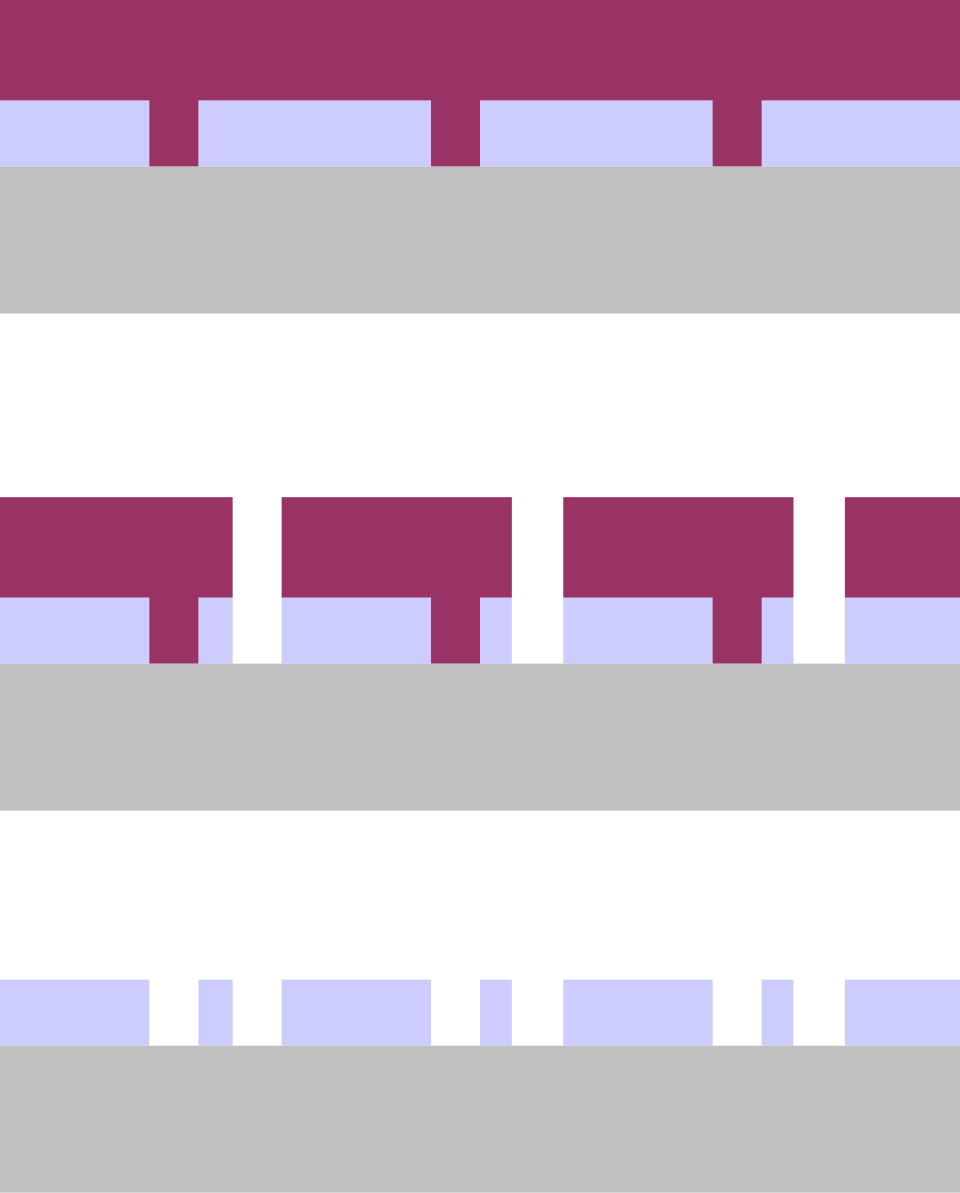

二、栅氧化层厚度:电容的“放大器”栅氧化层电容Cox = εox / Tox,其中εox是介电常数,Tox是氧化层物理厚度。Tox越薄,Cox越大,IdSAT就越高。这也是为什么工艺节点不断追求更薄的栅氧——从90纳米的1.4纳米到5纳米的0.7纳米左右。但Tox不能无限减薄,否则量子隧穿导致的栅极漏电会急剧增加。因此在先进节点,工程师用高介电常数材料(如HfO₂)替代SiO₂,在保持较大物理厚度的同时实现更小的等效氧化层厚度,兼顾低漏电和高Cox。

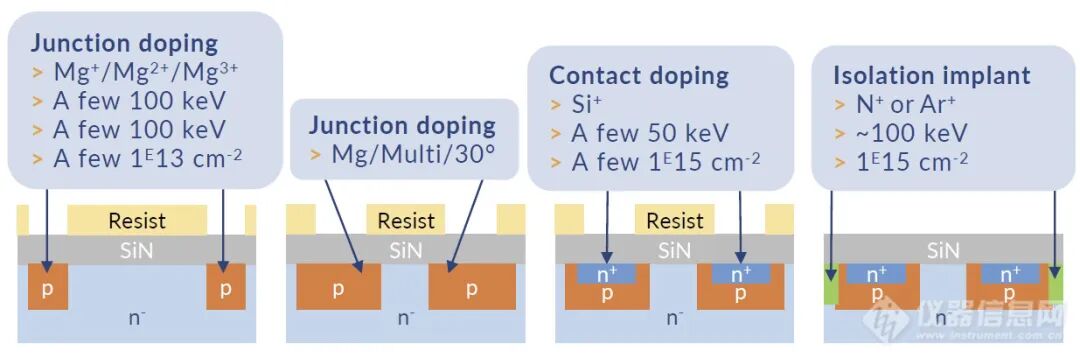

三、离子注入与阈值电压:开关的“门槛”阈值电压Vth是晶体管从关到开的临界栅压。为了让晶体管在低压下快速开启,我们希望Vth尽可能低。但Vth过低会导致关态漏电激增。Vth主要由沟道离子注入剂量决定:注入的掺杂浓度越高,Vth越大。工程师通过精确控制注入能量和剂量,将Vth设定在一个最优值(通常0.2-0.4V)。此外,栅极材料的功函数也直接影响Vth。传统多晶硅栅的功函数固定,而金属栅极可以通过选择不同功函数的金属(如TiN、TaN等)来精细调节Vth,实现多阈值电压设计,满足不同电路对速度和功耗的差异化需求。

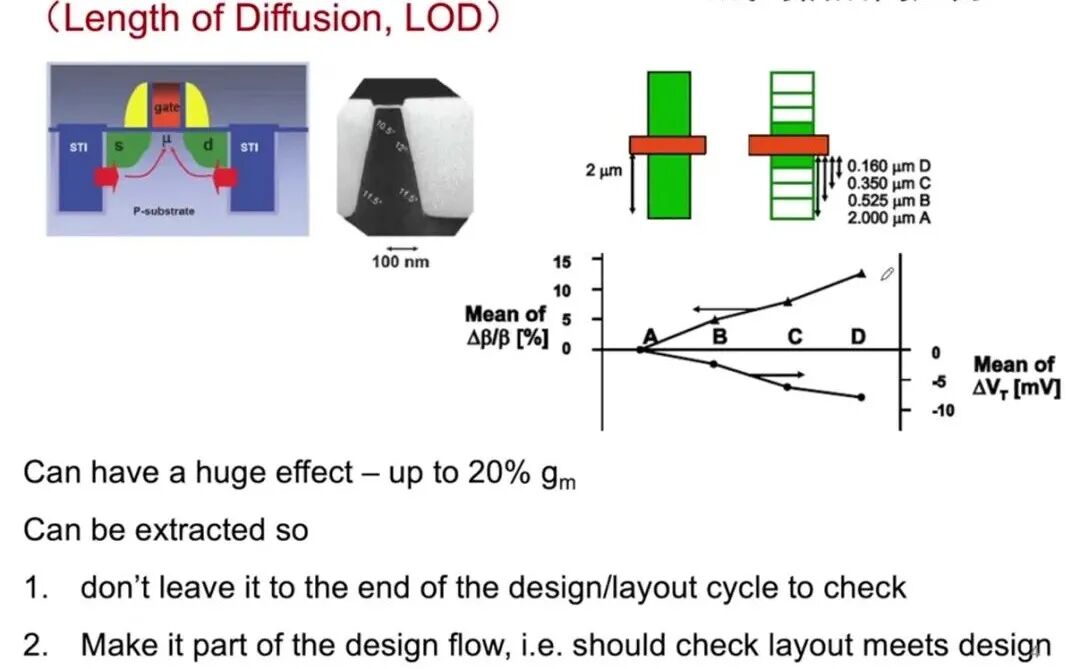

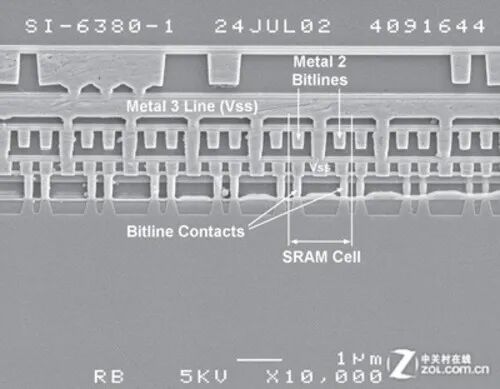

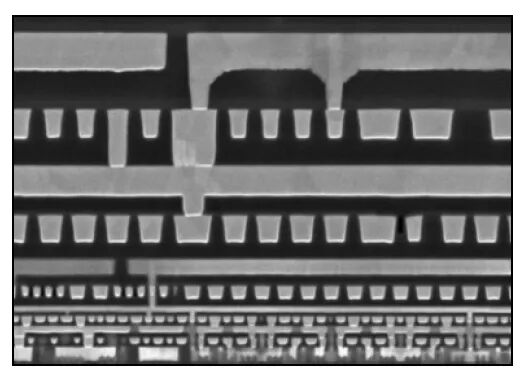

四、源漏间距与沟道长度:电子奔跑的“赛道”公式中的沟道长度L,是源极和漏极之间的距离。L越短,IdSAT越大,因为电子跑完这段路程的时间更短。这正是摩尔定律的核心——不断缩小晶体管尺寸。但L缩短会引发短沟道效应,导致Vth下降、漏电增加。为了抑制短沟道效应,源漏结深必须做得极浅,这就是所谓的“源漏cell pitch”缩小的含义。此外,抬升源漏技术通过在浅结上外延高掺杂硅层,降低接触电阻,从而进一步提升实际IdSAT。

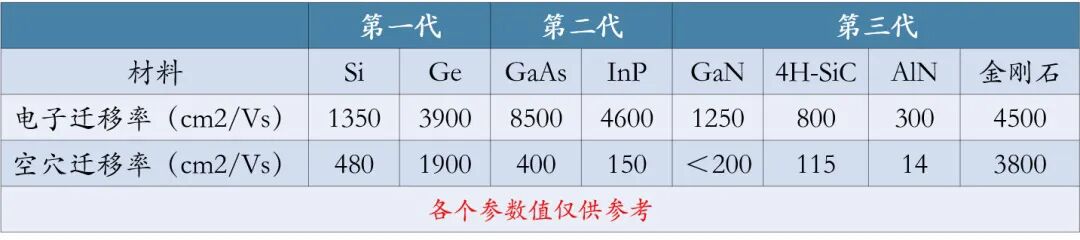

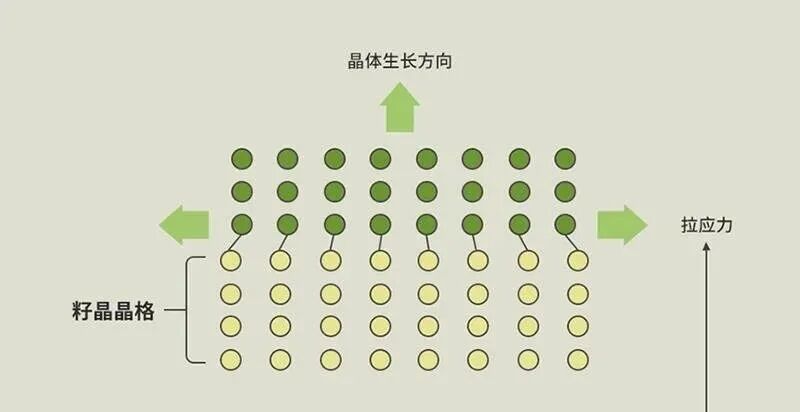

五、迁移率:载流子的“速度极限”迁移率μ反映了电子或空穴在电场下的平均漂移速度。μ越高,IdSAT越大。应变硅技术通过外延锗硅或碳化硅,在沟道中引入应力,改变硅的能带结构,从而显著提高迁移率。PMOS采用压应力提升空穴迁移率,NMOS采用张应力提升电子迁移率。迁移率的提升是“免费”的——不增加功耗,不增大面积,直接提高性能。

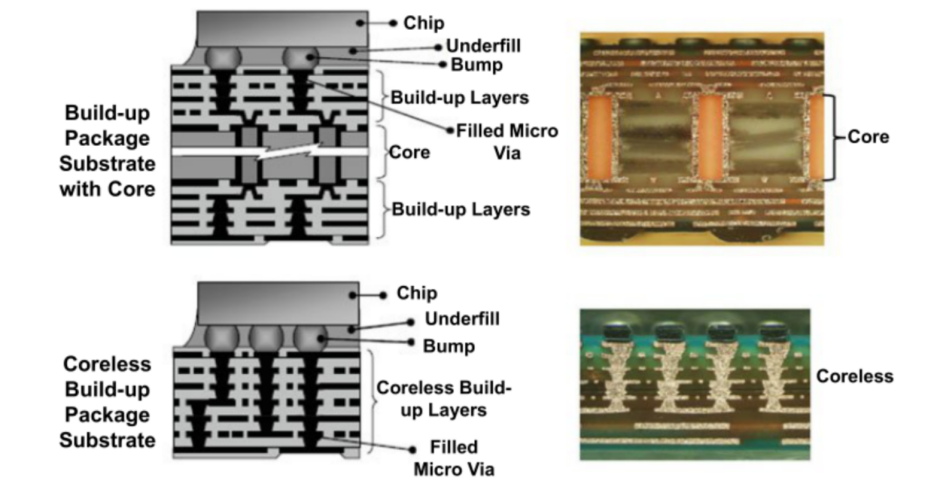

六、其他关键工艺:接触电阻与寄生效应公式之外,还有一些实际因素同样影响IdSAT。源漏接触电阻(Rc)如果过大,会形成额外的电压降,等效降低Vds,从而减少IdSAT。因此,在源漏区顶部形成低电阻的金属硅化物(如TiSi₂、CoSi₂)至关重要。此外,栅极材料的电阻和互连寄生电容也会间接影响IdSAT的测量值。七、总结:多变量协同的艺术从公式IdSAT ∝ μ × Cox × (Vgs-Vth)^2 / L 出发,我们看到了影响IdSAT的五大工艺杠杆:栅氧化层厚度(Cox)、沟道掺杂(Vth)、栅极功函数(Vth)、沟道长度(L)和应变工程(μ)。每一项都不是独立变量:减薄Tox会增加Cox但也可能恶化可靠性;降低Vth会提升IdSAT但漏电也会增加;缩短L会提高速度但短沟道效应必须被抑制。芯片工程师的工作,正是在这些相互制约的变量之间,找到那个最优的平衡点,让晶体管的“马力”在功耗和可靠性的边界上,拉到最满。

评论区

登录后即可参与讨论

立即登录