SK海力士HBM混合键合良率取得突破,但成本挑战仍存

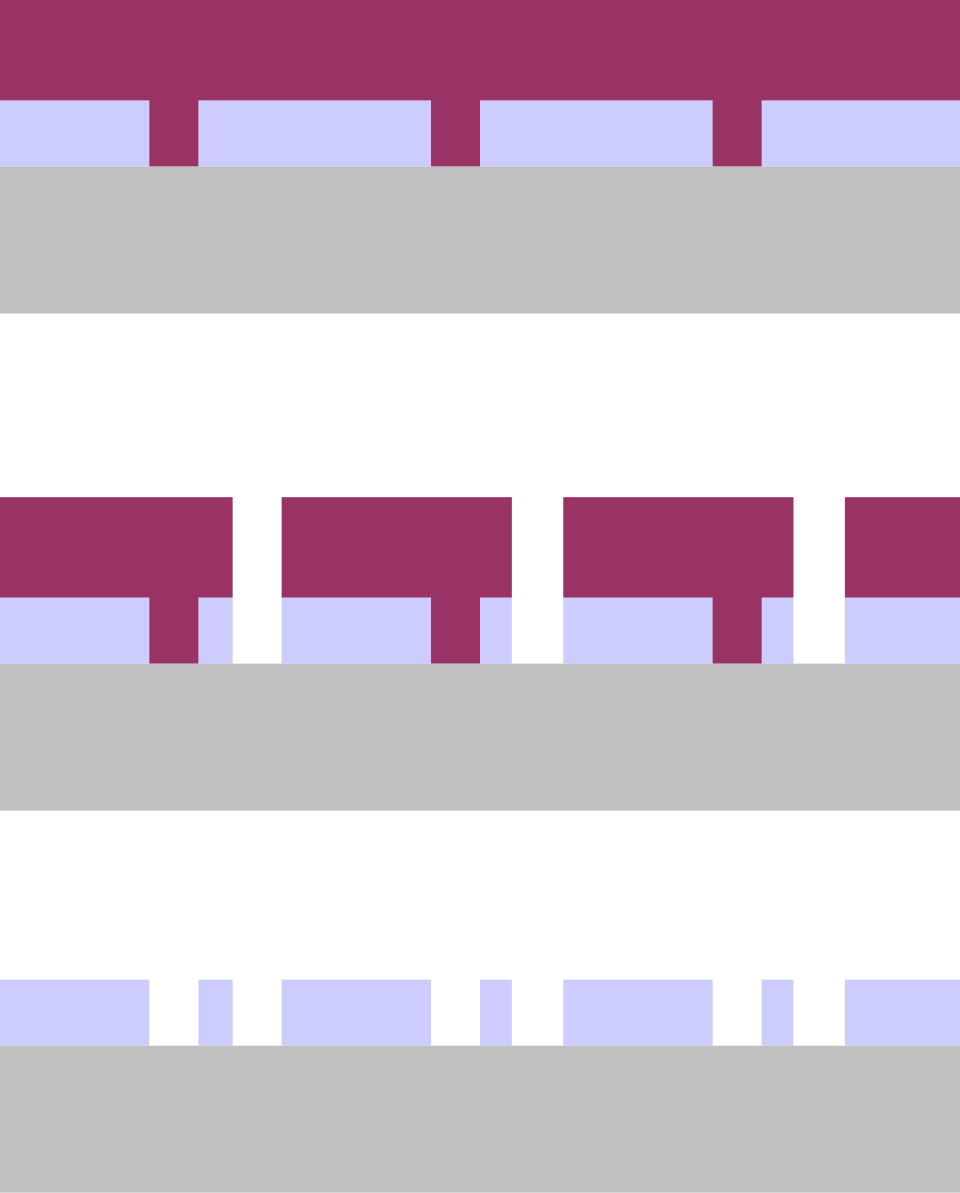

据韩媒thelec最新报道,在4月28日于首尔举行的一场半导体会议上,SK海力士技术负责人金钟勋(Kim Jong-hoon)透露,公司应用于HBM的混合键合(Hybrid Bonding)技术良率较两年前已显著提升,12层堆叠产品的验证工作已经完成,目前正致力于提升大规模生产的产量。 随着HBM技术的演进,堆叠层数不断增加,工艺复杂性也急剧上升,从而推动了封装技术的持续创新。HBM封装技术已从采

关于「良率」的技术文章、设计资料与工程师讨论,持续更新。

据韩媒thelec最新报道,在4月28日于首尔举行的一场半导体会议上,SK海力士技术负责人金钟勋(Kim Jong-hoon)透露,公司应用于HBM的混合键合(Hybrid Bonding)技术良率较两年前已显著提升,12层堆叠产品的验证工作已经完成,目前正致力于提升大规模生产的产量。 随着HBM技术的演进,堆叠层数不断增加,工艺复杂性也急剧上升,从而推动了封装技术的持续创新。HBM封装技术已从采

在追求极致性能与极小特征尺寸的集成电路制造领域,任何微小的异常均可能导致芯片失效。这些异常,即制造缺陷,是影响最终产品良率、性能与可靠性的直接因素。缺陷并非呈现单一形态,而是在晶圆经历上百道工艺步骤的过程中,不断演化、累积并显现,构成一幅复杂的图景。 一、缺陷分类 前端制程(Front End of Line, FEOL)是集成电路制造中形成晶体管等核心有源器件的阶段。在这一纳米尺度的精密制造过

本文介绍了多重曝光技术对良率的影响。 良率是决定先进制程芯片能不能卖、赚不赚钱的核心,从来不是制造端一个环节的事,从设计、光刻、架构到封装,全链路都是博弈。 摩尔定律走到下半场,拼的不是谁能做更小的晶体管,而是谁能把良率玩明白。 1. 先搞懂:良率到底是怎么算出来的 先给良率一个人话定义:一片晶圆上能通过测试的合格芯片,除以总芯片数,这个比值就是良率。 良率损失本质上就三个来源:工艺偏差、设计限制