PCB画板有瓶颈?蛇形走线你真的会用吗?速看这篇干货教程!

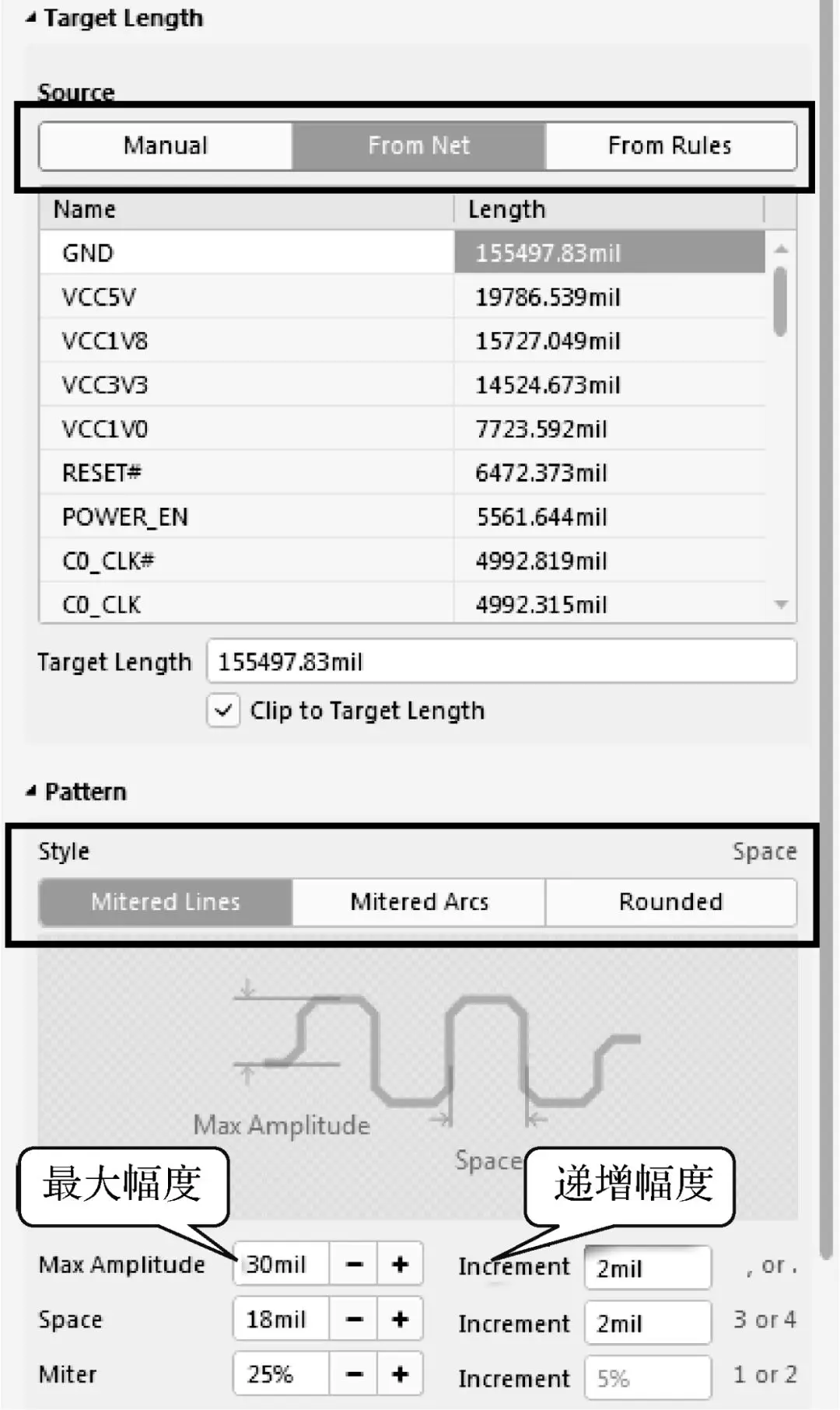

在高速PCB设计中,时序控制与信号完整性变得愈发重要。你是否也曾面对总线时序不匹配的烦恼?有没有想过“蛇形走线”不仅是个美观技巧,更是一门高效提升性能的实战技能? 今天我们就以Altium Designer中的单端与差分蛇形等长走线技巧为例,手把手教你掌握这项必备技能!每一步配图对应,让你看得懂、学得会! 单端蛇形走线,时序控制第一步 在高速并行总线(如DDR SDRAM)设计中,由于多个数据信号

关于「信号完整性」的技术文章、设计资料与工程师讨论,持续更新。

在高速PCB设计中,时序控制与信号完整性变得愈发重要。你是否也曾面对总线时序不匹配的烦恼?有没有想过“蛇形走线”不仅是个美观技巧,更是一门高效提升性能的实战技能? 今天我们就以Altium Designer中的单端与差分蛇形等长走线技巧为例,手把手教你掌握这项必备技能!每一步配图对应,让你看得懂、学得会! 单端蛇形走线,时序控制第一步 在高速并行总线(如DDR SDRAM)设计中,由于多个数据信号

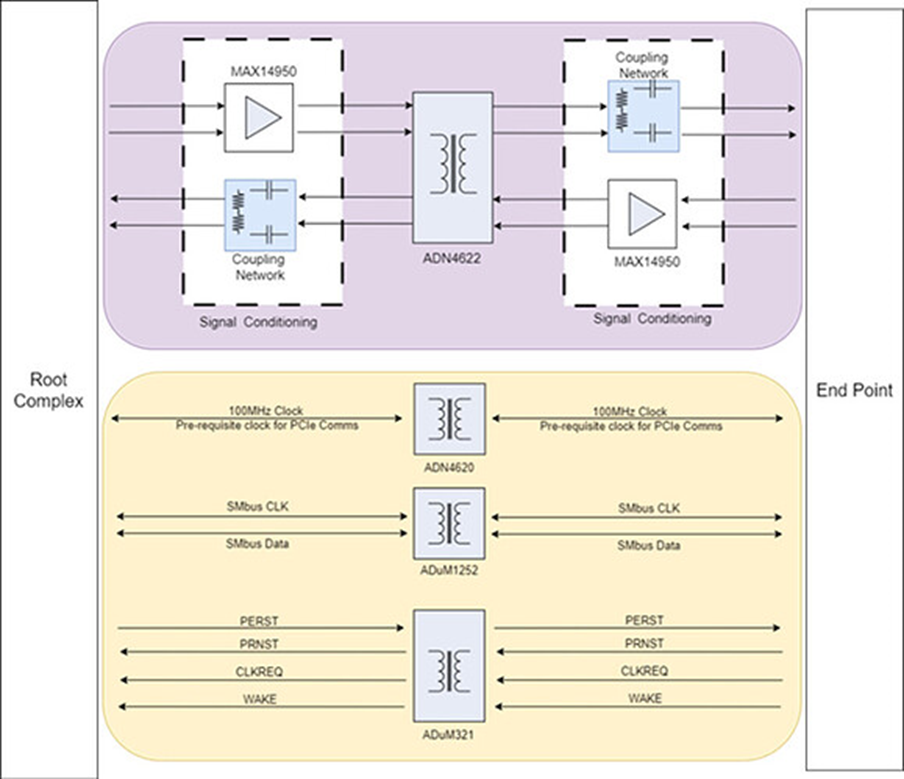

文章**概述** 工业与高可靠性领域,实现 PCI Express(PCIe)接口的电气隔离对于系统的抗噪声、可靠性、接地分离以及安全要求至关重要。ADI(Analog Devices)提供基于 Giga‑Speed 隔离技术的完整方案,可满足 PCIe Gen 1 高速链路的隔离需求,并确保信号完整性(SI)与协议兼容性。 ADN4622BRNZ:PCIe Gen 1 LVDS 链路隔离核心器件

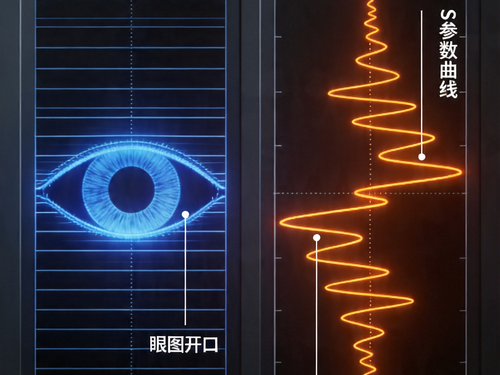

说出来你可能不信,很多工程师拿着漂亮的仿真报告,实物一测试,问题全出来了。返工、延期、挨骂,样样都逃不掉。 归根结底,大多数问题都出在仿真方法上。今天就来聊聊信号完整性仿真中,90%的工程师都在犯的几个错误。 错误一:时域仿真和频域仿真傻傻分不清 有些工程师做仿真,要么只跑时域,要么只跑频域,觉得跑一个就够了。这其实是个大坑。 时域仿真告诉你的是:信号长什么样、眼图开多大、有没有出现过冲下冲。就像

一、基础理论知识 1)电路分析基础(李瀚荪),这本书是教材,对于底子薄的同学,还是建议先看看的,主要是一些电路分析的定理、转换方式等。 2)像微机原理、线性电子电路、非线性电子电路、高频电子线路这些教材都建议看看。 二、数字电路设计 推荐《数字电子技术基础》(第六版,阎石),数字电路基础是电子专业必修课,高校教材内容也都是大差不差的,也可以看华成英的第五版。 如果是走FPGA/CPLD路线,需要学

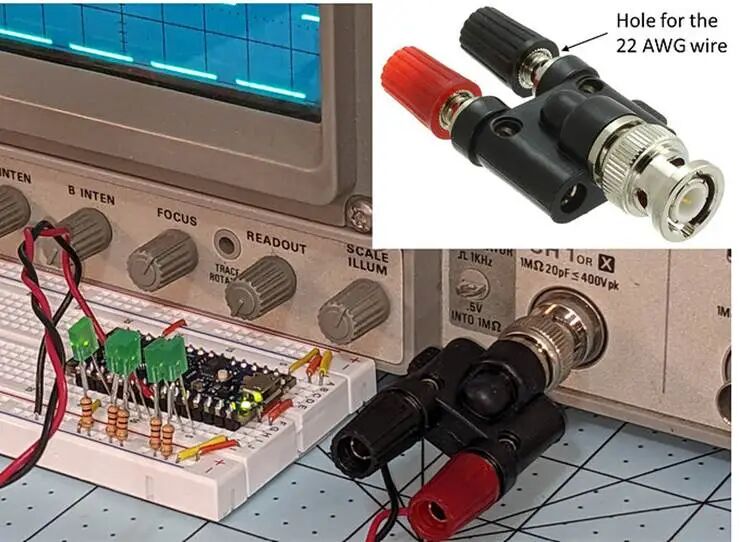

文章**概述** 在使用无焊面包板进行原型开发时,我们常需要将电路连接到示波器、频谱仪或函数发生器进行测试。传统做法是直接使用示波器探头或带鳄鱼夹的测试线,但在面包板上,这种方式往往既笨拙又不可靠。 为什么示波器探头不适合面包板? 问题并非出在探头设计,而是 探头设计初衷与面包板使用场景完全不匹配。 面包板接触压力低,插孔松紧不均。 示波器探头弹性夹子和探针有一定的“抓拉力”。 在调试过程中频繁移

在智能制造的浪潮下,工业自动化正经历着深刻变革。在生产现场忙碌的机器设备,已经与无处不在的传感器,以及算力日趋强大的控制中心整合在一起,构成一个数据驱动的高密度、模块化和分布式的自动化系统,实现前所未有的高效率和灵活性。 这一趋势正在重塑工业自动化的底层技术逻辑,自然也包括作为自动化系统神经中枢的控制柜,进而对高性能、高可靠性的柜内互连,也提出了更严苛要求。 具体来讲,工业自动化柜内互连方案面临着