文章**概述**

工业与高可靠性领域,实现 PCI Express(PCIe)接口的电气隔离对于系统的抗噪声、可靠性、接地分离以及安全要求至关重要。ADI(Analog Devices)提供基于 Giga‑Speed 隔离技术的完整方案,可满足 PCIe Gen 1 高速链路的隔离需求,并确保信号完整性(SI)与协议兼容性。

ADN4622BRNZ:PCIe Gen 1 LVDS 链路隔离核心器件

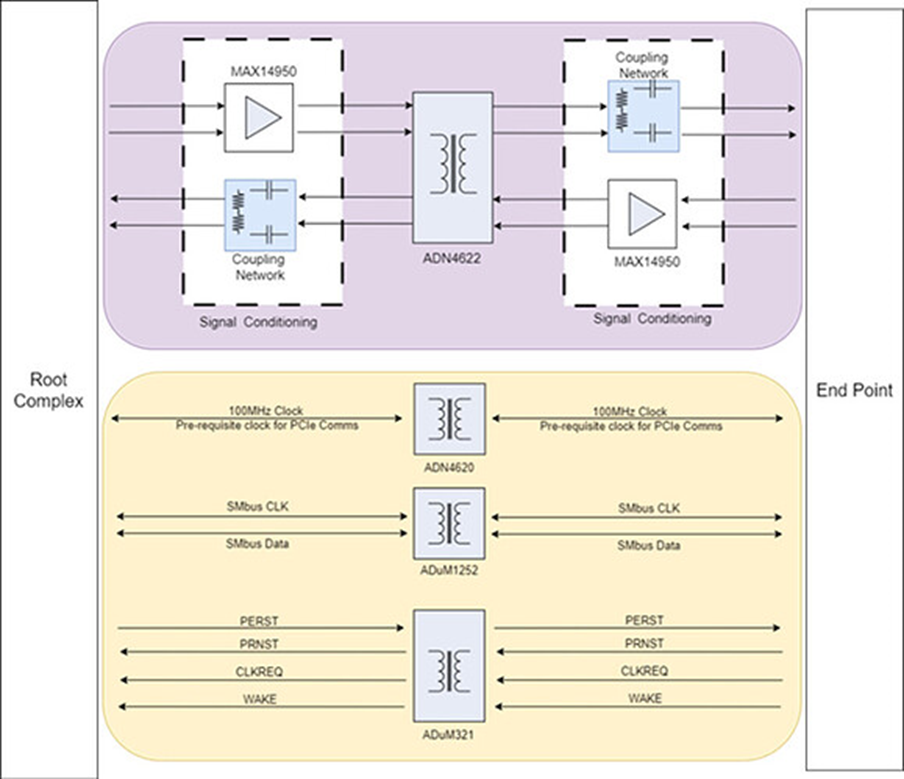

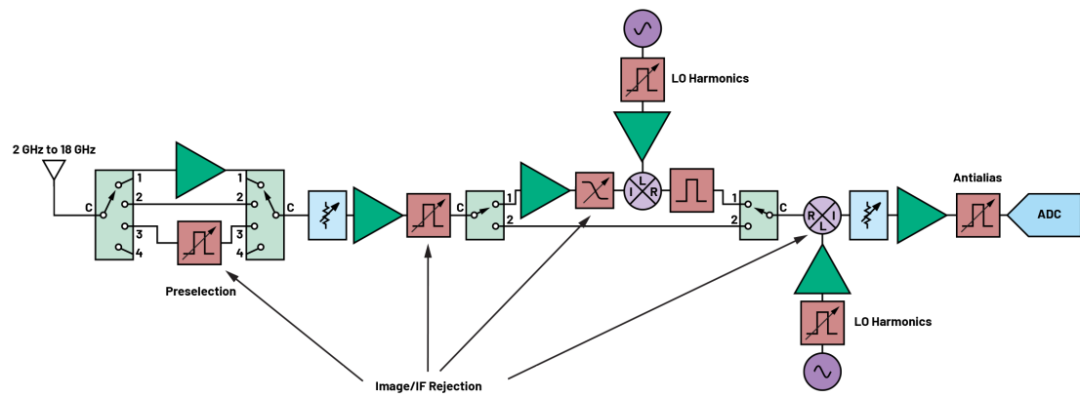

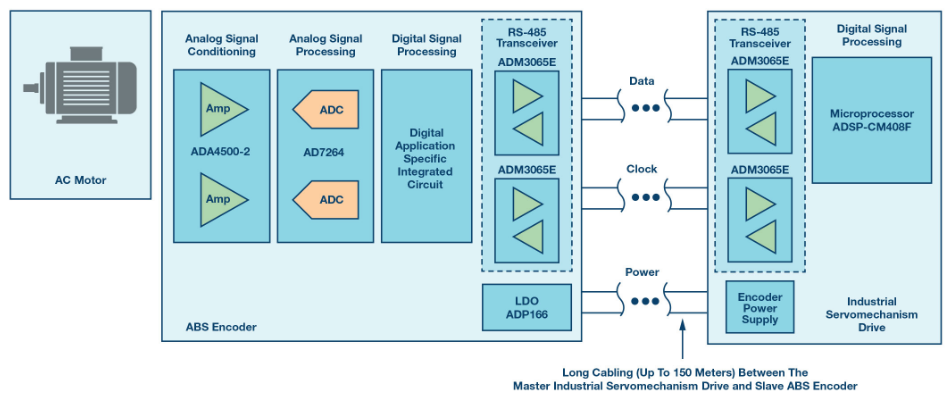

需考虑PCIe信号组成,确保完全支持协议的关键行为。需通过ADN4622BRNZ实现电平转换以支持信号传输,电气空闲支持则确保空闲状态传递。如图1所示,这通过ADN4622BRNZ每个输入输出端的耦合网络模块实现。

*图1:采用ADI隔离技术的PCIe Gen 1*接口隔离方案

MAX14954**:**高速链路的均衡与信号完整性补偿

除耦合网络外,MAX14954PCIe重驱动器采用均衡技术提升信号完整性。

由于高速差分信号在 PCB 走线、连接器与隔离屏障间会出现:

-

高频损耗

-

插损

-

回损

-

抖动累积

因此需要在隔离链路中加入 MAX14954 PCIe 重驱动器(Redriver)。

MAX14954 通过:

-

输入均衡

-

输出摆幅与预加重调节

-

直通延迟优化

可显著改善 SERDES 信号眼图质量,提高链路训练成功率,确保 BER 满足 PCIe 规范。

REFCLK(100 MHz)隔离:ADN4620BRSZ-RL

PCIe 的数据链路必须依赖 100 MHz 参考时钟(REFCLK) 进行同步。REFCLK 的抖动性能直接影响:

-

链路初始化

-

PLL 锁定能力

-

SERDES 的整体 jitter budget

ADN4620BRSZ-RL 支持:

-

100 MHz LVDS / HCSL 等类型时钟隔离

-

超低抖动传输路径

-

对 SSC(Spread-Spectrum Clocking)完全兼容

因此可作为 PCIe 系统中时钟隔离的优选解决方案。

SMBus / I**²**C 系统管理信号隔离:ADuM1252AUA+T

PCIe 系统管理多采用 SMBus(I²C 兼容)进行:

-

板级监控

-

温度、电压、设备状态读取

-

电源管理通信(PMBus 系统中常见)

ADuM1252AUA+T 是双向 I²C 隔离器,负责与系统设备间传递信息,可隔离信号,适用于隔离 PCIe 平台中的系统管理总线。

电源隔离:LT8302ES8E#TRPBF

尽管图 1 未展示完整电源隔离结构,但在 PCIe 隔离系统中,需要提供隔离侧的独立电源。

LT8302 作为隔离式反激控制器,可:

-

直接在隔离屏障两侧生成独立供电

-

减少磁性元件尺寸

-

支持高效率、低噪声隔离电源设计

保证整个隔离链路的安全性与抗干扰性能。

结论

本文探讨了工业环境中如何隔离PCIe Gen1协议。该方案也适用于其他需要隔离以满足鲁棒性、噪声和防护要求的终端应用。通过复制图1中的Gigaspeed部分,可轻松扩展至更高通道宽度。

评论区

登录后即可参与讨论

立即登录