PCB画板有瓶颈?蛇形走线你真的会用吗?速看这篇干货教程!

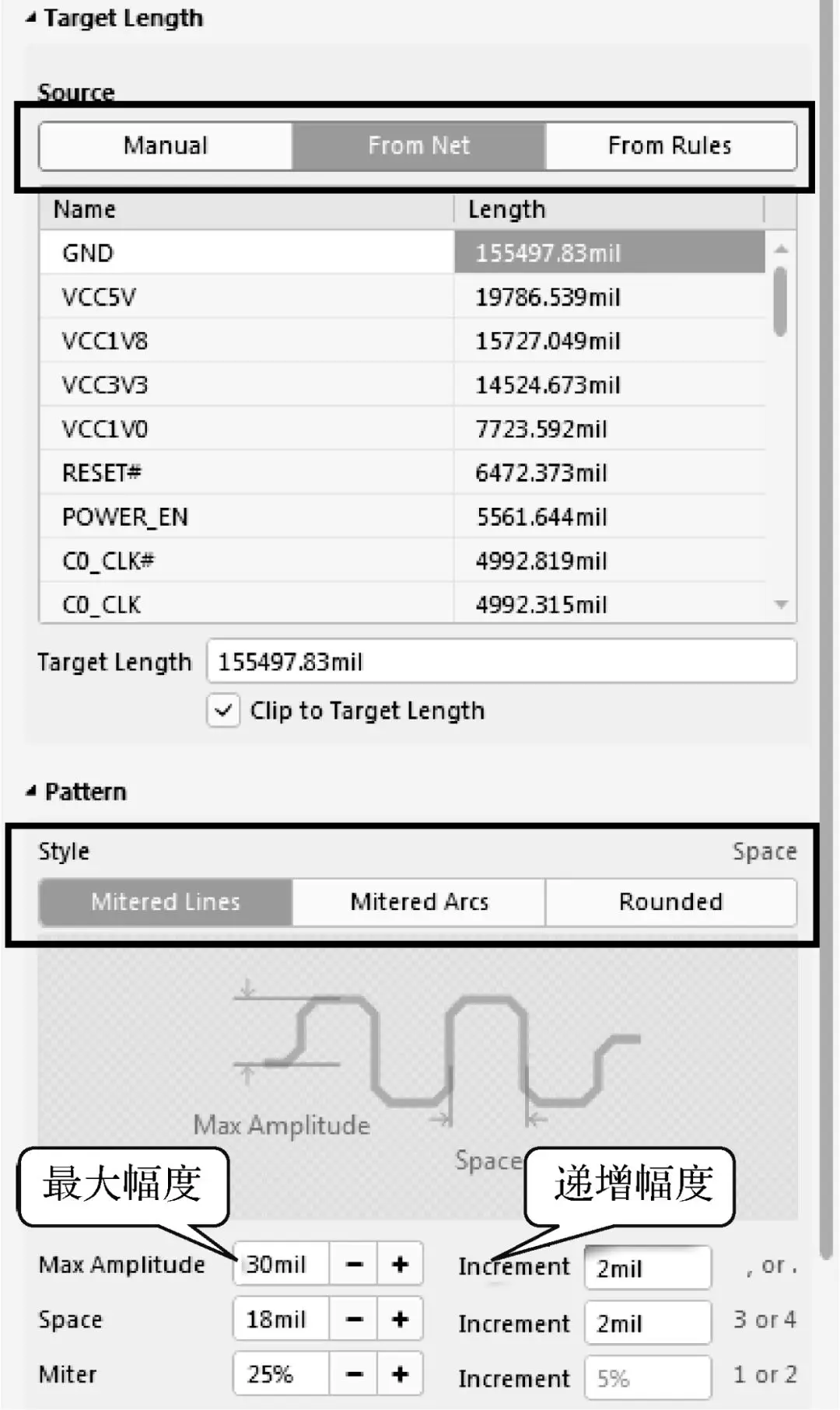

在高速PCB设计中,时序控制与信号完整性变得愈发重要。你是否也曾面对总线时序不匹配的烦恼?有没有想过“蛇形走线”不仅是个美观技巧,更是一门高效提升性能的实战技能? 今天我们就以Altium Designer中的单端与差分蛇形等长走线技巧为例,手把手教你掌握这项必备技能!每一步配图对应,让你看得懂、学得会! 单端蛇形走线,时序控制第一步 在高速并行总线(如DDR SDRAM)设计中,由于多个数据信号

关于「信号完整性」的技术文章、设计资料与工程师讨论,持续更新。

在高速PCB设计中,时序控制与信号完整性变得愈发重要。你是否也曾面对总线时序不匹配的烦恼?有没有想过“蛇形走线”不仅是个美观技巧,更是一门高效提升性能的实战技能? 今天我们就以Altium Designer中的单端与差分蛇形等长走线技巧为例,手把手教你掌握这项必备技能!每一步配图对应,让你看得懂、学得会! 单端蛇形走线,时序控制第一步 在高速并行总线(如DDR SDRAM)设计中,由于多个数据信号

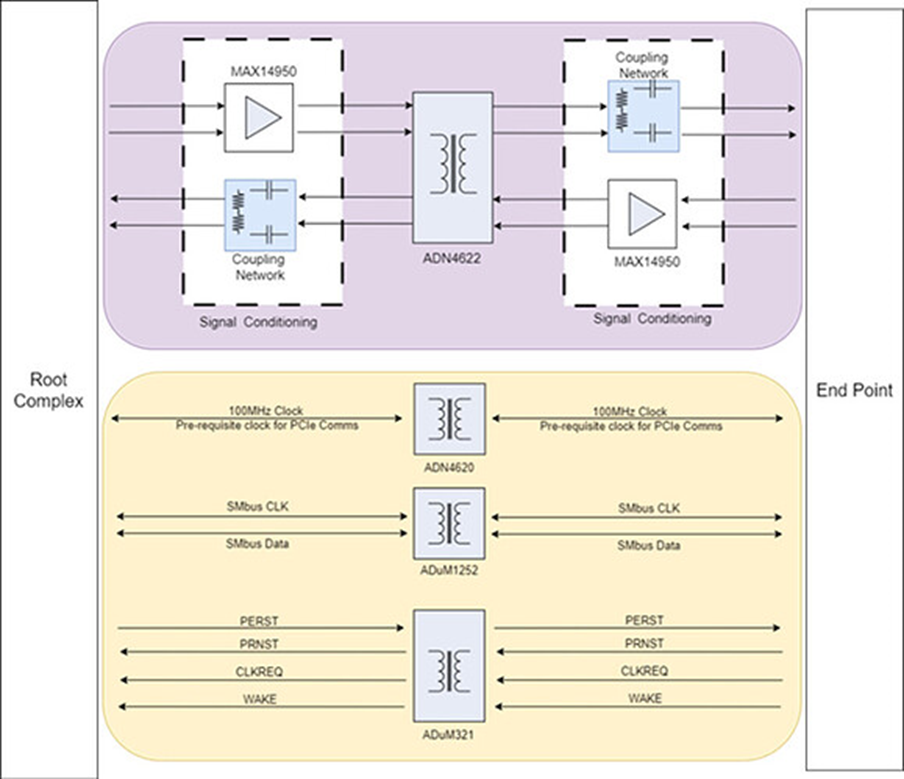

文章**概述** 工业与高可靠性领域,实现 PCI Express(PCIe)接口的电气隔离对于系统的抗噪声、可靠性、接地分离以及安全要求至关重要。ADI(Analog Devices)提供基于 Giga‑Speed 隔离技术的完整方案,可满足 PCIe Gen 1 高速链路的隔离需求,并确保信号完整性(SI)与协议兼容性。 ADN4622BRNZ:PCIe Gen 1 LVDS 链路隔离核心器件

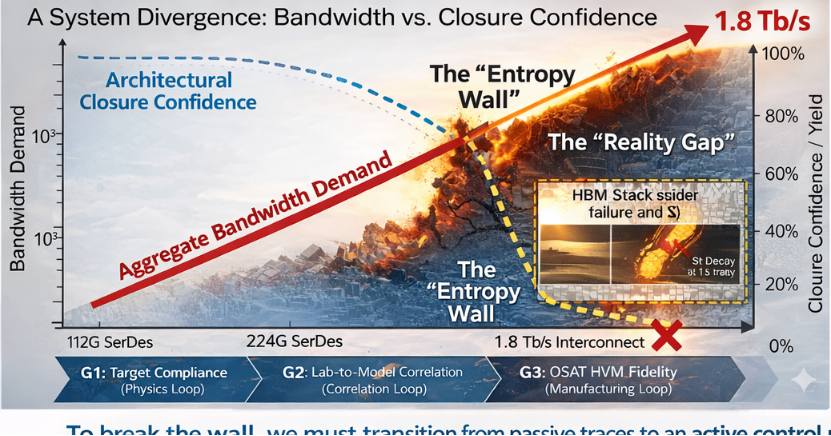

当英伟达 Blackwell 架构以 NVLink 5 将 GPU-GPU 互联带宽推至1.8Tb/s(14.4Tbps),AI 超算正式迈入 “万亿参数级训练” 的新纪元——单颗GPU的芯片间带宽达到PCIe 5.0的35倍、Hopper NVLink 4的2倍,支撑72颗 GPU 集群每秒处理数 PB 级数据流动。但这一带宽革命并非性能的线性跃升,而是将电子系统设计推向物理极限的临界点:信号完

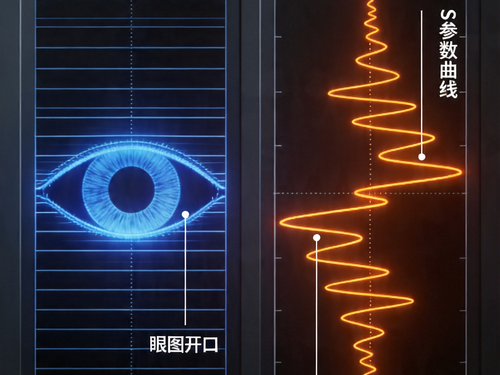

说出来你可能不信,很多工程师拿着漂亮的仿真报告,实物一测试,问题全出来了。返工、延期、挨骂,样样都逃不掉。 归根结底,大多数问题都出在仿真方法上。今天就来聊聊信号完整性仿真中,90%的工程师都在犯的几个错误。 错误一:时域仿真和频域仿真傻傻分不清 有些工程师做仿真,要么只跑时域,要么只跑频域,觉得跑一个就够了。这其实是个大坑。 时域仿真告诉你的是:信号长什么样、眼图开多大、有没有出现过冲下冲。就像

一、基础理论知识 1)电路分析基础(李瀚荪),这本书是教材,对于底子薄的同学,还是建议先看看的,主要是一些电路分析的定理、转换方式等。 2)像微机原理、线性电子电路、非线性电子电路、高频电子线路这些教材都建议看看。 二、数字电路设计 推荐《数字电子技术基础》(第六版,阎石),数字电路基础是电子专业必修课,高校教材内容也都是大差不差的,也可以看华成英的第五版。 如果是走FPGA/CPLD路线,需要学

去年的帖子,需要的同学做个参考。 测评 测评大概接近100道题,性格测试和行测题(约20道,基本上都是逻辑推理题)混合在一起。 笔试 所有岗位同一个时间,我做的是A卷,硬件笔试是90分钟,题目类型有单选、多选、填空、简答和计算题,一共100分。 题目主要涉及的知识点:通信协议(SPI、IIC、UART等)、开关电源、信号完整性、分立元件参数性能(MOS、BJT、PN结等)个人感觉以上4方面

在汽车电子电气架构由分布式电子控制单元(ECU)走向域控制单元(Domain Control Unit, DCU)的演进过程中,连接器已不再只是“电气连接接口”,而是攸关系统可靠性、数据传输能力、功能安全与整车可制造性的关键元器件。本文将为您介绍连接器在汽车DCU中所扮演的核心角色,以及Molex(莫仕)DuraClik连接器的产品特性与优势。 连接器在汽车域控制单元中 扮演的关键角色 从系统层

本期 DigiKey向大家推介一款产品——Molex EMI 滤波高性能D-Sub Pi 适配器和连接器 Molex EMI 滤波 D-sub pi 适配器和连接器提供了可靠的解决方案,可减轻苛刻环境中的电磁干扰 (EMI),例如军用和商用飞机中的发动机控制、机载无线电、成像设备、过程设备等。 这些连接器采用紧凑的设计,增强了信号完整性 (SI) 并符合监管标准,简化了实施,同时提高了整体性能和可

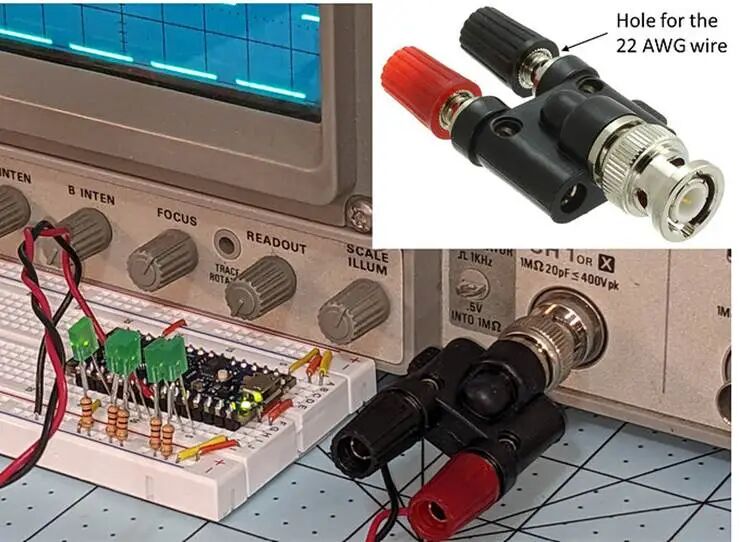

文章**概述** 在使用无焊面包板进行原型开发时,我们常需要将电路连接到示波器、频谱仪或函数发生器进行测试。传统做法是直接使用示波器探头或带鳄鱼夹的测试线,但在面包板上,这种方式往往既笨拙又不可靠。 为什么示波器探头不适合面包板? 问题并非出在探头设计,而是 探头设计初衷与面包板使用场景完全不匹配。 面包板接触压力低,插孔松紧不均。 示波器探头弹性夹子和探针有一定的“抓拉力”。 在调试过程中频繁移

云计算、物联网、VR/AR、数字孪生、人工智能(AI)……这些让科技圈热血沸腾的技术背后,都有一个共同的底层逻辑——它们都是以海量数据的处理作为支撑的。因此,无论是哪条赛道上的竞争,都会体现为数字基础设施建设上的比拼,即新一代数据中心的设计和部署。 数据中心的建设作为一个系统工程,面临着来自各个方面的挑战,比如高性能计算、电力供应、网络安全等等,而高速互连技术也是其中至关重要的一环,它为数据在规模

在智能制造的浪潮下,工业自动化正经历着深刻变革。在生产现场忙碌的机器设备,已经与无处不在的传感器,以及算力日趋强大的控制中心整合在一起,构成一个数据驱动的高密度、模块化和分布式的自动化系统,实现前所未有的高效率和灵活性。 这一趋势正在重塑工业自动化的底层技术逻辑,自然也包括作为自动化系统神经中枢的控制柜,进而对高性能、高可靠性的柜内互连,也提出了更严苛要求。 具体来讲,工业自动化柜内互连方案面临着