在高速PCB设计中,时序控制与信号完整性变得愈发重要。你是否也曾面对总线时序不匹配的烦恼?有没有想过“蛇形走线”不仅是个美观技巧,更是一门高效提升性能的实战技能?

今天我们就以Altium Designer中的单端与差分蛇形等长走线技巧为例,手把手教你掌握这项必备技能!每一步配图对应,让你看得懂、学得会!

单端蛇形走线,时序控制第一步

在高速并行总线(如DDR SDRAM)设计中,由于多个数据信号需要同步采样,因此必须实现精确的时序匹配。这时候,蛇形等长走线应运而生!

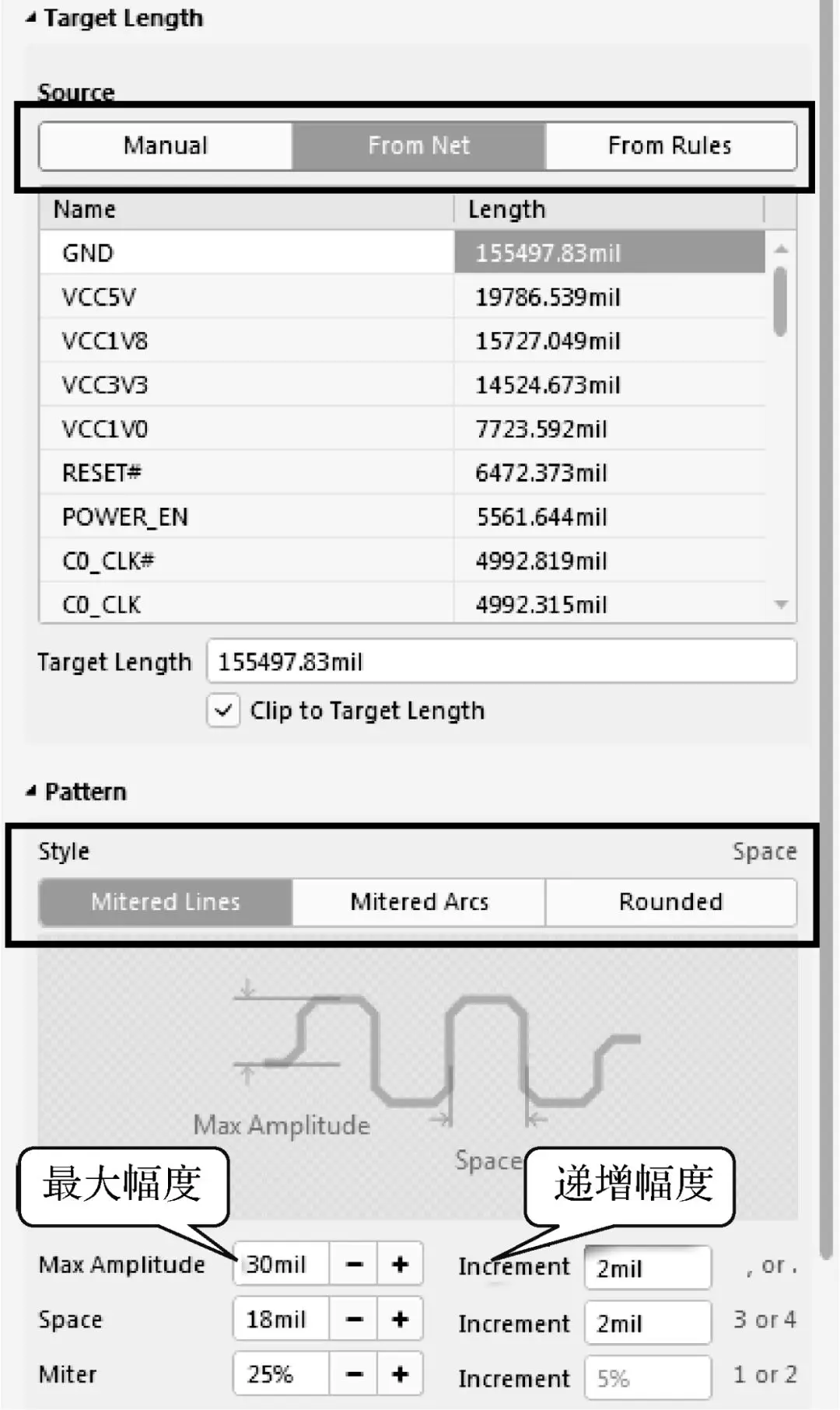

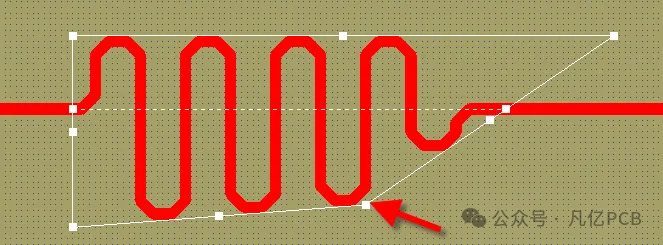

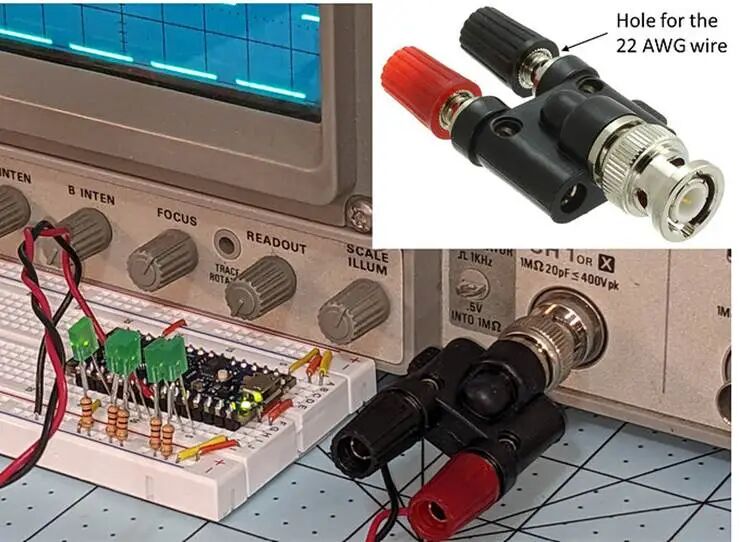

如图1所示:单端蛇形线参数设置

等长绕线建议先建立网络类并完成基础布线。之后,通过快捷键 UR 激活等长命令。

🔍 参数详解:

- Target Length

设置目标长度(手动、基于网络类、或设计规则)

- Pattern 模式

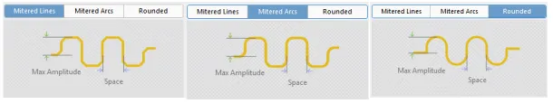

选择线条类型:斜线条(推荐)、斜弧、半圆(图10-106)

- Max Amplitude

蛇形线最大幅度,建议逐步递增设置为2mil(图10-107)

- Space 间距

建议遵守3W规则,同样可调增量为2mil

图2 斜线条、斜弧与半圆等长模式

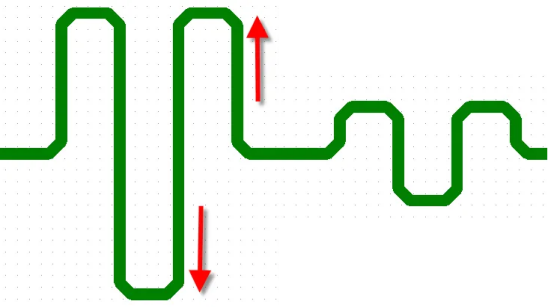

图3 蛇形线及蛇形幅度递增

操作技巧提升效率

滑动鼠标生成蛇形线

使用键盘 > 和 < 可实时调整蛇形幅度(每次按下为2mil递增/递减)

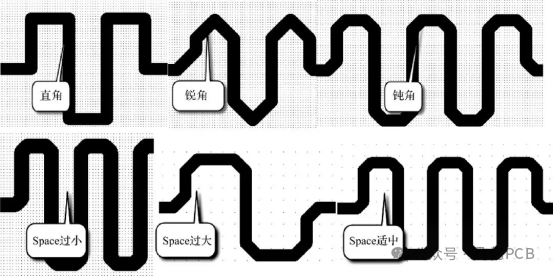

图4:拐角及Space调整技巧

数字键盘:

1:减小拐角幅度

2:增大拐角幅度

3:减小线间距

4:增大线间距

图中示例展示直角、锐角、钝角的调整效果

图4 等长的直角、锐角、钝角及等长的Space调整

后期微调更灵活

即使已经完成蛇形绕线,也可以继续优化!

图5:调整蛇形结构点击走线段,拖动“小点”调整蛇形形状,灵活修正不理想区域。

图5 蛇形线的调整

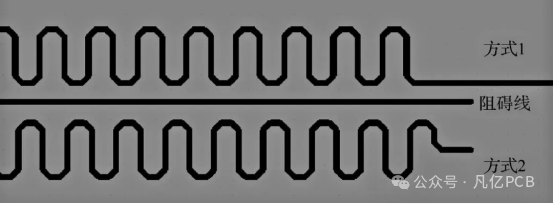

提效小技巧:阻碍线助力单边蛇形

在蛇形线另一侧放置阻碍线,可强制走线集中在一侧,节省空间。完成后删除阻碍线即可。图6-利用阻碍线优化空间

图6 阻碍线的使用

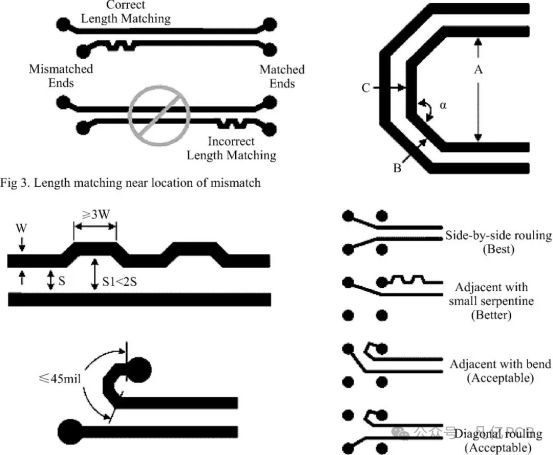

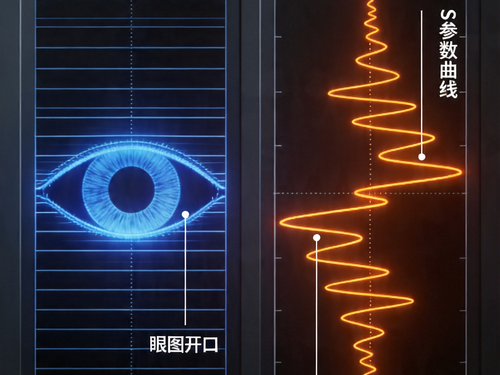

差分信号也能“蛇形”处理!

对于串行差分信号(如USB、SATA、PCIe),虽然没有同步采样要求,但为了保持差分信号完整性和阻抗匹配,差分对等长布线也不可或缺!

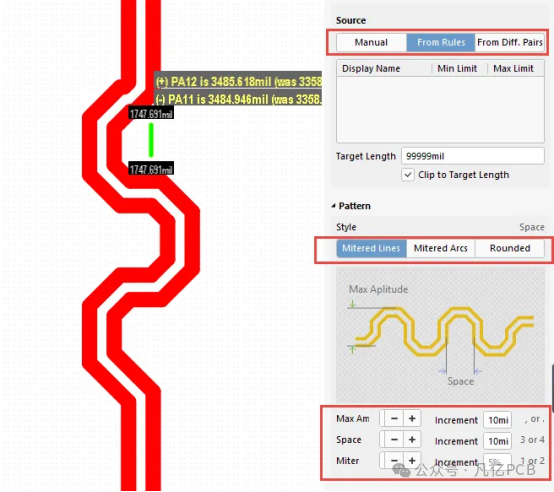

📌 图7:差分蛇形线参数设置

快捷键 UP 启动“差分对网络等长调节”,设置方式与单端蛇形类似。

图7 差分蛇形线参数设置

差分对内等长处理建议:

使用普通单端绕线方式对一条线绕线

误差控制在 5mil 内

图8 常见差分对内等长方式

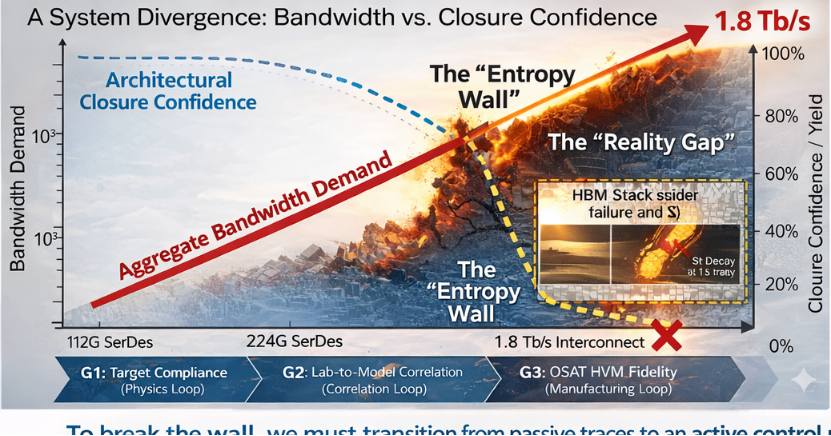

总结:走线美感 VS 性能,如何两者兼得?

通过以上图文讲解,你是否已经掌握了Altium Designer中的蛇形走线核心技巧?不论是单端高速总线,还是差分高速信号——合理等长布线+灵活调节技巧,才是打破“设计瓶颈”的关键!

评论区

登录后即可参与讨论

立即登录