对照一下 你是否误解了变压器初级 / 次级阻抗?

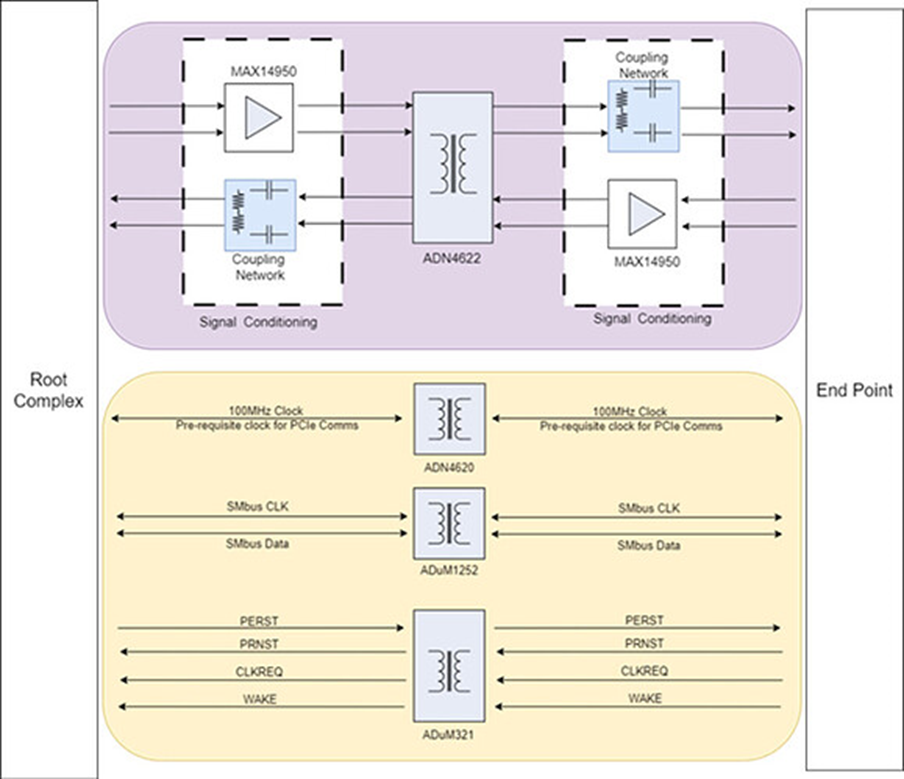

文章**概述** 工业与高可靠性领域,实现 PCI Express(PCIe)接口的电气隔离对于系统的抗噪声、可靠性、接地分离以及安全要求至关重要。ADI(Analog Devices)提供基于 Giga‑Speed 隔离技术的完整方案,可满足 PCIe Gen 1 高速链路的隔离需求,并确保信号完整性(SI)与协议兼容性。 ADN4622BRNZ:PCIe Gen 1 LVDS 链路隔离核心器件

关于「PCIe」的技术文章、设计资料与工程师讨论,持续更新。

文章**概述** 工业与高可靠性领域,实现 PCI Express(PCIe)接口的电气隔离对于系统的抗噪声、可靠性、接地分离以及安全要求至关重要。ADI(Analog Devices)提供基于 Giga‑Speed 隔离技术的完整方案,可满足 PCIe Gen 1 高速链路的隔离需求,并确保信号完整性(SI)与协议兼容性。 ADN4622BRNZ:PCIe Gen 1 LVDS 链路隔离核心器件

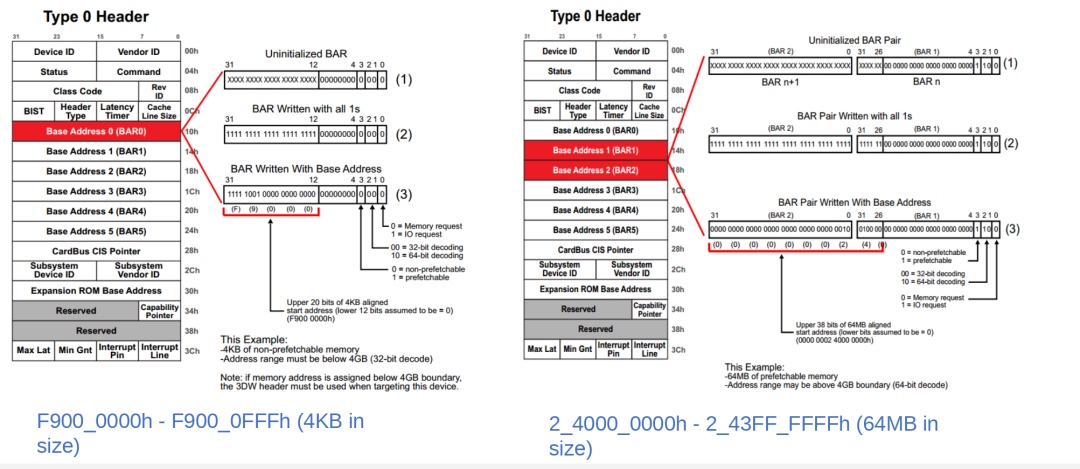

前言 对于主机而言,FPGA-PCIe 设备通过其 BAR(Base Address Register)被识别和访问。主机必须通过读写 BAR 所映射的地址空间,才能与 FPGA-PCIe 正确通信。这相当于将 FPGA-PCIe 内部的地址区域映射到主机的内存空间中,主机通过访问这段内存来完成数据收发。 readl(dif->bar0_mapped_addr + (offset<&l

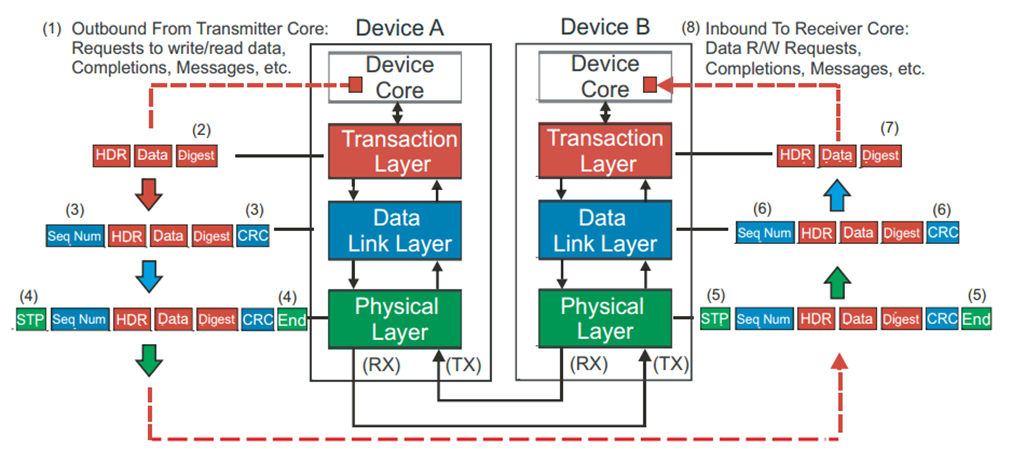

前言 本系列不会从零讲PCIe,也不会照搬规范条款,标准文档已经够厚,这里更像是一份工程师视角下的PCIe手边笔记 , 以更简洁的方式记录PCIe的关键点。 TLP包 由于PCIe-DMA的实现始终在事务层通过TLP包完成,因此深入理解TLP包的构成至关重要。 TLP包所在位置 在PCIe协议的传输层中,TLP包的结构相较于链路层与物理层的报文而言,最为简单清晰。 TLP的结构 TLP的结构