sv基础:timescale、timeunit、timeprecision

1. 前言 Verilog/System verilog 仿真中的时间单位/时间精度设置是保证仿真设置正确的重要手段,但是很多场景下却常常被忽视。设置不合理会导致诸多问题,例如延时不准确,时钟周期不对,打印信息不准确,验证用例耗费的时间特别长,多模块配合无法发现隐藏的问题。 因此,本文件将描述timescale、timeunit、timeprecision等概念,并描述如何正确地使用timesca

关于「Verilog」的技术文章、设计资料与工程师讨论,持续更新。

1. 前言 Verilog/System verilog 仿真中的时间单位/时间精度设置是保证仿真设置正确的重要手段,但是很多场景下却常常被忽视。设置不合理会导致诸多问题,例如延时不准确,时钟周期不对,打印信息不准确,验证用例耗费的时间特别长,多模块配合无法发现隐藏的问题。 因此,本文件将描述timescale、timeunit、timeprecision等概念,并描述如何正确地使用timesca

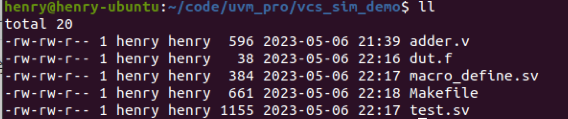

我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。 源文件内容如下: //adder.v module adder( input clk, input rst, input [9:0] A, input [9:0] B, output reg [10:0] C ); always @ ( pose

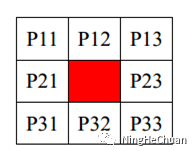

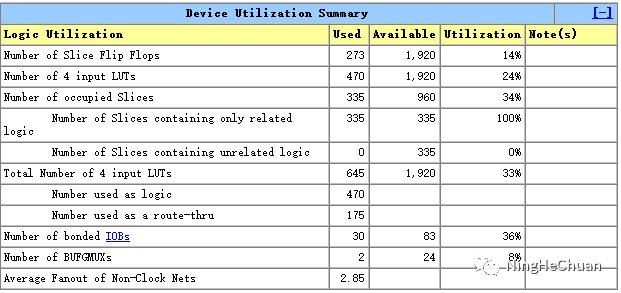

前面实现了基于FPGA的彩色图像转灰度处理,减小了图像的体积,但是其中还是存在许多噪声,会影响图像的边缘检测,所以这一篇就要消除这些噪声,基于灰度图像进行图像的滤波处理,为图像的边缘检测做好夯实基础。 椒盐噪声(salt & pepper noise)是数字图像的一个常见噪声,所谓椒盐,椒就是黑,盐就是白,椒盐噪声就是在图像上随机出现黑色白色的像素。椒盐噪声是一种因为信号脉冲强度引

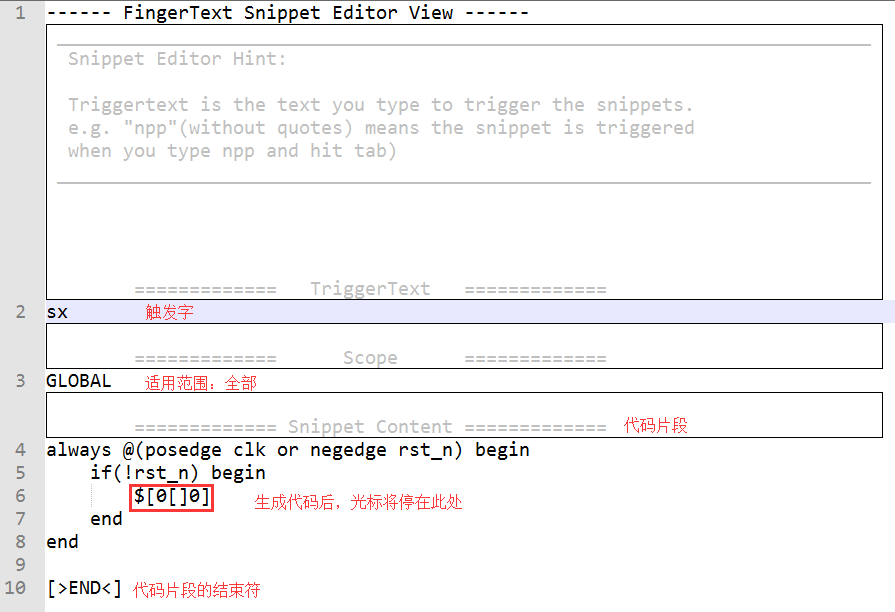

版本:Notepad++ 7.6.6 ,32位 //======================================================================== //== 安装与Verilog设置 //========================================================================

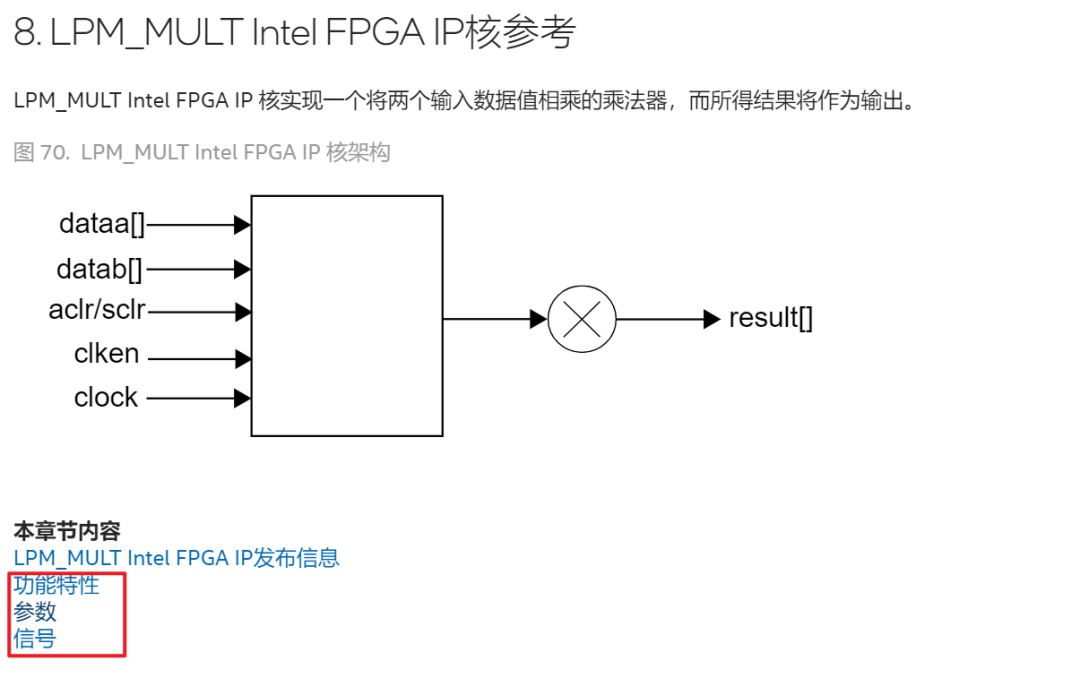

在进行编码时,我们时常会使用到乘法器,除法器,等较复杂功能模块,为此fpga vendor设计定制了IP核,用户通过调用IP核来实现所需功能,耗费资源少且利于时序收敛。我们在日常verilog编码过程期望通过参数化的方式调用IP核。例如IP的位宽,时延,部分关键特性期望可以通过参数调用的方式实现,而不是通过打开GUI界面通过手动选择的方式实现。其实实现方式很简单。首先通过手动打开quart

在讲脚本前,根据小艾的经历,有必要介绍一下文本编辑器。 这个说起来不是个难事,但是对于刚使用linux的同学而言,编辑文本还真是个问题,首先,你很难找到写字板,就算找到了,也很难用,我说的没错吧。😄 所以,你必须改变,就从现在开始! Linux平台上一直有两派,争执不下,一个是emacs,另一个就是vim 他们两个都是很好的文本编辑器,但由于开发初衷不一样。 前者大约于1975在MIT诞生,他是一

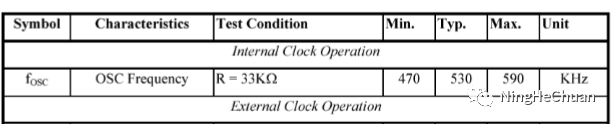

前言 在做这个实验的时候在网上找了许多资料,都是关于使用单片机驱动LCD显示,确实用单片机驱动是要简单不少,记得在FPGA学习交流群里问问题的时候,被前辈指教,说给我最好的指教便是别在玩这个了,多看看关于FPGA方面的书籍,比做这个单片机做的东西价值强多了。现在想来确实,自从学习FPGA以来,看过的书没有多少,只是想做个什么了,就在网上找找例程,照抄下来,把算法推理一遍,下个板子实现

当你第一次接触Verilog时,很容易把它当成C或Java这样的编程语言。这是一个常见的误区,也是入门路上的第一个坎。Verilog不是一种编程语言,而是一种硬件描述语言。 你的角色不是“写程序”,而是在“画图纸”——用代码的形式描述一个数字电路应该长什么样。 一、核心思想:你是在描述电路 在开始写代码之前,请务必建立这个思维模型: 软件程序:是指令的序列,在CPU上按时间顺序执行。 硬件描述

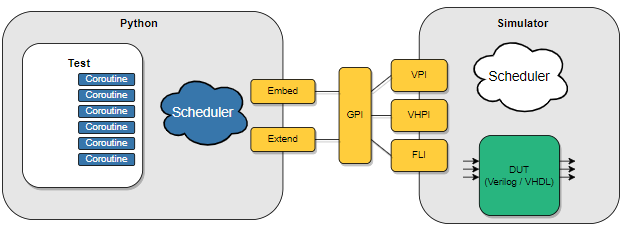

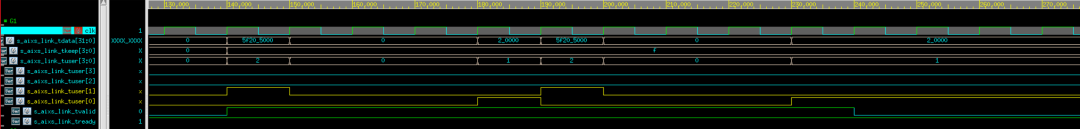

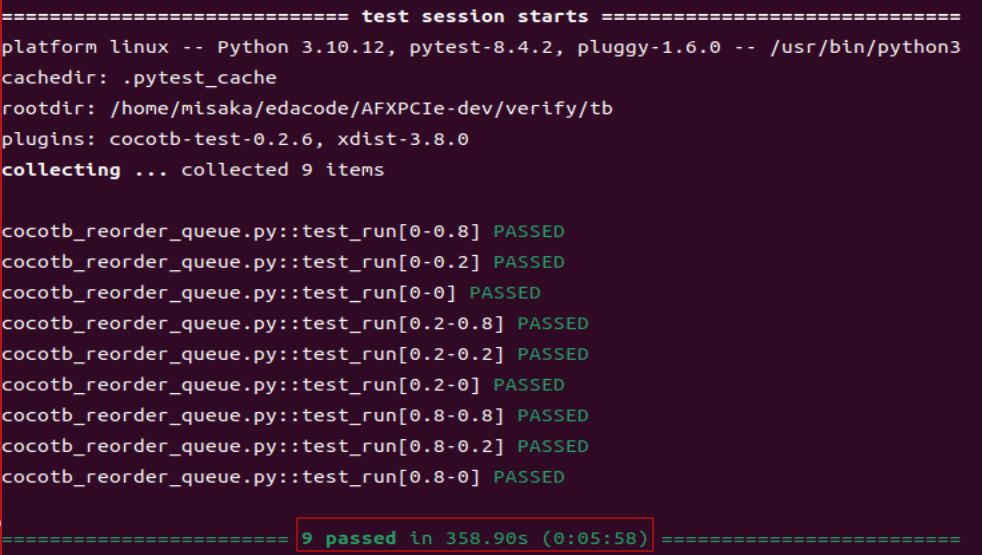

很多FPGA/IC工程师擅长设计,但在仿真方面较为薄弱。我认为主要问题在于,完整的仿真实现学习成本较高,如学习UVM需要掌握大量新的内容。而单纯使用Verilog自仿又难以满足需求,以报文仿真为例,我们需要解析报文,若仅依赖Verilog自仿,就相当于要自己编写一个报文解析模块,工作量非常庞大。而Python在数据处理方面则更加高效,如果加以利用,完全可以快速构建一个完整的仿真模型。Cocotb

前言 自从学习FPGA以来,唯一做过的完整系统就是基于basys2得多功能数字表。记得当时做的时候也没少头疼,最后用时间磨出来了一个不是很完整的小系统,当时还是产生了满满的成就感。现在回头看来,先不说功能实现的如何,首先代码书写满是不规范,其中犯得最多的一个问题就是把verilog当C来写。所以,我决定趁着寒假自由支配的时间比较多,决定重写多功能数字时钟,算是对我大二第一学期以来

1前言 很多FPGA/IC工程师擅长设计,但在仿真方面较为薄弱。我认为主要问题在于,完整的仿真实现学习成本较高,如学习UVM需要掌握大量新的内容。而单纯使用Verilog自仿又难以满足需求,以报文仿真为例,我们需要解析报文,若仅依赖Verilog自仿,就相当于要自己编写一个报文解析模块,工作量非常庞大。而Python在数据处理方面则更加高效,如果加以利用,完全可以快速构建一个完整的仿真模型。Coc

一、标识符与注释 前面已经说到,模块名的定义要符合标识符的定义,那么什么是标识符呢?它的语法是什么呢? ①标识符是赋给对象的唯一名称,通过标识符可以提及相应的对象,Verilog语法将对转义标识符中的字符逐个处理。 ②标识符可以是字母、数字、下划线和美元符$的组合,并且标识符的第一个字母必须是字母或者是下划线。此外,在Verilog的标识符中,是区分大小写的。 ③Verilog中有一些关键字,简

前言 在上一篇文章中,我们提到相同协程是阻塞的,不同协程是并发的这一说法。然而,这种理解存在偏差,所以第一个现象并不像我们之前想象的那样。今天,我们将专门梳理协程的概念,深入剖析其本质,以纠正上次关于协程与阻塞的说明。 案例说明 下面我将介绍一种非常典型的现象 for i in range(2): await device_to_host_source.send(frame) for

前言 在使用 cocotb 编写测试时,很多人可能都会遇到一些让人困惑的现象:比如说,你明明在发送一帧完整数据之后,加了 await RisingEdge(clk) 想等待 5 个周期再发下一帧,但在波形上却发现帧与帧之间并没有间隔;或者你在别的地方加了 Timer 也没起作用更甚至cocotb直接卡住不动了;又或者明明指定了发包数,却提前结束了。 这些现象的背后,其实不是 cocotb 出了问题

一、入门首先要掌握**HDL(HDL=verilog+VHDL**)。 第一句话是:还没学数电的先学数电。然后你可以选择verilog或者VHDL,有C语言基础的,建议选择VHDL。因为verilog太像C了,很容易混淆,最后你会发现,你花了大量时间去区分这两种语言,而不是在学习如何使用它。当然,你思维能转得过来,也可以选verilog,毕竟在国内verilog用得比较多。

对于许多FPGA/IC工程师而言,设计实现游刃有余,验证仿真却常成短板——传统验证方法面临两难困局:学习UVM需投入大量时间成本,而纯Verilog自仿又会陷入重复造轮子的低效循环。以通信协议仿真为例,仅报文解析就需要重写整套解析逻辑,相当于用Verilog再实现一次协议栈,耗时费力。此时,Python的生态优势便锋芒尽显。其丰富的字符串处理库可直接解析报文,配合Cocotb框架,仅需少量Pyth

在数字电路设计的世界里,Verilog不仅是实现功能的工具,更是工程师与工具(综合器、仿真器)、与同事、与未来的自己沟通的桥梁。糟糕的代码风格如同混乱的电路板,线缆缠绕,故障难寻;而优雅的代码风格则像一份精密的施工图,层次清晰,一目了然。它不仅是个人习惯,更是项目成功的第一道防线。 一、结构与可读性:像写文章一样写代码 1. 一致的缩进与格式统一的缩进(建议使用2或4个空格)是代码可读性的基石。