在进行编码时,我们时常会使用到乘法器,除法器,等较复杂功能模块,为此fpga vendor设计定制了IP核,用户通过调用IP核来实现所需功能,耗费资源少且利于时序收敛。我们在日常verilog编码过程期望通过参数化的方式调用IP核。例如IP的位宽,时延,部分关键特性期望可以通过参数调用的方式实现,而不是通过打开GUI界面通过手动选择的方式实现。其实实现方式很简单。首先通过手动打开quartus,采用手动调用的方式选择想要使用的IP核,完成配置后并且产生IP,在生产的例化代码中查看如何配置功能和参数,然后自己按照例化案例模块中的格式编写一个verilog模块将IP包一层,并且关键特性使用参数化。这样就能实现IP核的参数化调用了。

首先通过器件手册获取IP核说明,也可以通过官网查询(https://www.intel.cn/content/www/cn/zh/docs/programmable/683037/23-1/core-references-91023.html)

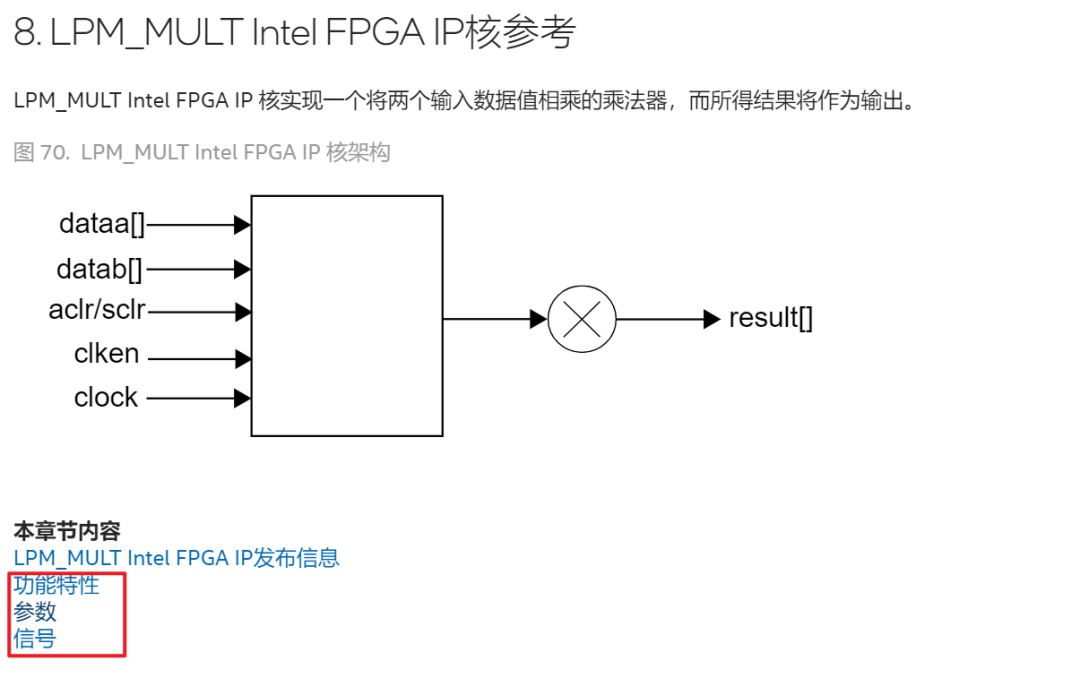

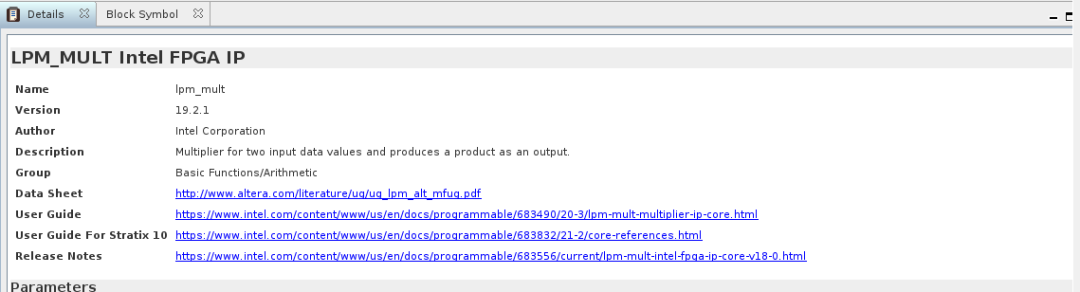

本案例中LPM_MULT Intel FPGA IP 核是一个两个输入数据乘法器,两个相乘数据作为输入,所得结果作为输出。

1.IP功能特性描述

LPM_MULT 核提供如下特性:

生成一个乘法器将两个输入数据值相乘

支持1–256位数据宽度

支持有符号和无符号数据表示格式

支持区域或速度优化

支持具有可配置输出延迟的流水线操作

为专用数字信号处理(DSP)模块电路或逻辑单元(LE)中的实现提供选项。

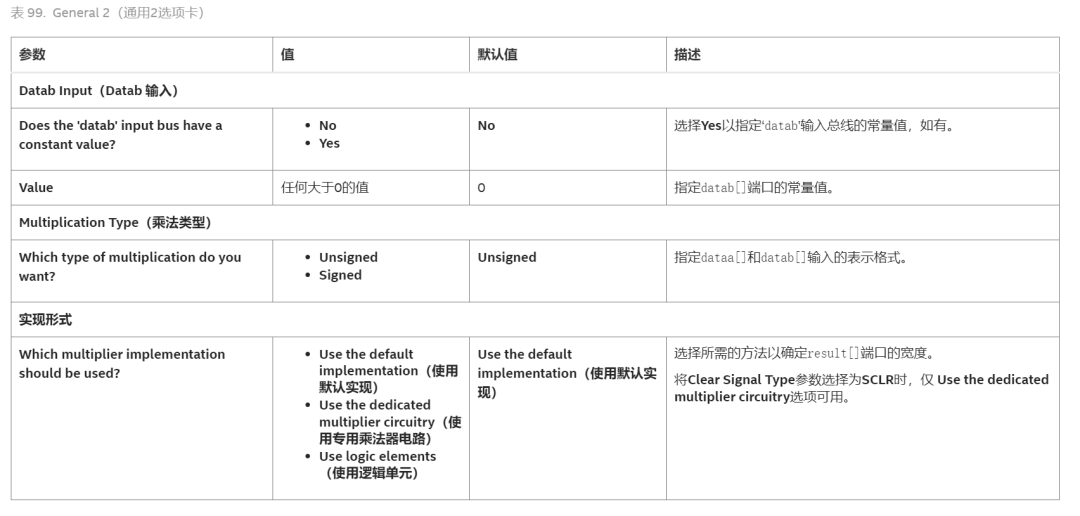

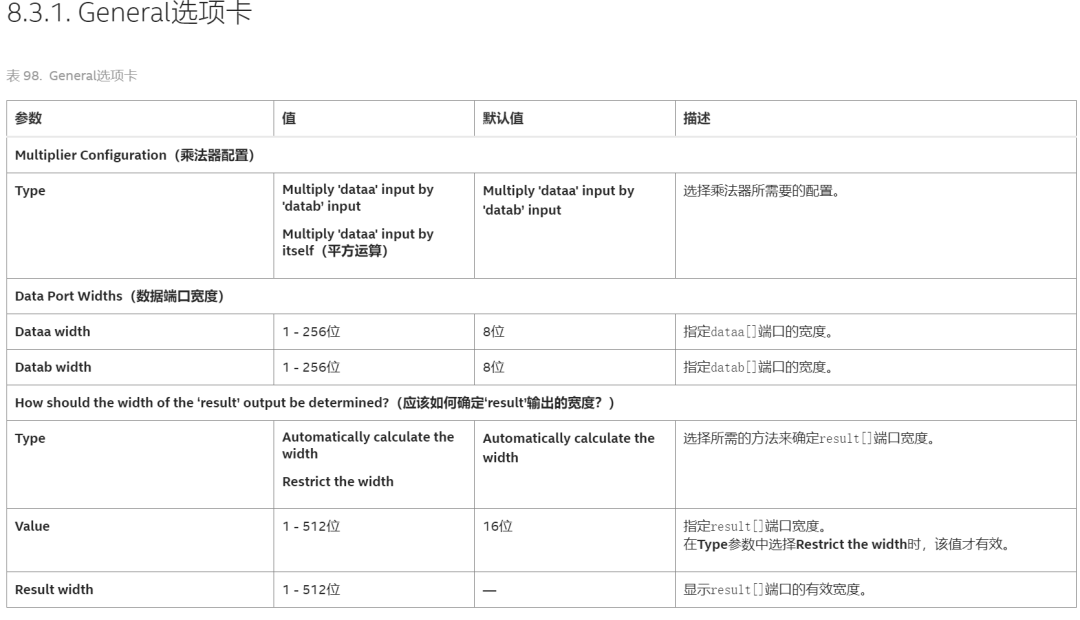

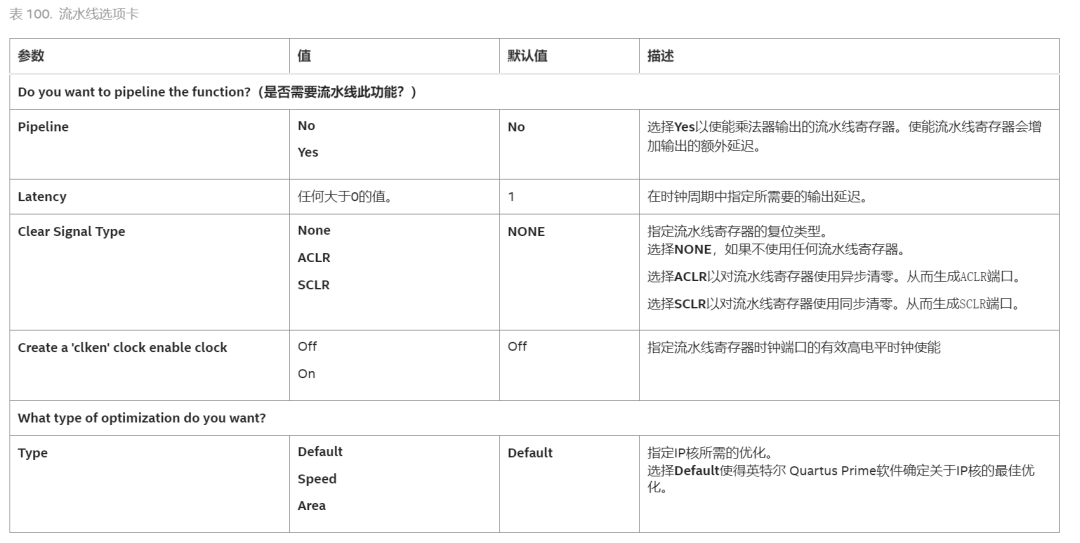

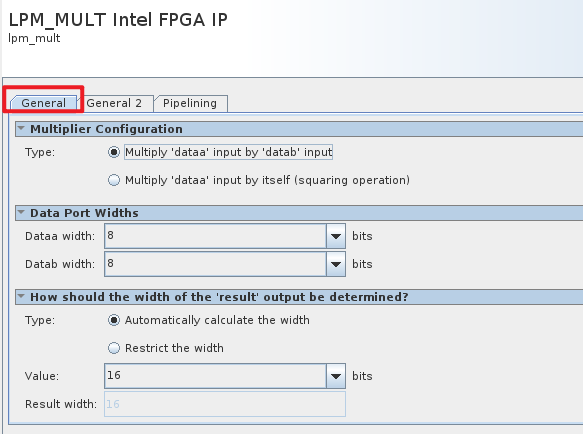

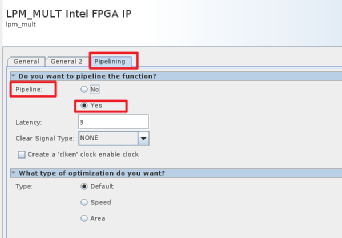

2.IP参数设置

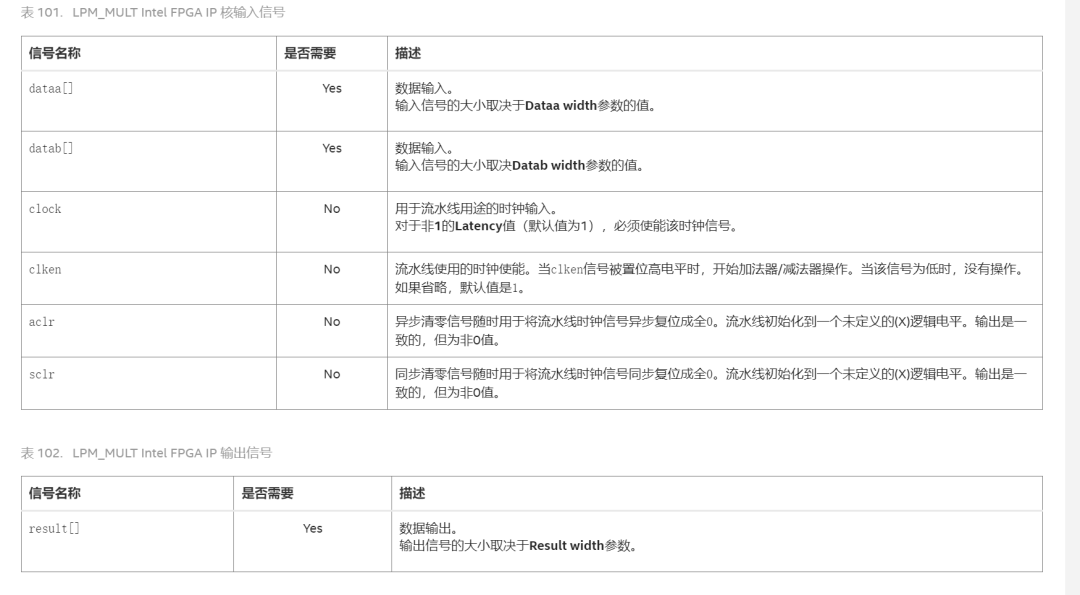

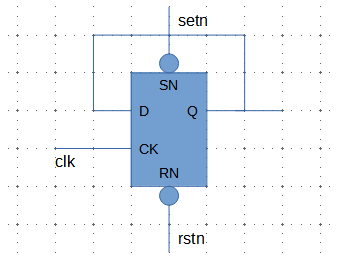

3.接口信号

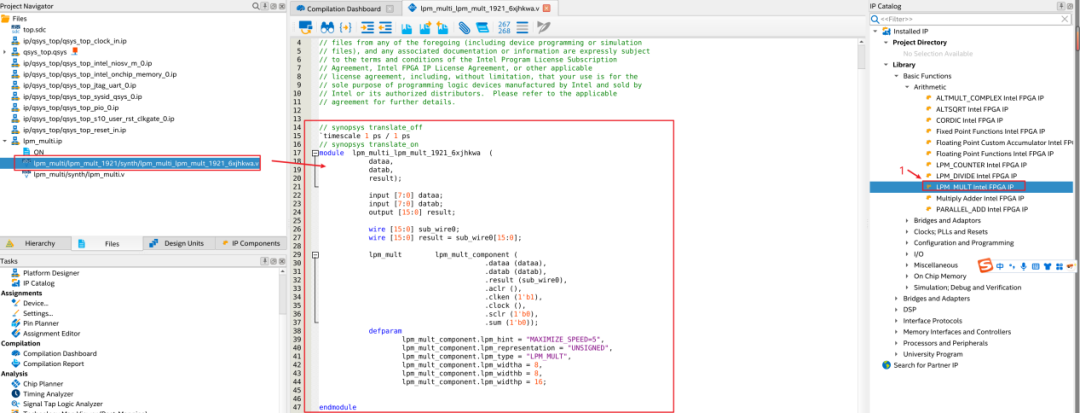

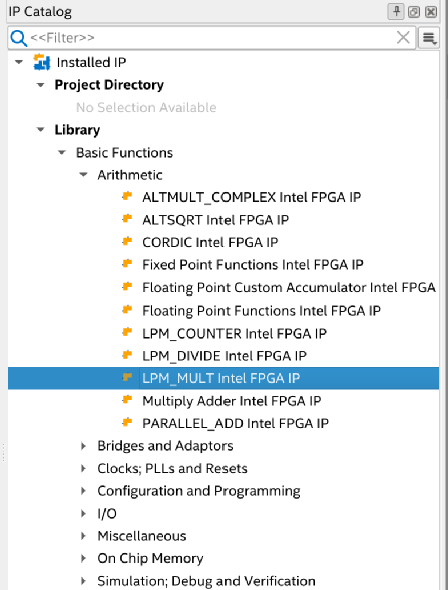

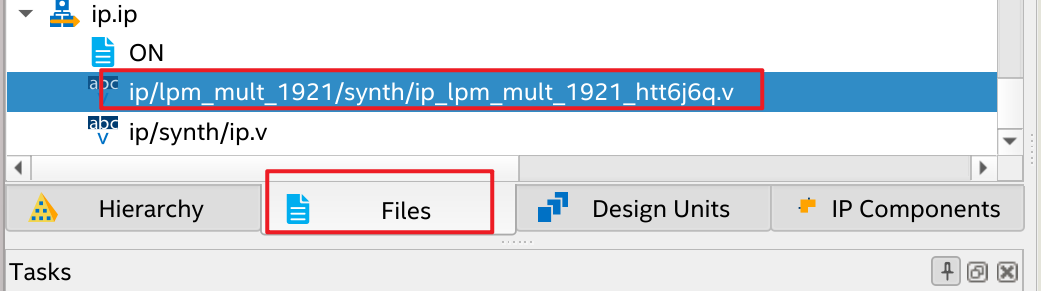

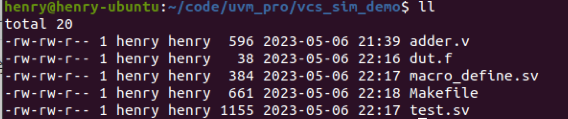

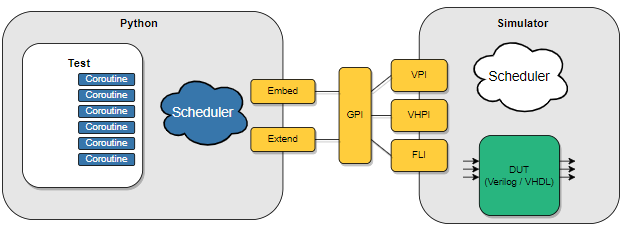

4.quartus如何调用IP

FPGA IP描述文档路径

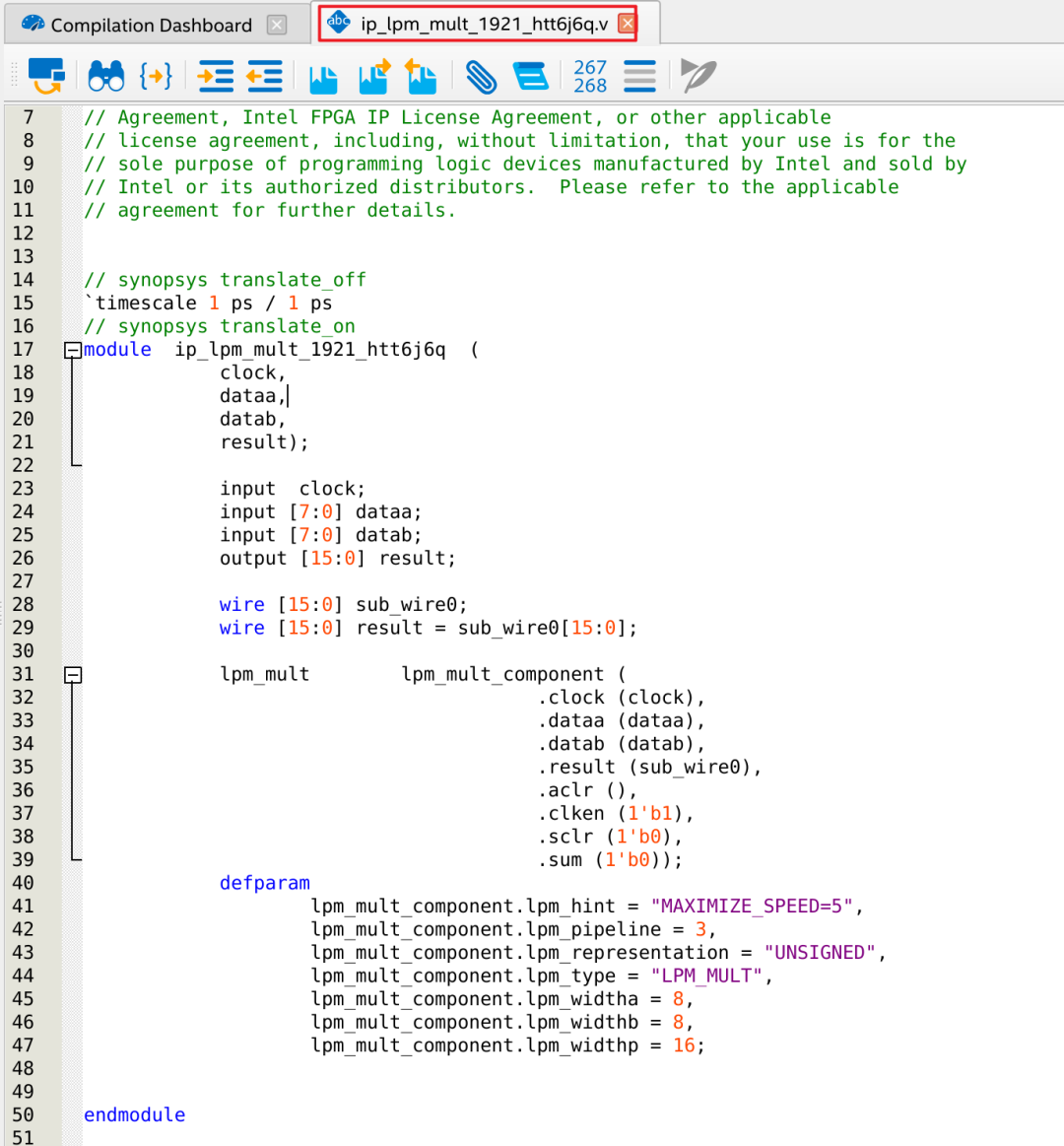

5.参数化调用IP

参考quartus工具给出的lpm_mult调用方法,参数化调用IP。

module asic_lpm_mult #( parameter PIPE_NUM = 4 , parameter MULT_DATAA_WDTH = 16 , parameter MULT_DATAB_WDTH = 16 , parameter MULT_RESULT_WDTH = 32 )( input i_clk , input [MULT_DATAA_WDTH -1:0] dataa , input [MULT_DATAB_WDTH -1:0] datab , output [MULT_RESULT_WDTH -1:0] result); lpm_mult u_lpm_mult ( .clock ( i_clk ), .dataa ( dataa ), .datab ( datab ), .result ( result ), .aclr ( ), .clken ( 1'b1 ), .sclr ( 1'b0 ), //.sum ( 1'b0 ) ); defparam u_lpm_mult.lpm_hint = "MAXIMIZE_SPEED=9", u_lpm_mult.lpm_pipeline = PIPE_NUM, u_lpm_mult.lpm_representation = "UNSIGNED", u_lpm_mult.lpm_type = "LPM_MULT", u_lpm_mult.lpm_widtha = MULT_DATAA_WDTH, u_lpm_mult.lpm_widthb = MULT_DATAB_WDTH, u_lpm_mult.lpm_widthp = MULT_RESULT_WDTH;endmodule

评论区

登录后即可参与讨论

立即登录