前言

自从学习FPGA以来,唯一做过的完整系统就是基于basys2得多功能数字表。记得当时做的时候也没少头疼,最后用时间磨出来了一个不是很完整的小系统,当时还是产生了满满的成就感。现在回头看来,先不说功能实现的如何,首先代码书写满是不规范,其中犯得最多的一个问题就是把verilog当C来写。所以,我决定趁着寒假自由支配的时间比较多,决定重写多功能数字时钟,算是对我大二第一学期以来对verilog的学习做一个总结。

首先,重写后的工程不仅在功能上做了一些优化,而且占用片内的资源也相对来说少了一些。话不多说先上图。

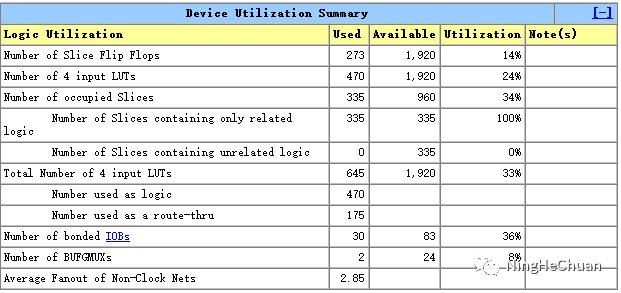

原来工程的资源占用情况

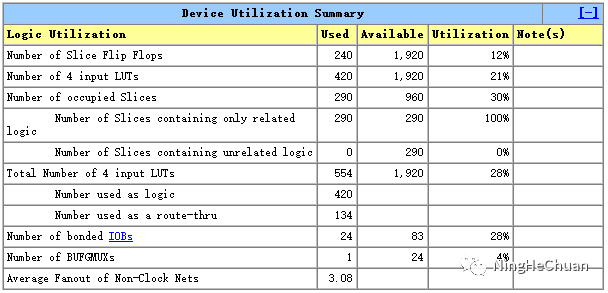

重写后资源占用情况(少了一点点,呵呵)

一、**摘要**

多功能数字表,有数字钟、秒表(有暂停清零功能)、闹钟(可设置)、外设蜂鸣器(当闹钟达到设定时间的时候蜂鸣器响应)。第一次写的代码主要是代码书写不规范,可读性和可移植性不强,一个always块里经常给多个寄存器赋值,或者多个if...else语句嵌套,这次重写在占用资源上得到优化,功能更加完善。

二、设计思想

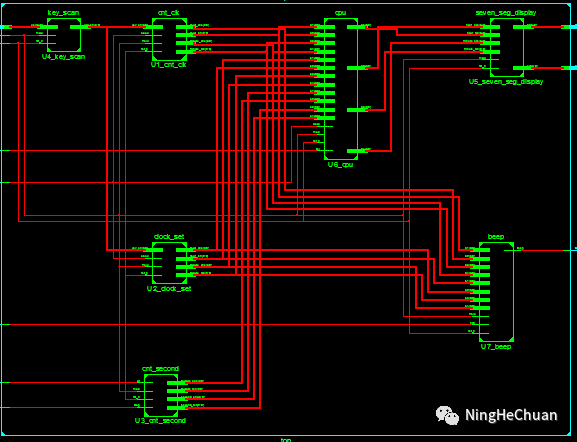

主要有七个模块构成:数字钟计数、秒表计数、按键驱动、数码管显示、蜂鸣器、闹钟设置、中央数据处理中心。下面是rtl原理图。在设计闹钟、时钟、以及秒表共享数码管显示模块的时候,由于每个数码管是单独显示的所以闹钟、时钟、秒表设置模块的一共12个输出我还没有想到更好的办法处理,就专门写了一个cpu模块将各个功能模块对应使用拨码开关什么时候数码管应该显示的信号。感觉这种写法cpu模块的连线有点多。所以以后有机会再回头看看怎么优化一下。

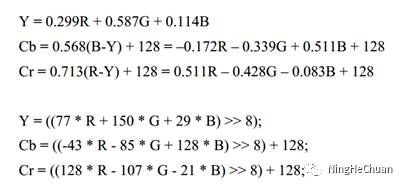

在写时钟计数器时为了使时钟信号的准确,我采用数据流型信号,来作为时间的进位出发标志,代码如下,这种写法,即可以节省寄存器资源占用,也可以在将信号作为边沿检测使用时避免时钟偏移(skew)。

按键消抖模块,我采用的是软件消抖,当按键按下后有一段不稳定时期,所以在检测到按键按下后计数器开始计数,当计数器记到一定数值,按键才会响应,当按键松开,计数器停止计数,所以在可以将那一段不稳定时期避免开。代码如下,可以根据所需要的按键个数自定义位宽!

蜂鸣器模块,当时钟计数到的时间与预先设置的时间相同时,蜂鸣器响应,发出救护车的声音。蜂鸣器驱动救护之音方法与呼吸灯类似,使用pwm信号脉宽调制,当pwm信号越来越高占空比高的时候,蜂鸣器声音越来越大,反之蜂鸣器声音越来越小。本例采用的无源蜂鸣器(有源蜂鸣器只需要通电便可直接响应),代码才考如下:

最后附上数码管显示模块,该模块没有复杂的地方会写译码器就应该能看懂

今天无意之中看到了另一种设置多功能数字表的思想,废话少说,下面做以笔记。

我原来的设计,在秒分频过后,当记到59秒时,将分的个位加1,当分的个位记到9时将分的十位加1,当分的十个位为59时,将时的个位加1,以此类推。我使用的basys2开发板只有四个LED数码管,所以只能显示分时,所以有四个输出端口minute_one,minute_ten,hour_one,hour_ten。完成显示。

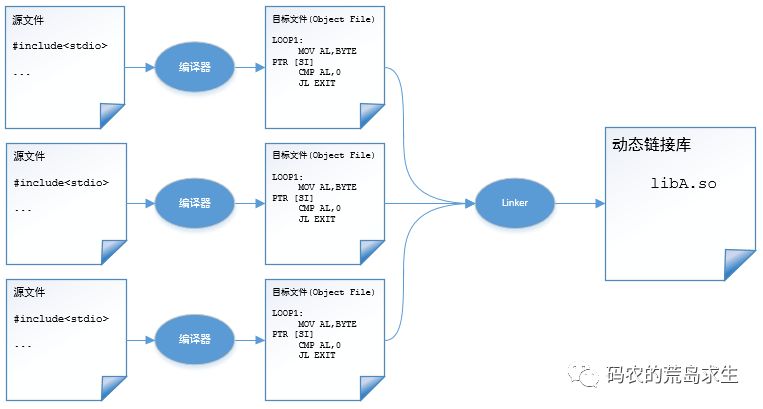

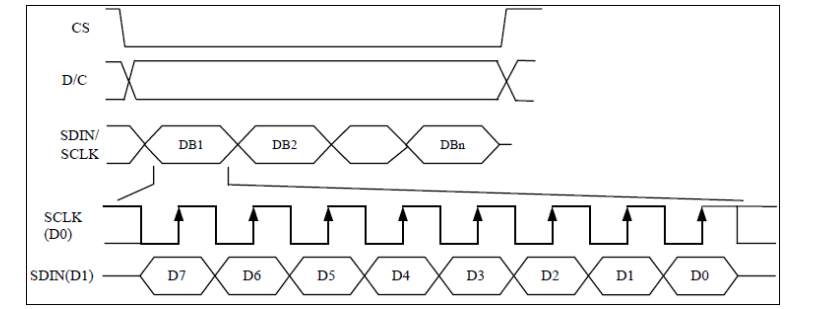

下面我引出另一种设计思路

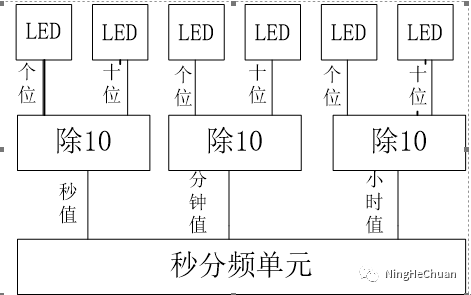

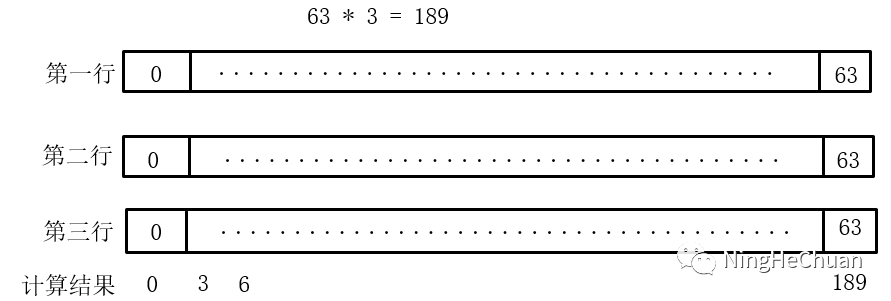

将秒计数到59,分进行进位,将分计数到59,小时进行进位,最后小时计数到23。然而一个时钟的个位和十位是分别显示的,所以还要做一个接口转换,把2位十进制数的个位和十位分离开。具体方法就是除以10,商是十位的值,余是个位的值。

如图所示:

三、实验总结

工作总结

第二期我们小队选择多功能数字时钟一题,针对basys2开发板使用Verilog HDL语言编译,完成该工程。题目要求多功能数字中有时钟(可校时)、秒表(可清零、暂停)功能,我们在原有题目完成的基础上添加了闹钟功能,在完成任务过程中可谓是一路心酸加苦逼,但最后还是终于圆满完成!下面我将简述我们完成工作过程中具体遇到的一些问题。

心得与体会

从接触开始我就感觉按键消抖比较抽象,再加上对于放在我们这个数字钟的题目,按键不由的跟时钟扯到了一起,消抖的代码没有问题,但是因为这个题目的特殊,消抖后必须和时钟扯上关系,所以在这个问题上耗费了我很多的时间,上周从周一到周四四天里一下课我就来实验室,将代码改了一遍又一遍,改回来又改回去,到周四的时候我已经体会到绝望的感觉。周五终于解决了这个问题。到这里我们的工程就取得了一个大前进。

我其他两个组员编写了秒表计数的模块,然后在周五下午我就立马将模块整合,到此便完成了题目的所有要求。闹钟功能必须要又可以设置闹钟的功能而按键只有四个已经用过了,要是再在原来的基础上改动有可能别的模块出问题。周日的工作很顺利几乎没用多少时间,在原有的代码基础上增加个模块就实现了闹钟功能,至此我们的任务顺利完成。

从开始接触fpga以来已经有6个月了,我的还是很漫长,就像bingo曾经说的,我没资格放弃。现在寒假还有不到二十天结束,不知道我又能学多少,我不认为自己势必比别人聪明的人,但我相信通过自己的努力,会慢慢变得更好。最后献上一个图,每天多努力一点点和少努力一点点的差距就是这么大。

评论区

登录后即可参与讨论

立即登录