一、全球存储市场在AI驱动下的结构性重构

自2024年以来,全球存储产业进入三十年来最深刻的结构性变革期。这轮变化不同于历次“价格周期”,而是由AI爆发引发的产能重构,使旧制程存储产品面临不可逆式退出。

以HBM为代表的高端存储占据晶圆产能,其单片晶圆资源占用量是SDRAM的3–5倍。在晶圆厂利润导向下,HBM/DDR5获得最大资源倾斜,旧制程产线(SDRAM/DDR3/小容量 eMMC)不再具备持续经营价值。这意味着:

-

SDRAM(46/65nm)产能被持续削减

-

DDR3/部分DDR4陆续停产

-

4GB/8GB/16GB小容量eMMC持续断供、涨价

-

旧制程NAND与部分并行存储将逐步消失

这不是暂时性短缺,而是未来3–5年的行业底层趋势。

传统高性能MCU使用的存储组合(SDRAM+eMMC)正在被产业链“自然淘汰”。在这一背景下,高性能MCU必然转向:

-

PSRAM/HyperRAM

-

串行NAND Flash

-

高速NOR(FlexSPI XIP)

而NXP RT系列是业内最早全面适配这一新存储体系的高性能MCU平台。

二、外扩RAM的时代迁移:SDRAM→PSRAM/HyperRAM

过去十年MCU的大容量RAM主流是SDRAM,但在AI和先进制程挤压下,SDRAM已出现以下结构性问题,因此,SDRAM的退出已成为必然。

-

制程老旧,产能快速萎缩

-

单价上涨 2–5倍

-

高速并行接口导致PCB布线复杂

-

EMC/EMI难度高

-

不适用于低功耗与新型HMI/AI-lite

✅PSRAM/HyperRAM:SDRAM的自然承**接者,未来三到五年高性能MCU**的行业主流RAM

PSRAM/HyperRAM采用更新制程,具备:

-

简单串行接口(QSPI/OPI)

-

接口简单, 引脚数少

-

功耗低

-

适合IoT、小屏GUI、图像缓存

-

Roadmap清晰:128Mb→256Mb→512Mb→1Gb

在SDRAM完全退出前,PSRAM/HyperRAM将承担大部分中高端MCU RAM负载。

目前全球高性MCU中,RT系列MCU是最早原生支持PSRAM/HyperBus的产品线,在 RAM 技术演进上具备先发优势。

三、eMMC的终局与NAND的崛起

与SDRAM类似,小容量eMMC(4GB/8GB/16GB)也正在快速退出,这是由移动行业全面转向UFS所导致的结构性结果,eMMC不再适合作为高性能MCU的大容量存储:

-

存储厂商主动停产小容量eMMC

-

4GB eMMC

-

行情已涨至20–25$

-

8GB eMMC从9$涨到20$

-

未来供应将持续收缩

✅ NAND Flash: 未来高性能MCU的大容量主存储

NAND的优势决定了它将成为MCU的主流大容量数据存储:

-

成本远低于eMMC(低40–60%)

-

制程成熟、供应厂商众多

-

容量灵活

-

可满足GUI资源、AI模型、固件等大容量需求

更关键的是:

✅RT1170/RT700原生支持NAND Boot(ECC+坏块管理)在主流高性能MCU中极为少见。

四、PSRAM/HyperRAM技术路线与市场发展趋势

产业路线已足够明确:

-

PSRAM:成本敏感型 IoT/GUI

-

HyperRAM:高性能 HMI/AI-lite

-

HyperBus逐步成为 MCU RAM主接口标准

-

制造商路线图:容量与带宽逐年提升

-

RT系列已完美覆盖PSRAM与HyperRAM生态

值得强调的是:

✅RT1170提供HyperBus原生支持

✅RT700的三路4/8/16bit XSPI将成为未来多通道存储系统的最佳硬件基础

五、RT系列为何具备结构性优势?

5.1 RT系列三大代表产品

✅ RT1060-RT10xx主力产品

-

Cortex‑M7@600MHz

-

支持:4-bit QSPI、8-bit OPI

-

支持:串行PSRAM/HyperRAM

-

适用于中端HMI、音频、消费场景

✅ RT1170-旗舰双核(双FlexSPI)

-

Cortex‑M7@1GHz + Cortex‑M4@400MHz

-

双FlexSPI(FlexSPI1/2)

-

支持:QSPI、OPI、HyperBus

-

支持NAND Boot(ECC + 坏块管理)

-

适用于高性能HMI、工业控制、车载显示

✅ RT700,下一代三路XSPI (行业领先MCU存储平台)

-

三路独立XSPI:4-bit/8-bit/16-bit

-

可并行挂接NOR+NAND+PSRAM/HyperRAM

-

支持多模型缓存、多通道高带宽访问-面向AI、语音、边缘推理

RT700是业内首屈一指的三路16bit XSPI的MCU,未来扩展空间极大。

5.2 架构完整性:RT是行业极少数全覆盖未来存储路线的MCU

RT系列是全行业极少数同时支持:

-

PSRAM

-

HyperRAM

-

NAND Boot

-

XIP NOR

六、存储价格体系的结构性分化:RT系列的成本优势正在加速形成

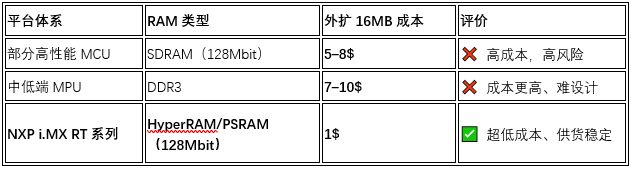

全球存储产业在2024–2026年进入深度重构期,先进制程(HBM、DDR5、UFS)持续扩产,而旧制程(SDRAM、DDR3、小容量 eMMC)快速萎缩。这使得不同 MCU/MPU 体系的存储成本出现了前所未有的“断层式分化”。

-

部分高性能MCU架构(SDRAM+eMMC)储存成本失控

-

MPU架构(DDR+eMMC)储存成本飙升

-

RT架构(PSRAM/HyperRAM+串行NAND)储存呈稳定趋势

这一分化使RT系列在 成本、可用性、风险控制、架构可持续性 上全面领先。

本章将重点对比:

✅RT vs 部分高性能MCU:“接口+成本”的双重降维打击

✅RT vs 中低端MPU:“系统级成本结构”优势扩大

6.1 RT vs 部分高性能MCU:成本结构出现断层,RT系列成本低40–60%

部分MCU厂商大部分还是采用的仍是上一个时代的存储架构:

-

外扩RAM:SDRAM

-

大容量存储:eMMC

-

扩展接口:并行 FMC, 高复杂度

而RT系列的架构是面向未来的,这是一场“体系级别”的架构代差,而非简单的产品差异:

-

外扩RAM:PSRAM/HyperRAM

-

大容量存储:NAND(可Boot)

-

扩展接口:FlexSPI/XSPI(高带宽、低复杂度)

6.1.1 外扩RAM:PSRAM/HyperRAM vs SDRAM 的成本断层

根据最新市场价格(HyperRAM/PSRAM可视为同价):

✅ HyperRAM/PSRAM 最新价格:

| 容量 | 换算 | 最新价格 | | 64 Mbit | 8 MB | 0.6$ | | 128 Mbit | 16 MB | 1.0$ | | 256 Mbit | 32 MB | 2.0$ |

✅新制程、价格稳定✅长期供货不受老制程退出影响✅多家供应商持续扩产(APM/ISSI/Winbond)

✅ SDRAM/DDR3:旧制程价格高企且供货风险加大

| 类型 | 常见容量 | 当前价格区间 | | SDRAM(老制程) | 128Mbit/16MB | 5–8$ | | DDR3(老制程持续退出) | 4Gb/512MB | 7–10$ |

❌成本高❌制程停产风险大❌未来 2–3 年缺货与涨价风险升级

✅成本计算:RT(PSRAM/HyperRAM)优势巨大:

以16MB为比较基准:

✅成本差异:

- 对比SDRAM:1$ vs 5–8$ →节省 80–87%成本

- 对比DDR3:1$ vs 7–10$ →节省 85–90%成本

✅结论:

RT的优势不是“便宜一点”,而是“成本级别完全不同”:

-

SDRAM/DDR3:属于旧制程尾期→ 高价+高风险

-

HyperRAM/PSRAM:新制程 → 成本是SDRAM的 1/5~1/8

-

RT系列借此获得结构性成本优势,BOM成本显著低于部分高性能MCU和中低端MPU

RT让外扩RAM从“几美元级”下降到“1美元级”,成本结构完全重塑。

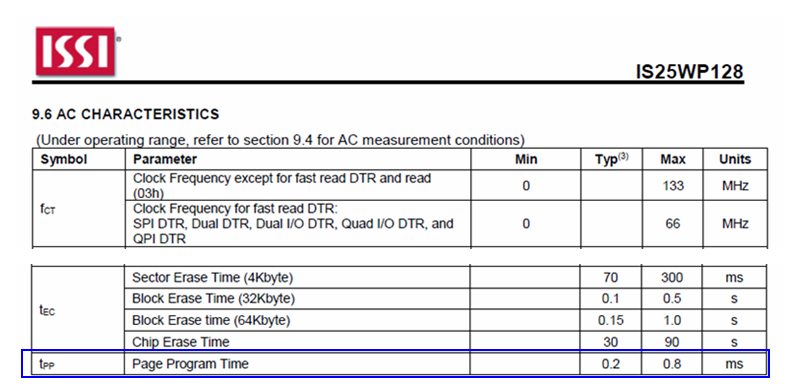

6.1.2 大容量 Flash:NAND vs eMMC 的结构性成本差异

✅ eMMC(旧制程)价格崩坏:

-

4GB eMMC:25$

-

8GB eMMC:20$

-

16GB eMMC:21$

小容量 eMMC 已成为“奢侈品”,完全不适合高性能MCU。

✅ NAND(新制程)依旧价格可控:

| NAND 容量 | 价格(2025–2026) | | 1Gbit(128MB) | 2.0–2.5$ | | 2Gbit(256MB) | 3.5–4$ | | 4Gbit(512MB) | 8$ | | 8Gbit(1GB) | 12$ |

✅结论:

-

RT(NAND 架构) vs 部分高性能MCU (eMMC架构)

-

RT可降低 40–60%的存储成本

-

NAND生命周期更长

-

RT1170/RT700 具备 NAND Boot (带ECC)→ 同价位优势

6.1.3 接口成本:FlexSPI / XSPI vs 并行接口

✅ RT:FlexSPI / XSPI(行业领先MCU存储接口)

-

单线串行

-

支持4bit/ 8bit/16bit

-

布线极简

-

EMI/EMC成本极低

-

支持NAND/NOR/PSRAM/HyperRAM

-

RT700:三路 XSPI → 可并发访问 NOR+NAND+RAM

✅部分高性能MCU:并行总线

-

需要30–50根引脚

-

必须6层PCB

-

布线难度成倍增加

-

EMI/EMC成本高

-

系统功耗更高

-

SDRAM 时序调试复杂

✅结论:RT的接口成本压制部分高性能MCU 70%以上,这是纯工程成本的降维打击。

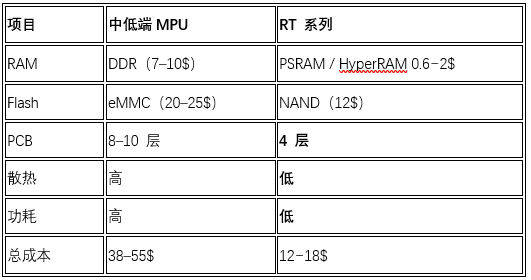

6.2 RT vs 中低端MPU:系统级成本降低50–70%(存储是决定性因素)

中低端MPU架构必须使用:

-

DDR(主内存)

-

eMMC(大容量)

但DDR+eMMC正是AI时代涨价最猛烈的两个部件。

6.2.1 中低端MPU的核心问题:DDR成本黑洞

✅ DDR3/DDR4本体价格高:

-

DDR3(4Gb):7–10$

-

DDR4(更贵)

✅ DDR 的隐藏成本更高:

-

PCB必须8–10层

-

高速布线拓扑复杂

-

SI/PI分析困难

-

必须加入散热器/气流设计

-

功耗与维护成本持续上升

一个中低端MPU项目里,DDR是成本灾难的起点。

6.2.2 中低端MPU的第二个问题:eMMC价格失控

如前:

-

4GB eMMC:25$

-

8GB eMMC:20$

绝大部分中低端MPU没有选择空间,不得不使用eMMC。

6.2.3 RT的系统成本:比MPU降低50–70%

✅RT系统成本比中低端MPU低50–70%

✅RT覆盖中低端MPU 80%的中端应用(HMI、视觉、AI-lite)

✅RT1170 (1GHz M7)已达到甚至超越部分MPU性能下限→ 性能不再是壁垒

6.3 RT的优势来自“结构性正确性”

RT的优势不是微小优化,而是:

✅ RT采用的存储技术都处于上升周期(PSRAM/HyperRAM/NAND)

✅ 绝大部分的MCU/MPU采用的存储技术都处于衰退周期(SDRAM/DDR/eMMC)

RT的成本优势并非短期价格波动,而是:

由产业趋势+架构选择共同构成的不可逆结构性红利。

评论区

登录后即可参与讨论

立即登录