用Cadence Virtuoso IC617仿真工艺库参数

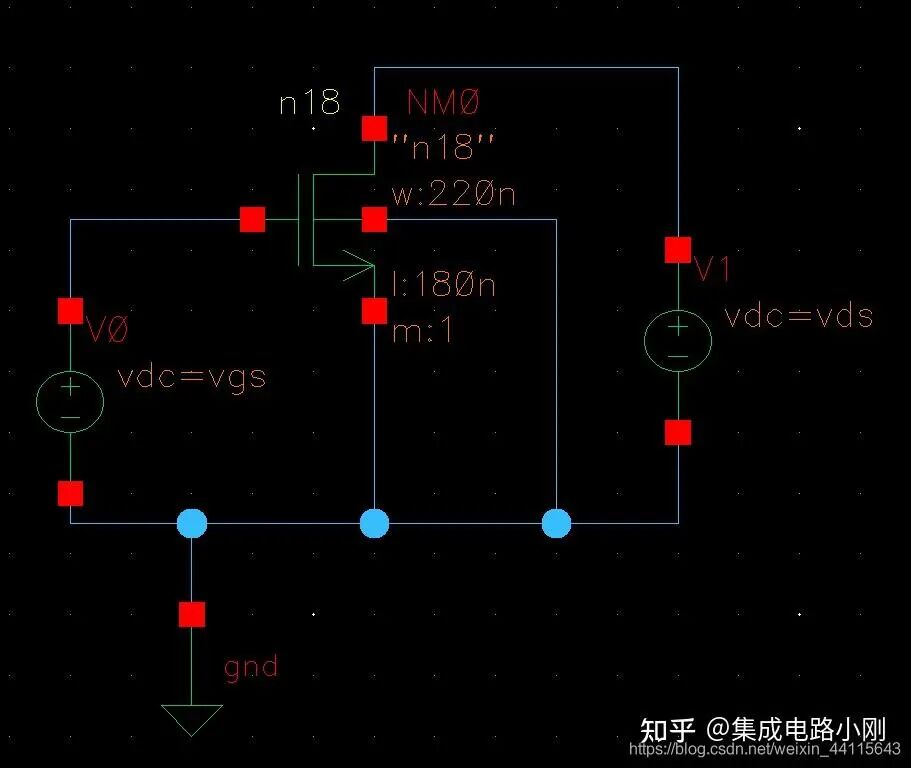

本文将会描述,如何通过V-I特性曲线得出SMIC 0.18um工艺库的工艺参数。 N-MOS的测量 提取数据 上一篇文章已经得到了在不同的vgs下的vds参数曲线。原理图如下。W为220um,L为180um,后面会用到。 为了更精确得到数据,这里改变一下扫描范围,vds范围改为0-2V,vgs范围改为0.6-1.2V,步长设置为0.2V,得出结果如下图。 选择Marker菜单中的Create

纳米网电路设计频道 — 提供电路设计领域最新资讯、技术文章和行业动态。

本文将会描述,如何通过V-I特性曲线得出SMIC 0.18um工艺库的工艺参数。 N-MOS的测量 提取数据 上一篇文章已经得到了在不同的vgs下的vds参数曲线。原理图如下。W为220um,L为180um,后面会用到。 为了更精确得到数据,这里改变一下扫描范围,vds范围改为0-2V,vgs范围改为0.6-1.2V,步长设置为0.2V,得出结果如下图。 选择Marker菜单中的Create

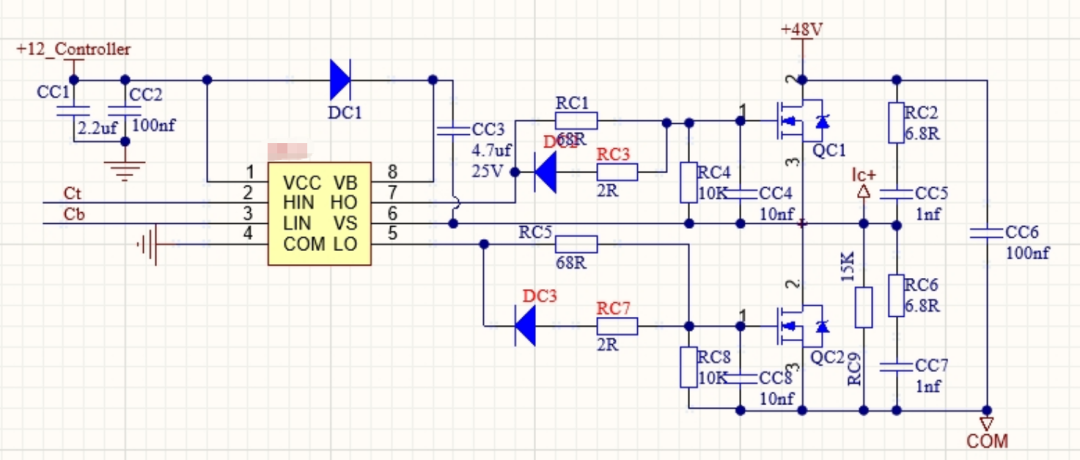

在 BLDC 驱动电路里,A/B/C 三相相节点对地接 几十k 下拉电阻,是无感方波控制里最经典、最必要的设计,核心目的只有一个:给反电动势(BEMF)过零检测提供稳定电位基准,同时兼顾安全与抗干扰。 一、核心目的:解决无感控制的「相端浮空」问题(最关键) 无感 BLDC 靠检测三相反电动势过零点判断转子位置,而: 电机静止、低速、上下桥 MOS 全关断时,三相相端是完全浮空的高阻态 浮空相端

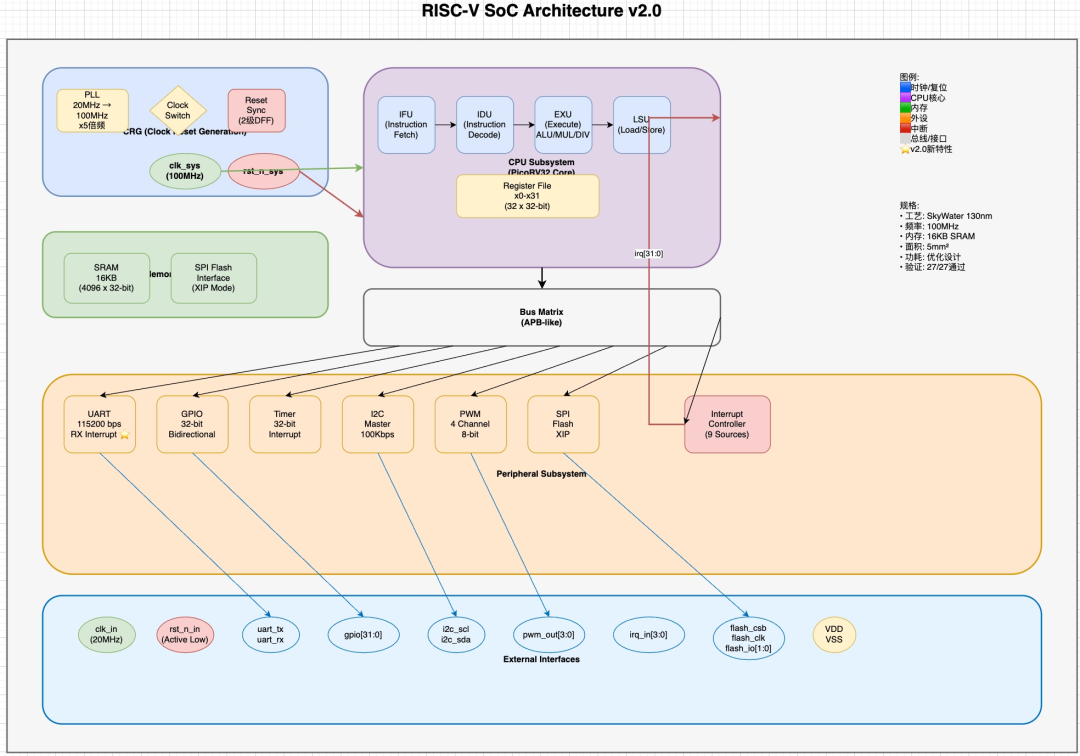

OpenClaw帮我做了件我一直想做的事情。 一直想串一下基于全开源EDA flow的芯片设计流程,但其中有大量的工具的安装和工具flows的使用,需要耗费大量的精力,OpenClaw用了一天时间帮我串了整个流程。 🎯设计目标 基于 PicoSoC 架构的增强版 RISC-V SoC 集成多种常用外设 (UART, GPIO, I2C, PWM, Timer, SPI) 适用于嵌入式控制和物联网

集成电路版图设计就是指将电路设计电路图或电路描述语言映射到物理描述层面,从而可以将设计好的电路映射到晶圆上生产。 版图是包含集成电路的器件类型,器件尺寸,器件之间的相对位置以及各个器件之间的连接关系等相关物理信息的图形,这些图形由位于不同绘图层上的图形构成。 版图工程师的职责包括:芯片物理结构分析,逻辑分析,建立后端设计流程,版图布局布线,版图物理验证,联络代工厂提交生产数据。 版图设计方法(从

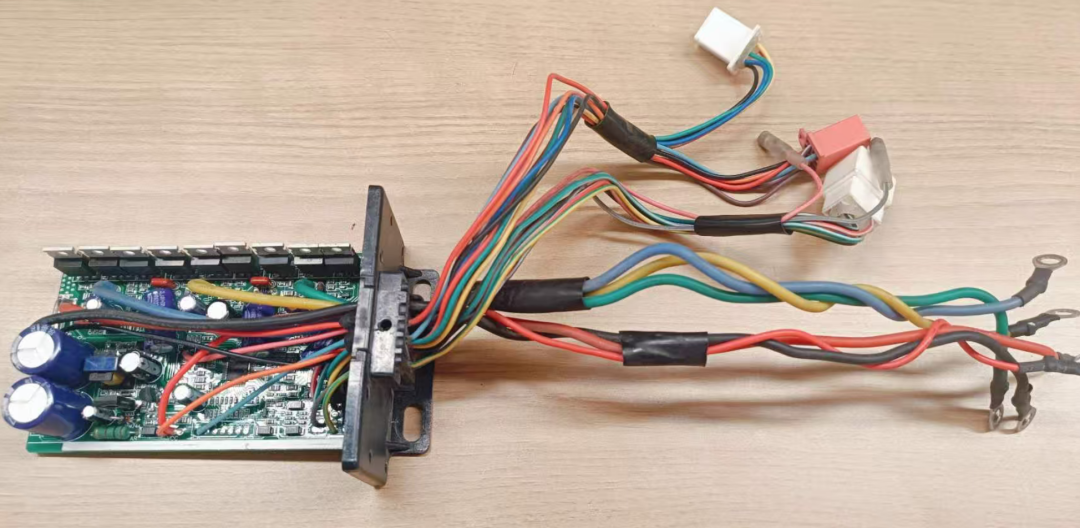

科普一下:什么是9管电驱控制器? 无刷电机一般由3个半桥构成,最基本的电路需要6个MOS管,也就是常说的6管控制器,为了增大功率也有采用2管并联当一个管的,于是出现了12管控制器。那么9管控制器是怎么回事呢?您可能猜到了:是半桥中和单臂用双管,另一单臂用单管。——的确如此。那么为何如此设计呢,难道两个臂发热不同? 这种情况只有1个管工作于PWM状态,损耗较大,另一个管常开,损耗很小。故只有PWM状

对于常规的track,通常基于LEF里的pitch,offset就可以直接创建(PS:当然也有invs自动调整的场景,这个需要用户留意),但是由于std-cell 的PG pin的存在,这个对于M1 (std-cell pin layer)track,是有一点小复杂,如果用户想充分利用M1的track,需要一点小技巧,这篇文章采用了了LEF里的一个特性来实现这个目的。闲言少叙,ICer GO!

在数字电路设计的世界里,Verilog不仅是实现功能的工具,更是工程师与工具(综合器、仿真器)、与同事、与未来的自己沟通的桥梁。糟糕的代码风格如同混乱的电路板,线缆缠绕,故障难寻;而优雅的代码风格则像一份精密的施工图,层次清晰,一目了然。它不仅是个人习惯,更是项目成功的第一道防线。 一、结构与可读性:像写文章一样写代码 1. 一致的缩进与格式统一的缩进(建议使用2或4个空格)是代码可读性的基石。

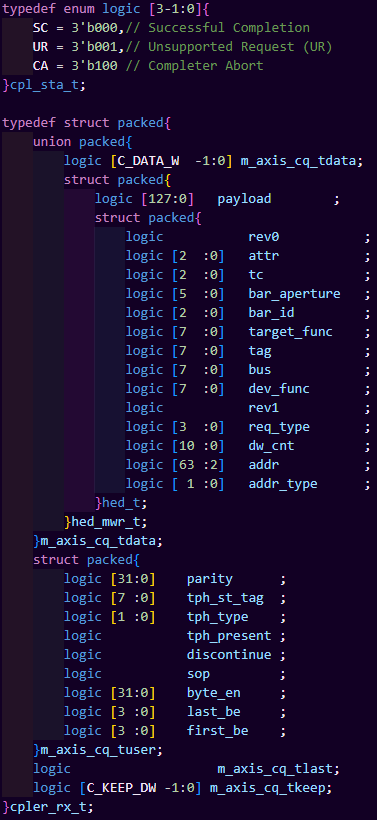

• 前言 • SV的优劣 • 最方便的信号类型(logic) • 定义复杂信号的优雅方式(struct) • 最省心的状态机利器(enum) • 提前发现多驱 • 让数据结构更清爽的秘诀(typedef) • 最常用的批量信号写法(packed array) • 模块通信的终极级懒人包(interface) • 最优雅的头文件(package) • 最懂工程师意图的过程块定义(always)

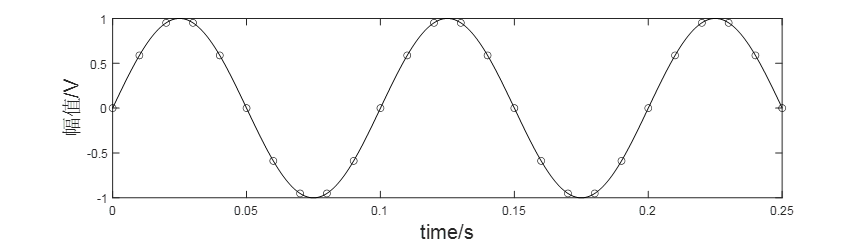

大家一定要明确几个概念:什么是模拟信号?什么是连续信号?什么是数字信号?什么是离散信号? 第一,模拟信号。 “模拟”这个词表面的意思是模仿,这个词在上个世纪80年代左右用于模拟计算机(当今用的是数字算计机),早期计算机是用电压或者电流来模拟、模仿方程中涉及到的温度、速度、距离等物理量,模拟信号的概念就是从这来的。 现在我们的计算机都是数字计算机,处理的信号大部分都是数字信号,但是模拟信号这个词被沿

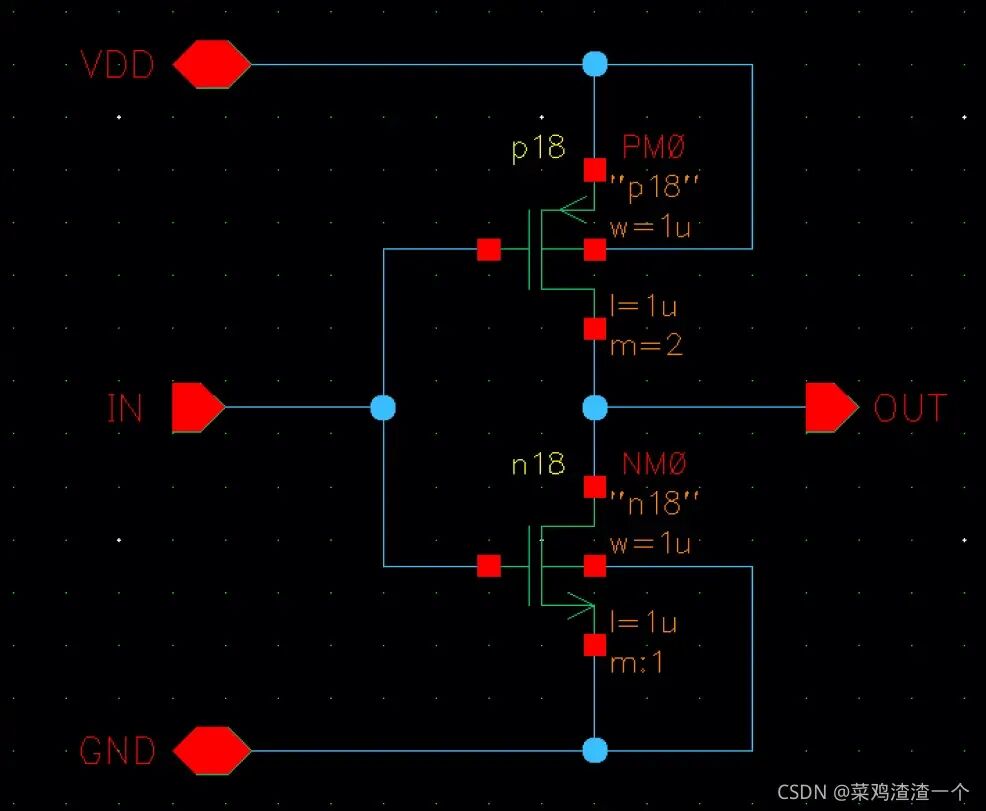

本文主要记录了如何用Cadence Virtuoso IC617建立器件和生成版图。虽然前面的文章记录过如何生成器件,但是本文将重新记录,方便查看和学习。本文将用以下原理图,这是一个反相器。 建立器件 确保原理图中的器件都是有版图的,没有包含各种信号源,同时接口都放置了Pin脚。选择Create -> Cellview -> From Cellview。 名字默认为原理图的名字。点

示波器排查CAN错误帧,没几个月消化不了,建议收藏! 硬件经典面试100题,这些不会,怎么找工作 为了省3颗NMOS,烧了整个电机驱动板! 180买了个泡水的数控电源PSP603,花了4天抄电路,终于救活了! 经典稳压芯片LM7805内部电路分析 我的2025年年终总结 小鸡电路 尖峰抑制,可以看看缓冲电路设计方法

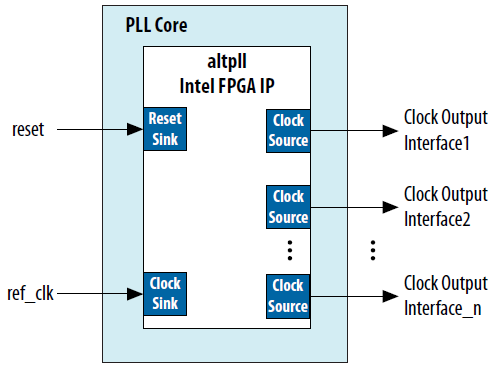

本文介绍了Altera FPGA中的Avalon MM总线接口规范,包括Avalon时钟接口、复位接口、存储器映射接口和Conduit接口的信号及属性,详细解释了这些接口的功能和应用场景。

本文深入探讨了功率因数校正(PFC)技术的演进,特别是碳化硅(SiC)MOSFET在PFC中的应用。文章分析了PFC的历史、无源和有源PFC技术,并详细介绍了SiC MOSFET在图腾柱PFC、AI算力电源、电动汽车充电桩和固态变压器中的优势。

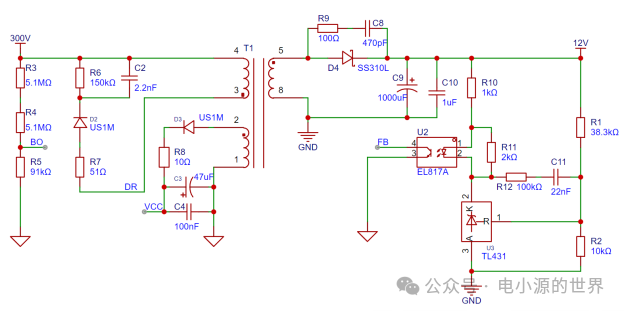

本文详细解析了反激开关电源反馈环路的计算过程,包括TL431参数计算、光耦参数设计以及补偿网络的作用,帮助读者理解如何通过调节反馈环路来稳定输出电压。