Verilog入门指南:从软件思维到硬件描述

当你第一次接触Verilog时,很容易把它当成C或Java这样的编程语言。这是一个常见的误区,也是入门路上的第一个坎。Verilog不是一种编程语言,而是一种硬件描述语言。 你的角色不是“写程序”,而是在“画图纸”——用代码的形式描述一个数字电路应该长什么样。 一、核心思想:你是在描述电路 在开始写代码之前,请务必建立这个思维模型: 软件程序:是指令的序列,在CPU上按时间顺序执行。 硬件描述

纳米网电路设计频道 — 提供电路设计领域最新资讯、技术文章和行业动态。

当你第一次接触Verilog时,很容易把它当成C或Java这样的编程语言。这是一个常见的误区,也是入门路上的第一个坎。Verilog不是一种编程语言,而是一种硬件描述语言。 你的角色不是“写程序”,而是在“画图纸”——用代码的形式描述一个数字电路应该长什么样。 一、核心思想:你是在描述电路 在开始写代码之前,请务必建立这个思维模型: 软件程序:是指令的序列,在CPU上按时间顺序执行。 硬件描述

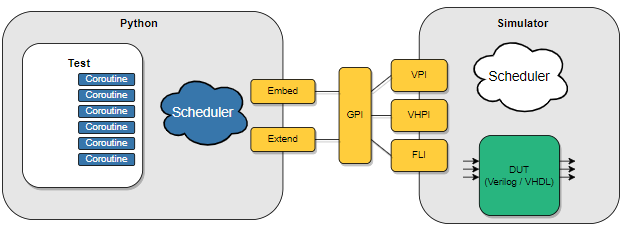

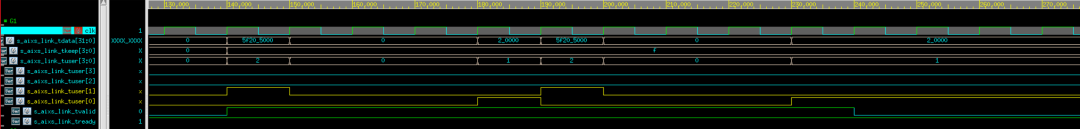

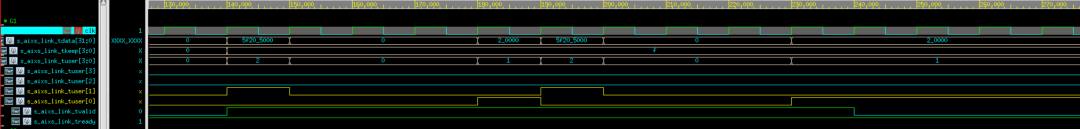

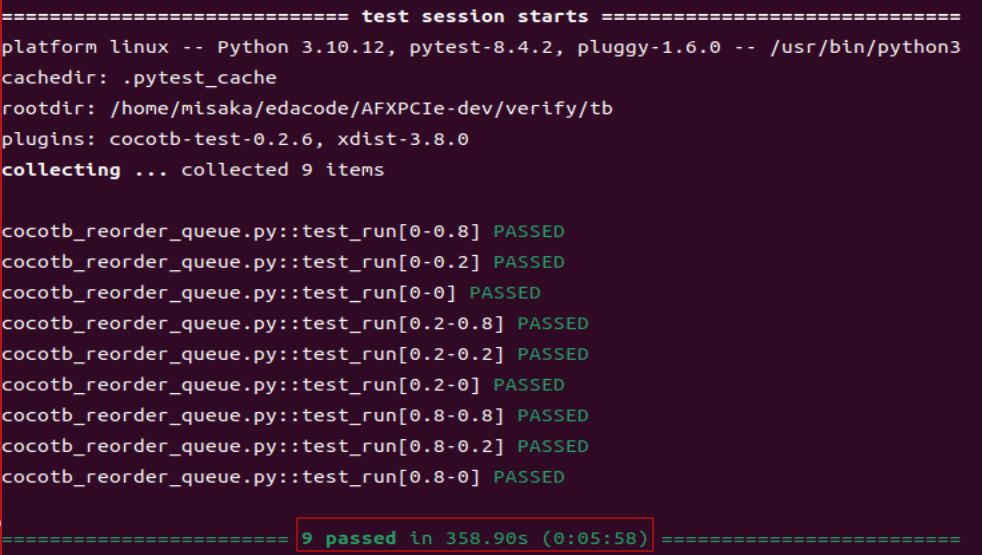

很多FPGA/IC工程师擅长设计,但在仿真方面较为薄弱。我认为主要问题在于,完整的仿真实现学习成本较高,如学习UVM需要掌握大量新的内容。而单纯使用Verilog自仿又难以满足需求,以报文仿真为例,我们需要解析报文,若仅依赖Verilog自仿,就相当于要自己编写一个报文解析模块,工作量非常庞大。而Python在数据处理方面则更加高效,如果加以利用,完全可以快速构建一个完整的仿真模型。Cocotb

01 什么是接地电阻? 接地电阻就是电流由接地装置流入大地再经大地流向另一接地体或向远处扩散所遇到的电阻,它包括接地线和接地体本身的电阻、接地体与大地的电阻之间的接触电阻以及两接地体之间大地的电阻或接地体到无限远处的大地电阻。 接地电阻大小直接体现了电气装置与“地”接触的良好程度,也反映了接地网的规模。在单点接地系统、干扰性强等条件下,可以采用辅助地极的测量方式进行测量。 02 接地主要分以下

HFSS使用入门 仿真螺旋形模型 1.在XZ平面创建一个⚪圆, 2.再点击工具栏螺线模型, 3.移动光标到坐标原点,单击鼠标确定螺线底圈半径 4.按住Z移动一段距离确定螺旋体盘升方向 5.调整参数 平面螺旋体创建: 1.在XY平面创建一个⚪圆, 2.再点击工具栏螺线模型, 3.移动光标到坐标原点,单击鼠标确定螺线底圈半径 4.按住Y移动一段距离确定螺旋体盘升方向 5.调整参数 7.完

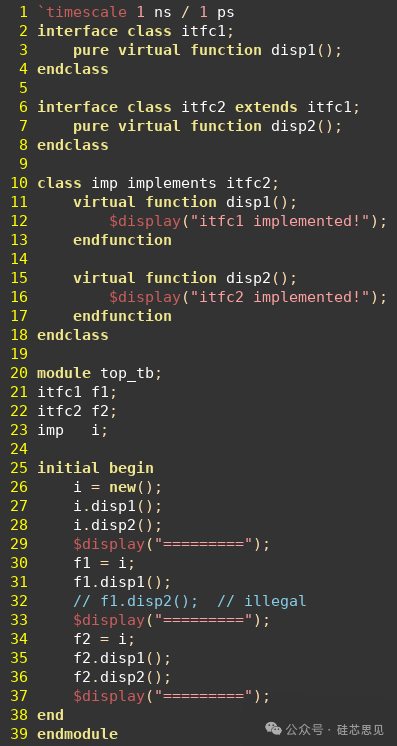

在SystemVerilog中,可以通过关键字implements指定实现类关联的接口类,接口类中定义的方法都是pure virtual方法,不能直接创建对象,其中的方法需要在与其关联的对象类中实现,这里需要注意,接口类与其对应的实现类之间的关系不是继承和被继承的关系。下面是接口类使用方式的简单示例: // 接口类定义interfaceclassABC;...endclass// 实现类关联对应的

1前言 很多FPGA/IC工程师擅长设计,但在仿真方面较为薄弱。我认为主要问题在于,完整的仿真实现学习成本较高,如学习UVM需要掌握大量新的内容。而单纯使用Verilog自仿又难以满足需求,以报文仿真为例,我们需要解析报文,若仅依赖Verilog自仿,就相当于要自己编写一个报文解析模块,工作量非常庞大。而Python在数据处理方面则更加高效,如果加以利用,完全可以快速构建一个完整的仿真模型。Coc

最近要学会HFSS这个软件仿真谐振器。 注意点: 安装软件路径不能包含中文名字。 按F键是选择面 按O键是选择体 Ctrl+D让物体适中显示 首先是设计一个T形波导, 端口1为信号输入,端口2和端口3为信号输出端口,通过改变隔片的位置可以改变端口1到端口2和端口3的传输功率和端口1的反射功率。 新建工程 选择求解类型为Solution 单位等 创建T形波导模型(设置参数) 设置波端

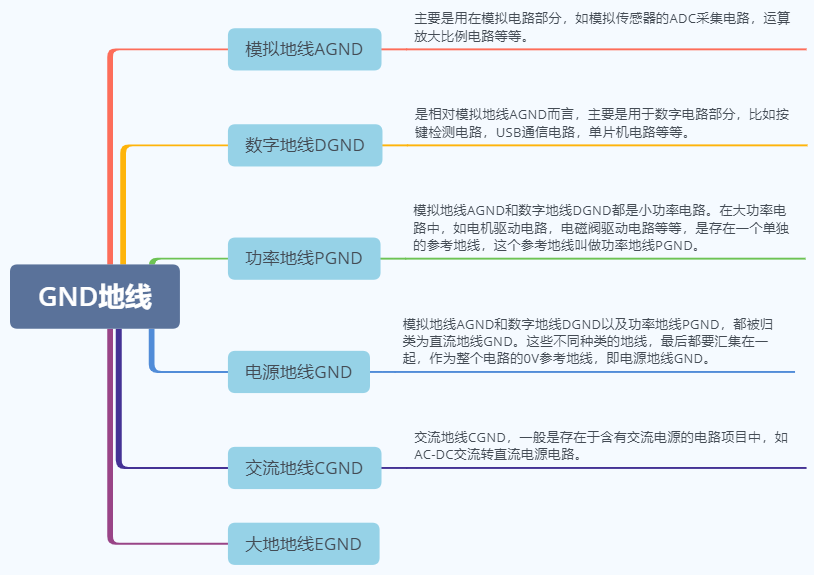

在电路原理设计阶段,为了降低电路之间的互相干扰,工程师一般会引入不同的GND地线,作为不同功能电路的0V参考点,形成不同的电流回路。 一、地线的分类 二、细究GND的原理 一个地线GND怎么会有这么多区分,简单的电路问题怎么弄得这么复杂?为什么需要引入这么多细分的GND地线功能呢? 工程师一般针对这类GND地线设计问题,都简单的统一命名为GND,在原理图设计过程中没有加以区分,导致在PCB布线的

一、标识符与注释 前面已经说到,模块名的定义要符合标识符的定义,那么什么是标识符呢?它的语法是什么呢? ①标识符是赋给对象的唯一名称,通过标识符可以提及相应的对象,Verilog语法将对转义标识符中的字符逐个处理。 ②标识符可以是字母、数字、下划线和美元符$的组合,并且标识符的第一个字母必须是字母或者是下划线。此外,在Verilog的标识符中,是区分大小写的。 ③Verilog中有一些关键字,简

前言 在上一篇文章中,我们提到相同协程是阻塞的,不同协程是并发的这一说法。然而,这种理解存在偏差,所以第一个现象并不像我们之前想象的那样。今天,我们将专门梳理协程的概念,深入剖析其本质,以纠正上次关于协程与阻塞的说明。 案例说明 下面我将介绍一种非常典型的现象 for i in range(2): await device_to_host_source.send(frame) for

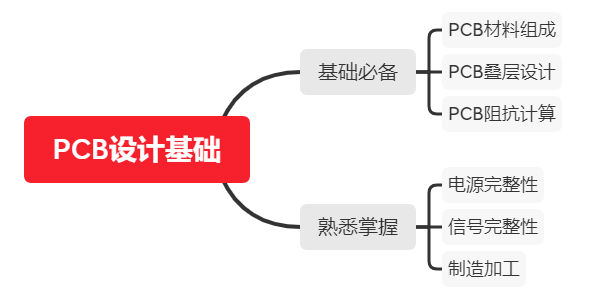

1.前言 求职面试时,大多数人都会在一个问题上纠结:去大公司还是小公司?这个问题在现阶段其实没有人能够给出一个100%完美的答案。如果展开来说,估计也要花好长时间。无论去哪个公司,落到我们自身来说,主要还是要能在岗位上体现出个人的价值。即用专业能力、综合素质能力去解决工作中的问题。 解决问题的快慢程度和结果好坏,就和我们掌握的专业技能和方法论有关。比如在我们公司,PCB板的Layout不需要硬件工

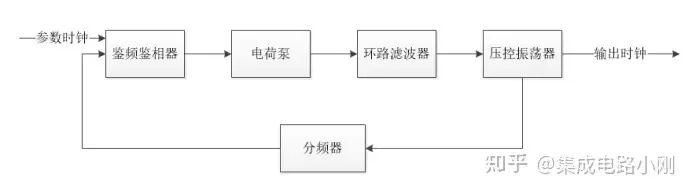

锁相环的基本原理 本章主要介绍锁相环的基本原理,主要介绍电荷泵锁相环的基本原理以及连续线性模型分析方法,在连续线性模型分析的基础上分析环路的稳定性,最后给出环路滤波器的参数的计算公式。 其中整个锁相环系统是一个相位负反馈系统,主要由鉴频鉴相器、电荷泵、环路滤波器、压控振荡器、分频器等模块组成。将分频器反馈的信号和参考时钟信号进行比较当两者的相位差为0时,环路进入稳定状态。对于锁相环在原点的个数对

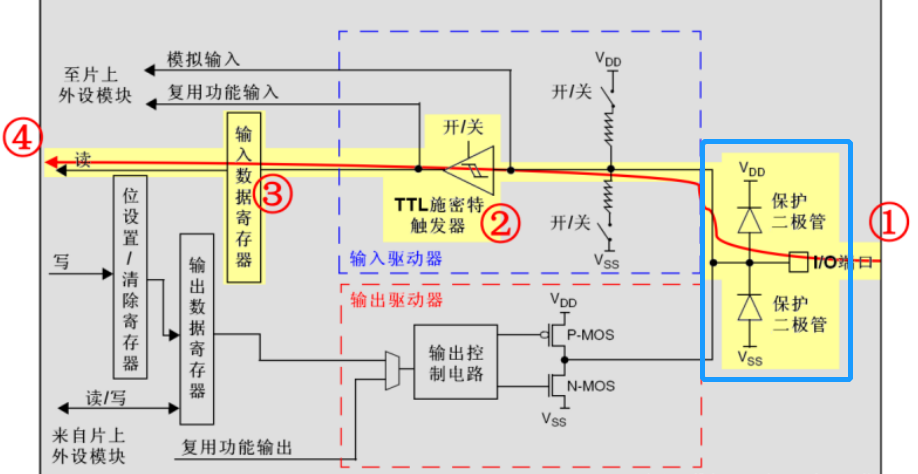

大家好,我是记得诚。 图1蓝色框内是二极管钳位电路的一般结构,多见于芯片输入端。当然还有专门的开关二极管,如下图2红色框内所示。本文主要针对此类型的二极管电路做一些简单介绍。 图1:mcu内部IO结构处的保护二极管 图2:常见的几种开关二极管 电路作用:实现二极管对异常电压的钳位作用,保护后级输入。 实现原理:下图3是用LTspice进行仿真的图形,D1和D2是肖特基二极管,正向导通压降Vf

前言 在使用 cocotb 编写测试时,很多人可能都会遇到一些让人困惑的现象:比如说,你明明在发送一帧完整数据之后,加了 await RisingEdge(clk) 想等待 5 个周期再发下一帧,但在波形上却发现帧与帧之间并没有间隔;或者你在别的地方加了 Timer 也没起作用更甚至cocotb直接卡住不动了;又或者明明指定了发包数,却提前结束了。 这些现象的背后,其实不是 cocotb 出了问题

电磁炉,这一现代厨房中的烹饪新星,凭借其独特的优势,日益受到人们的青睐。其便捷性和高效性,使得它成为忙碌现代人理想的选择。了解电磁炉在现代厨房中的角色,更是开启美食烹饪之旅的关键第一步。 电磁炉的主要电路包括以下几个部分: 1、电磁炉开机保护电路 电磁炉开机保护电路的作用是保证电磁炉在待机状态下IGBT不工作,防止电磁炉一开机(未按加热键)就加热的现象出现。该电路主要由主控IC(局部)、晶体管

公众号后台回复:DFM 对于硬件工程师而言,最紧张的时间节点就是发板前夕,画好的PCB要出Gerber文件给工厂,这Gerber文件是一定要仔仔细细检查,以前我一直用CAM350,这种检查纯靠“眼力”,简单的板子还好,遇到复杂的板子,纯靠肉眼检查的话,难免有遗漏,以至于每次发板,总是提心掉胆,尤其是第一版硬件。 今天推荐一款比CAM350还好用的软件,电子发烧友论坛出品的《华秋DFM》,支持Al

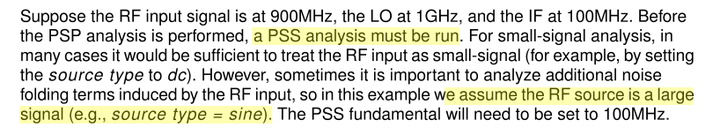

1.算法简介 在Cadence SpectrePF 里 ,psp 即 pss+sp,hbsp 即 hb+sp, 二者都是可以仿真含谐波或周期信号的S参数。与sp的区别在于,psp和hbsp仿真的是大信号S参数,sp仿真得到的是小信号S参数 psp 和 hbsp的设置基本一致,得到的结果也接近,最好不要一起跑(笔者一起跑得到的结果有误)。下面以psp为例进行说明。 2.端口设置 在端口设置上,与s

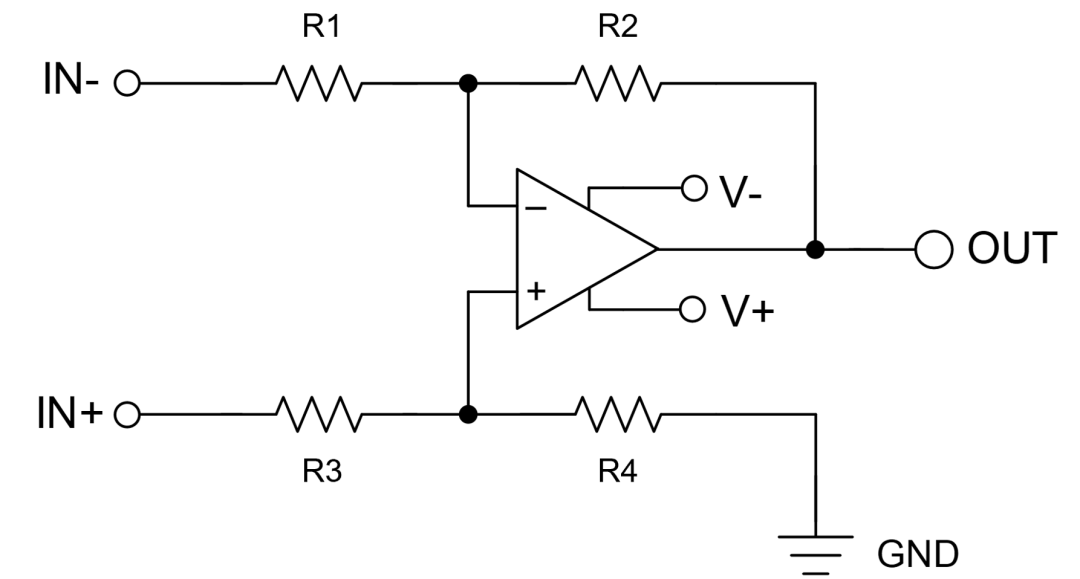

引言 利用运算放大器(运放)和电阻器网络,可以构建多种实用电路,差分放大器 (DA) 便是其中之一。借助 DA,可以测量两个信号之间的差值,这对于太阳能电池板、移动电源和其他 DC/DC 模块等系统中的电流和电压检测非常有用。此外,许多 DA 可以施加增益,向信号添加基准电压,以及抑制输入信号产生的共模噪声。 DA 主要有两种类型:分立式(使用外部电阻器)和集成式(使用单片或片上电阻器)。本文将通

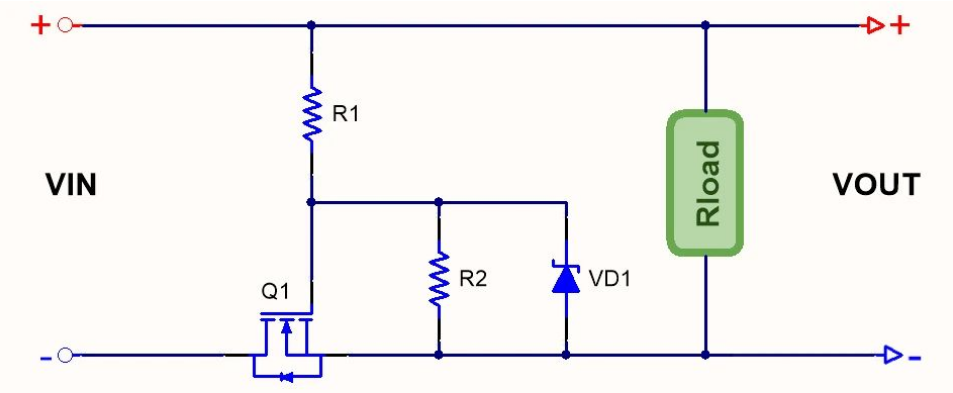

电子元件大都是使用直流工作,电源线反接就有可能就会烧坏,那电路如何防反接? 首当其冲我们想到的就是二极管了,运用其单向导通特性可有效防止电源反接而损坏电路,但是随之而来的问题是二极管存在PN节电压,通常在0.7V左右,低电流是影响不明显,但流过大电流时,如流过1A电流其会产生0.7W的功耗,0.7W的功耗发热对元件本身及周边元件的可靠性是个非常大的考验。 可见二极管防反接最大问题是管压降,越低损耗

对于许多FPGA/IC工程师而言,设计实现游刃有余,验证仿真却常成短板——传统验证方法面临两难困局:学习UVM需投入大量时间成本,而纯Verilog自仿又会陷入重复造轮子的低效循环。以通信协议仿真为例,仅报文解析就需要重写整套解析逻辑,相当于用Verilog再实现一次协议栈,耗时费力。此时,Python的生态优势便锋芒尽显。其丰富的字符串处理库可直接解析报文,配合Cocotb框架,仅需少量Pyth