芯片设计中的ESD防护设计介绍

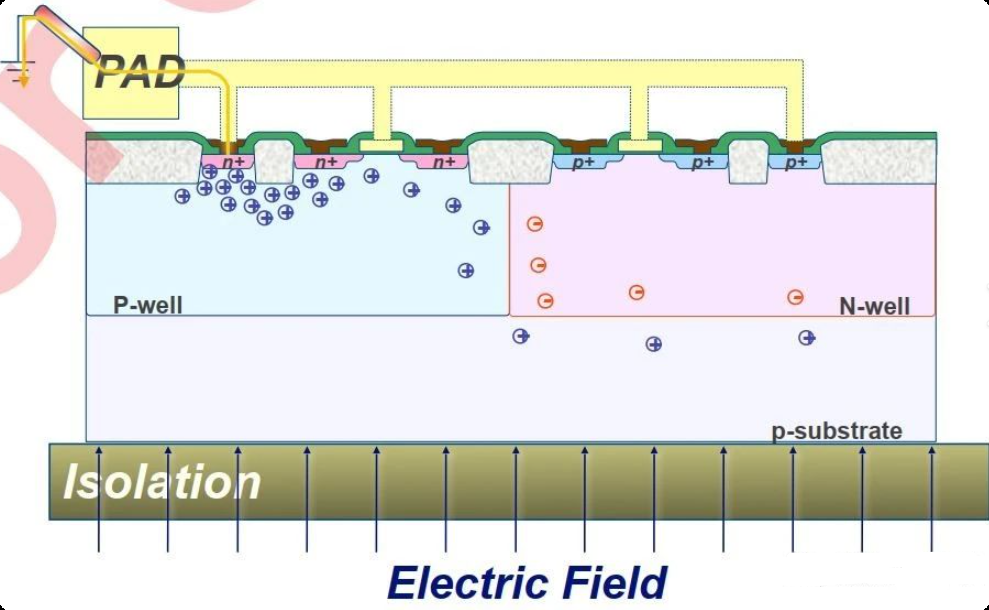

本文主要讲述芯片设计中的ESD防护设计介绍。 在集成电路(IC)的设计、制造、封装、测试及应用全流程中,静电放电(ESD)是最常见且破坏性极强的隐患之一。ESD放电时间虽仅为纳秒至微秒级,但瞬时峰值电流可达数十安培,足以击穿芯片内部的精密结构。因此,芯片设计时需要集成专用的ESD防护电路,在输入/输出引脚、电源引脚附近形成低阻抗放电通路,将静电能量旁路到地,避免核心电路受损。 ESD防护设计的核心

纳米网电路设计频道 — 提供电路设计领域最新资讯、技术文章和行业动态。

本文主要讲述芯片设计中的ESD防护设计介绍。 在集成电路(IC)的设计、制造、封装、测试及应用全流程中,静电放电(ESD)是最常见且破坏性极强的隐患之一。ESD放电时间虽仅为纳秒至微秒级,但瞬时峰值电流可达数十安培,足以击穿芯片内部的精密结构。因此,芯片设计时需要集成专用的ESD防护电路,在输入/输出引脚、电源引脚附近形成低阻抗放电通路,将静电能量旁路到地,避免核心电路受损。 ESD防护设计的核心

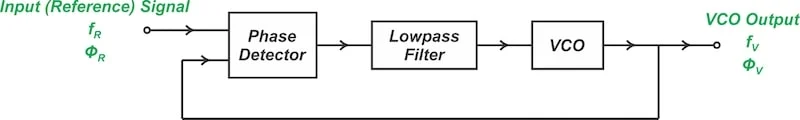

本文将了解如何用鉴相/鉴频器(PFD)替代普通鉴相器,以扩展锁相环(PLL)的捕获范围。 在学习锁相环(PLL)基础原理时,我们通常从鉴相器如何引导环路实现锁定开始讲起。但在实际应用中,许多 PLL 电路都会选择鉴相 / 鉴频器(PFD),而非单纯的鉴相器。PFD 是一种常用的时序逻辑电路,能够同时检测两路输入信号的相位差与频率差。正如本文将要介绍的,它比仅检测相位差的电路拥有更宽的捕获范围。 普

当下这社会,没有几万个Clock Gating,出门都不好意思和别人打招呼! 现在的深亚纳米工艺的设计中,低功耗已经是一个日渐总要的主题了,尤其是移动市场蓬勃发展起来之后,功耗的要求越来越严格,据传,在高级的手机系统开发的过程中,系统架构的设计,已经精确到每一个服务模块的毫安时(mAH)的级别,所以如果你的芯片功耗控制不下来,很有可能会被手机生产厂家踢出局。 在低功耗的世界里,我们有很多方法可做

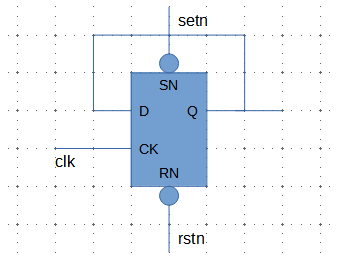

有群友提问,下面的代码为什么在DC里可以综合成DFF,而在FPGA上却综合成了latch。 always@(posedge clk, negedge rstn, negedge setn) if(!rstn) a <= 1'b0; else if(!setn) a <= 1'b1; else a <= a; 我们可以看到这段代码有两个特别之处: 同时有异

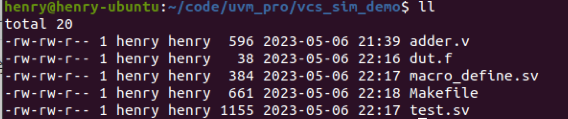

我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。 源文件内容如下: //adder.v module adder( input clk, input rst, input [9:0] A, input [9:0] B, output reg [10:0] C ); always @ ( pose

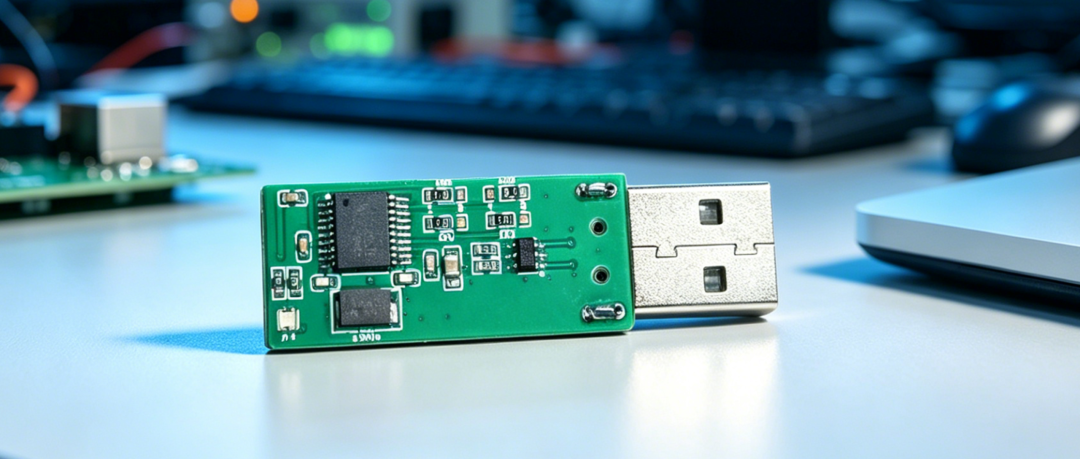

工程名称:铁电U盘 · USB FRAM DISK 前言 据说,这个U盘能做到——永久**存储、无限擦写、零延迟写入、还抗辐射?** 这4个特点,代表了这个U盘能: ——“永远”不坏 ——且每次打开,储存的资料都在 而且做一个这样的U盘只花10元?! 所以……它咋做到的?真能做到? 先瞅瞅它的电路设计和硬件参数! *0***1 设计图 ” 电路部分,作者只用了一颗主控+一颗FRAM。 原理图

一、红胶 红胶是一种聚烯化合物,受热后容易发生固化,当它所受的温度达到150℃凝固点时候,红胶就开始由膏状体变成固体,利用这一特性,可以用点胶或者印刷的方式对贴片元器件进行固定,线路板元件使用贴片红胶可以通过烤箱或者回流焊进行加热固化。 线路板上的元件,特别是双面贴装的线路板,过波峰焊的时候使用贴片红胶固定,可以让背面的小型贴片元件不会掉落到锡炉中。红胶有几大特点: ①对各种芯片元件均可获得稳定

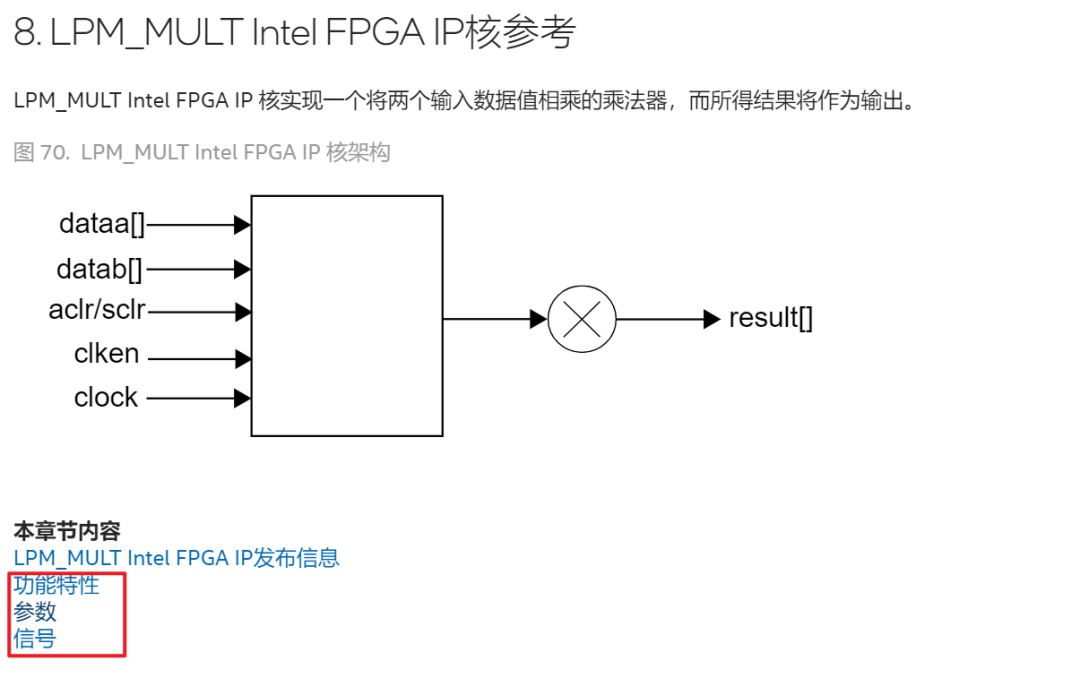

在进行编码时,我们时常会使用到乘法器,除法器,等较复杂功能模块,为此fpga vendor设计定制了IP核,用户通过调用IP核来实现所需功能,耗费资源少且利于时序收敛。我们在日常verilog编码过程期望通过参数化的方式调用IP核。例如IP的位宽,时延,部分关键特性期望可以通过参数调用的方式实现,而不是通过打开GUI界面通过手动选择的方式实现。其实实现方式很简单。首先通过手动打开quart

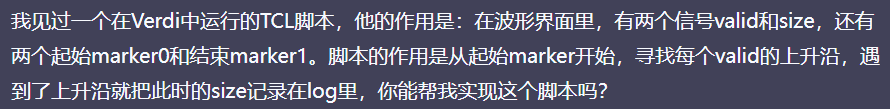

这个脚本在多年之前我就想做出来的,算是很执念的一件事。但是无奈自己的tcl编程能力和Verdi相关指令行掌握的太弱了,尝试了几次都没有成功。而这次我决定借助大模型力量再试一次,所以对着DS描述了这个脚本的行为: 但是后面想了想,描述的不够准确,于是进行了第二次描述: 其实想要的效果就是这样的(完成版): 讲真当年看到这个脚本的实现效果时真的是迷得我走不动道,所以这次必须要实现出来。 要在Ve

文章**概述** 在查看 DigiKey 上的变压器规格时,不少工程师会注意到参数表中出现 “初级阻抗”与 “次级阻抗”。但这往往会引发疑问: 变压器本身到底有没有阻抗? 参数中列出的初级/次级阻抗该如何理解? 这些阻抗是否等同于电力行业常提到的“百分比阻抗”或 Z%? 本文将结合一位用户的问题与工程师的专业解答,对上述概念进行系统说明。 一、原始问题: 用户的理解包括两点: 变

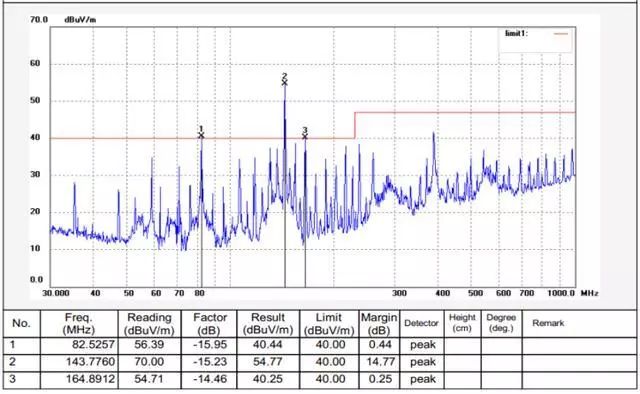

大家好,我是记得诚。 晶振在布局时,一般是不能放置在PCB边缘的,今天以一个实际案例讲解。 某行车记录仪,测试的时候要加一个外接适配器,在机器上电运行测试时发现超标,具体频点是84MHz、144MHz、168MHz,需要分析其辐射超标产生的原因,并给出相应的对策,辐射测试数据如下: 图1:辐射测试数据 1、辐射源头分析 该产品只有一块PCB,板子上有一个12MHz的晶体。其中超标频点恰好都是12

前言 开源 AFX-SATA-DMA 控制器:高速存储接口的完整实现(附源码) SATA 的开源并不是我的主要目的。这个项目最初的出发点,其实是想借此验证和实践 cocotb 仿真的完整流程,以及构建一套自主可控的 FPGA 开发工具链。可以说,是为了这点醋,才包了这顿饺子。不过既然 SATA 协议都已经实现出来了,索性就把它开源出来。开源的好处是双向的:对大家来说,可以借此深入学习SATA 协议

一、电容选型的关键参数 在选型之前,我们需要明确电容的几个关键参数,这些参数将直接影响电容的性能和适用场景: • 容量(Capacitance):电容存储电荷的能力,单位是法拉(F),常用单位有微法(μF)、纳法(nF)和皮法(pF)。 • 额定电压(Voltage Rating):电容能够承受的最大直流电压,超过该电压可能会导致电容损坏。 • 等效串联电阻(Equivalent Series

在设置input_delay时,我们经常会使用下面的方式: set_input_delay -clock clk -min 2 [get_ports data_in] set_input_delay -clock clk -max 4 [get_ports data_in] 但有时也会在后面增加一个-add_delay的参数: set_input_delay -clock clk -max 2.1

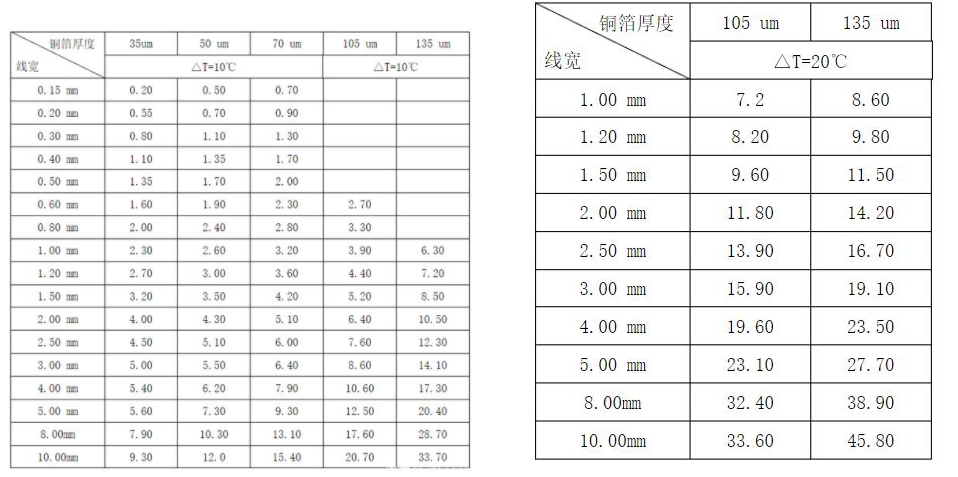

通常的PCB设计电流都不会超过10A,甚至5A,尤其是在家用、消费级电子中,通常PCB上持续的工作电流不会超过2A。 但是最近要给公司的产品设计动力走线,持续电流能达到80A左右,考虑瞬时电流以及为整个系统留下余量,动力走线的持续电流应该能够承受100A以上。 那么问题就来了,怎么样的PCB才能承受住100 A的电流? 方法一:PCB走线 要弄清楚PCB的过流能力,我们首先从PCB结构下手。 以双

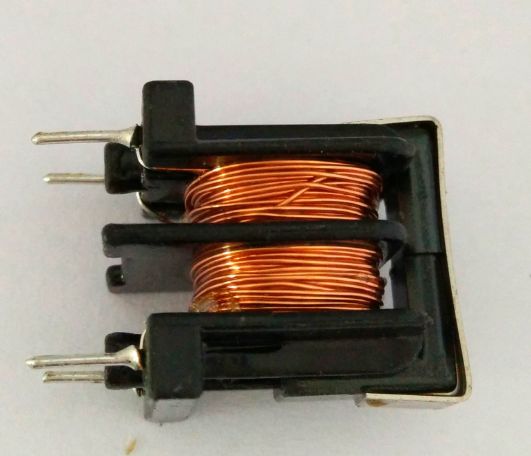

一、共模电感的作用、原理 相信对于共模电感很多人都不陌生,但是对它的接法你是否完全理解呢?你的电路上的共模电感是否接对了?首先我们来认识一下共模电感。 共模电感一个以铁氧体为磁芯的共模干扰抑制器件,它是由两个尺寸相同、匝数相同的线圈对称地绕制在同一个铁氧体环形磁芯上,形成一个四端器件,共模电感对交流电流起着阻碍的作用。对于插件电感,我们一般见的比较多的就是UU型和EE型以及环型等。 在交流电频率

闭环增益传递函数的推导核心是基于信号反馈原理,通过建立输入、输出与反馈信号的关系,消去反馈变量后得到输出与输入的比值。以下是典型负反馈系统的推导步骤: 明确系统基本模块与变量 负反馈系统包含3个核心模块,各变量定义如下: 输入信号: R(s) (系统期望的输入) 前向通道传递函数: G(s) (输入到误差信号再到输出的传递关系) 反馈通道传递函数: H(s) (输出信号反馈到输入端

01 前言 记录个使用SystemVerilog disable语句时遇到的坑,这个坑有点反直觉,以至于我当时有点不信,觉得可能是EDA仿真工具的问题。后来查看了SystemVerilog手册和使用不同EDA工具进行验证,才慢慢接受了。结论是:SystemVerilog disable block_name或task时,会把hierarchy一致的block_name或task的线程都停掉。 02

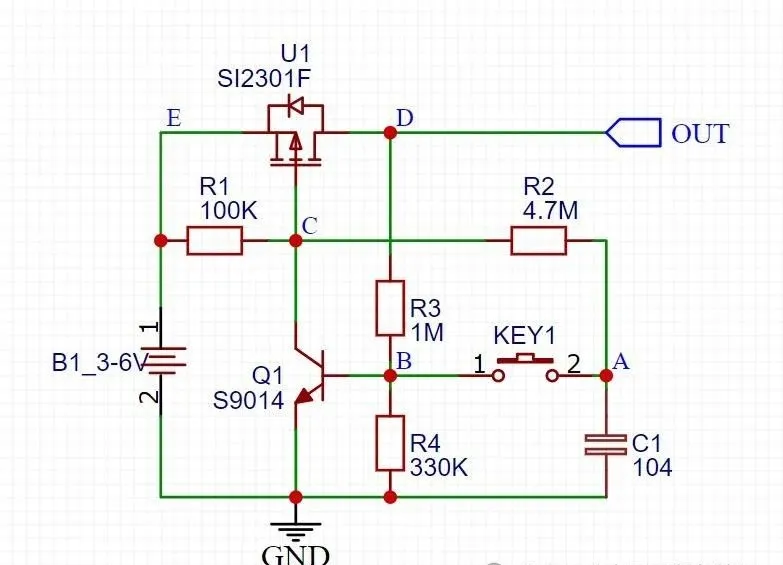

最近从网上看到一个单键电子开关电路,觉得还挺有意思的,比较适合DIY。 虽然之前也分析过一个单键电子开关电路,但是相对来说,当时的电路还是比较繁琐的,用的器件比较多,而且有一定的静态功耗,不算是一个合格的电子开关电路。 现在这个电路呢,用的器件不多,然后工作原理也比较巧妙。在这里简单的分析一下,希望可以帮到一些电子爱好者。 单键电子开关电路 这个电路用在3-6V的直流电路中。上电默认是没有输出的

PCB工程师在设计PCB时,对于高速电路板或电路板上的关键信号会经常涉及到到“做阻抗”、“阻抗匹配“的这些问题。 首先解释下什么是阻抗匹配: 阻抗要求是为确保电路板上高速性号的完整性而提出,它对高速数字系统正常稳定运行起到了关键性因素,在高速系统中,关键信号线不能当成是普通的传输线来看待,必需要考虑其特性阻抗,若关键传输线的阻抗没有达到匹配,可能会导致信号反射、反弹,损耗,原本良好的信号波形变形(