本文主要讲述外延应力如何提升芯片性能。

在追求更高性能的征途中,工程师们发现了一个免费午餐——应变硅技术。通过在特定区域引入晶格应力,可以显著提升载流子的迁移率,从而在不缩小尺寸的情况下提高晶体管的驱动电流。其中,选择性外延生长是施加应力的核心手段。那么,应力是如何从外延层“传递”到有源区(AA),又是如何改变晶体管电性的呢?

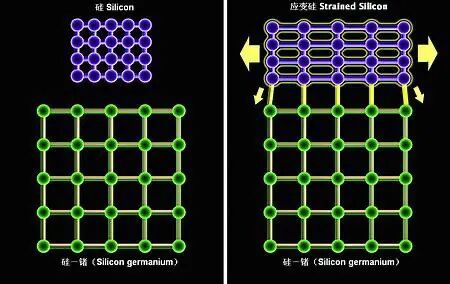

应力从何而来:外延层的“原子尺码不匹配”

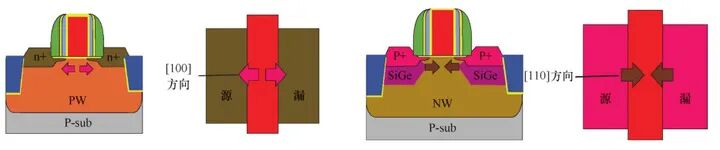

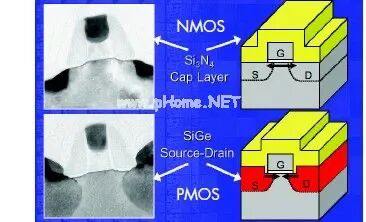

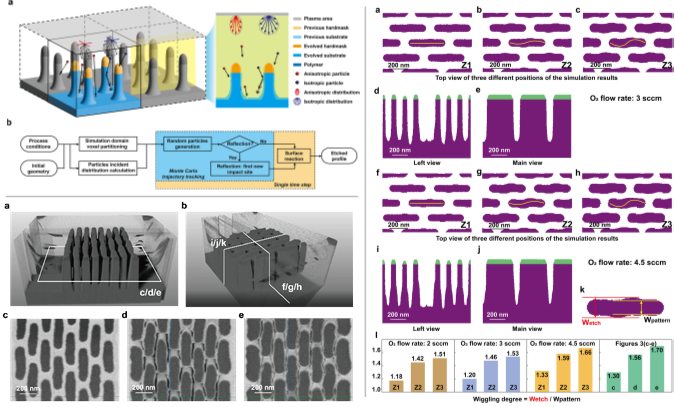

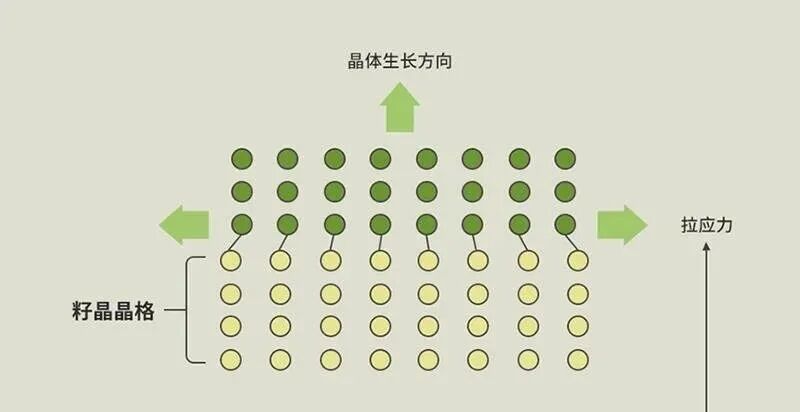

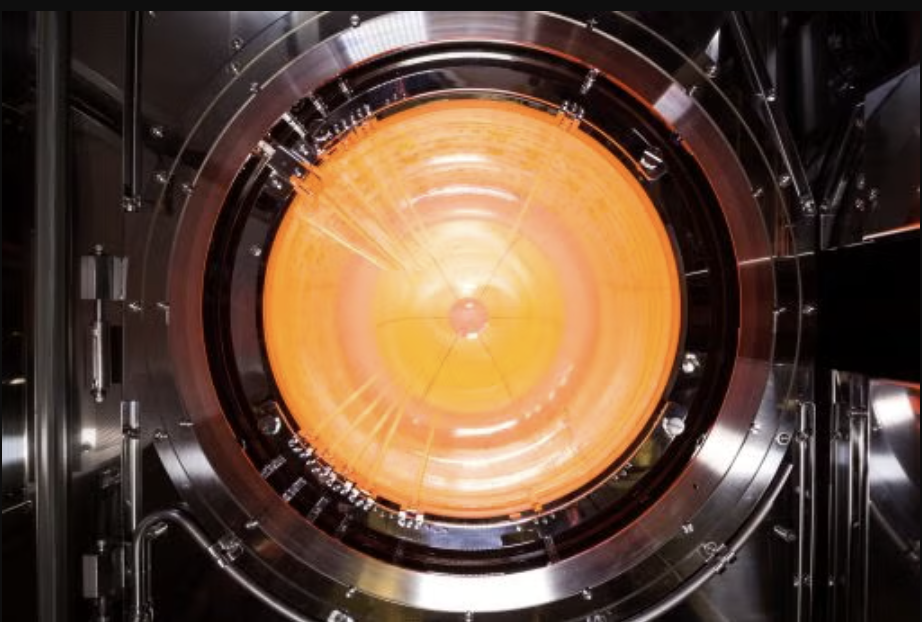

应力的源头,在于两种材料原子尺寸的差异。以PMOS晶体管为例,在源漏区选择性外延生长锗硅(SiGe)。锗原子的共价半径比硅大约4.2%,当SiGe外延层生长在单晶硅衬底上时,锗原子“挤”不进硅的晶格位置,导致外延层的晶格常数比下方的硅更大。但由于外延层与硅衬底是共格生长(原子一一对应),大晶格的SiGe被迫“拉伸”还是小晶格的硅被迫“压缩”?实际上,是两者相互妥协:SiGe层受到压应力(被压缩),而硅沟道区则受到张应力?等等,这里需要澄清。对于PMOS,我们希望在沟道中引入压应力,以提高空穴迁移率。典型做法是在源漏区外延SiGe,由于SiGe的晶格常数大于硅,外延层会试图“膨胀”,但被下面的硅衬底“拉住”,导致SiGe层自身承受压应力。同时,这种压应力会通过源漏区传递到沟道,使沟道硅晶格在电流方向上被压缩,即沟道承受单轴压应力。对于NMOS,则希望引入张应力,常用方法是源漏外延碳化硅(SiC),碳原子比硅小,外延层晶格常数小,对沟道产生拉伸作用,形成张应力。

应力如何“传递”到有源区:力学路径

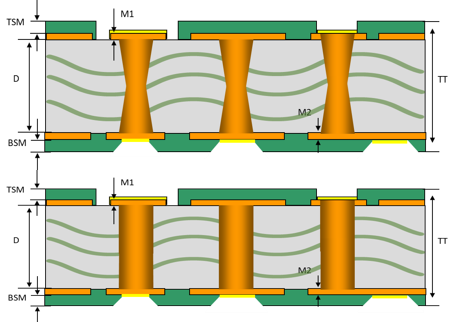

应力从源漏外延层传递到沟道,依赖于结构的连续性。在FinFET或平面晶体管中,源漏区与沟道区是同一块单晶硅,通过外延生长在源漏区上方加厚一层SiGe或SiC后,外延层与下方硅形成牢固的共格界面。由于整个源漏-沟道-源漏是连续的晶体,外延层中的应变会通过原子键的弹性形变传递到沟道区域。具体来说,SiGe外延层试图恢复其自然晶格常数,但被周围的硅约束。这种“挣扎”产生的应力通过源漏区侧壁作用于沟道两端,类似于从两端向中间挤压,使沟道硅的原子间距在电流方向上缩短,形成压应力。模拟显示,这种压应力可以高达数百兆帕到吉帕级别。

应力如何改变电性:能带结构与载流子迁移率

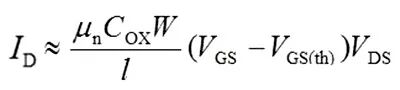

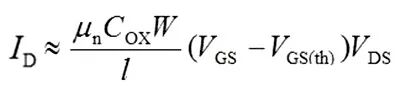

应力的核心影响在于改变硅的能带结构,从而影响载流子的有效质量和散射几率。对空穴(PMOS)的影响:硅的价带由重空穴带和轻空穴带组成,重空穴有效质量大,迁移率低。当施加单轴压应力时,能带发生分裂和扭曲,重空穴带与轻空穴带的能量间距增大,空穴更多分布在有效质量更小的轻空穴带,同时带间散射减少。因此,空穴迁移率显著提升。实验表明,约1GPa的压应力可使空穴迁移率提高50%以上。迁移率提高直接导致饱和电流(Idsat)同比增加,因为Idsat ∝ 迁移率 × 栅电容 × (Vgs-Vth)^2。对电子(NMOS)的影响:张应力使硅的导带发生能谷分裂。硅的导带有六个等价能谷,张应力使垂直于应力方向的四个能谷能量升高,平行于应力方向的两个能谷能量降低,电子优先占据有效质量较小的能谷,从而提升电子迁移率。张应力还可降低电子的谷间散射,进一步增加迁移率。

对阈值电压(Vth)的影响:应力也会轻微改变Vth,但机制更复杂。应力通过压电效应改变硅的禁带宽度,进而影响本征载流子浓度和表面势。通常,压应力会使PMOS的Vth绝对值略微降低(更易开启),而张应力对NMOS的Vth影响较小。总体而言,Vth的偏移通常可通过沟道掺杂微调来补偿,而迁移率提升带来的Idsat增益是主要受益。

工程实现与收益

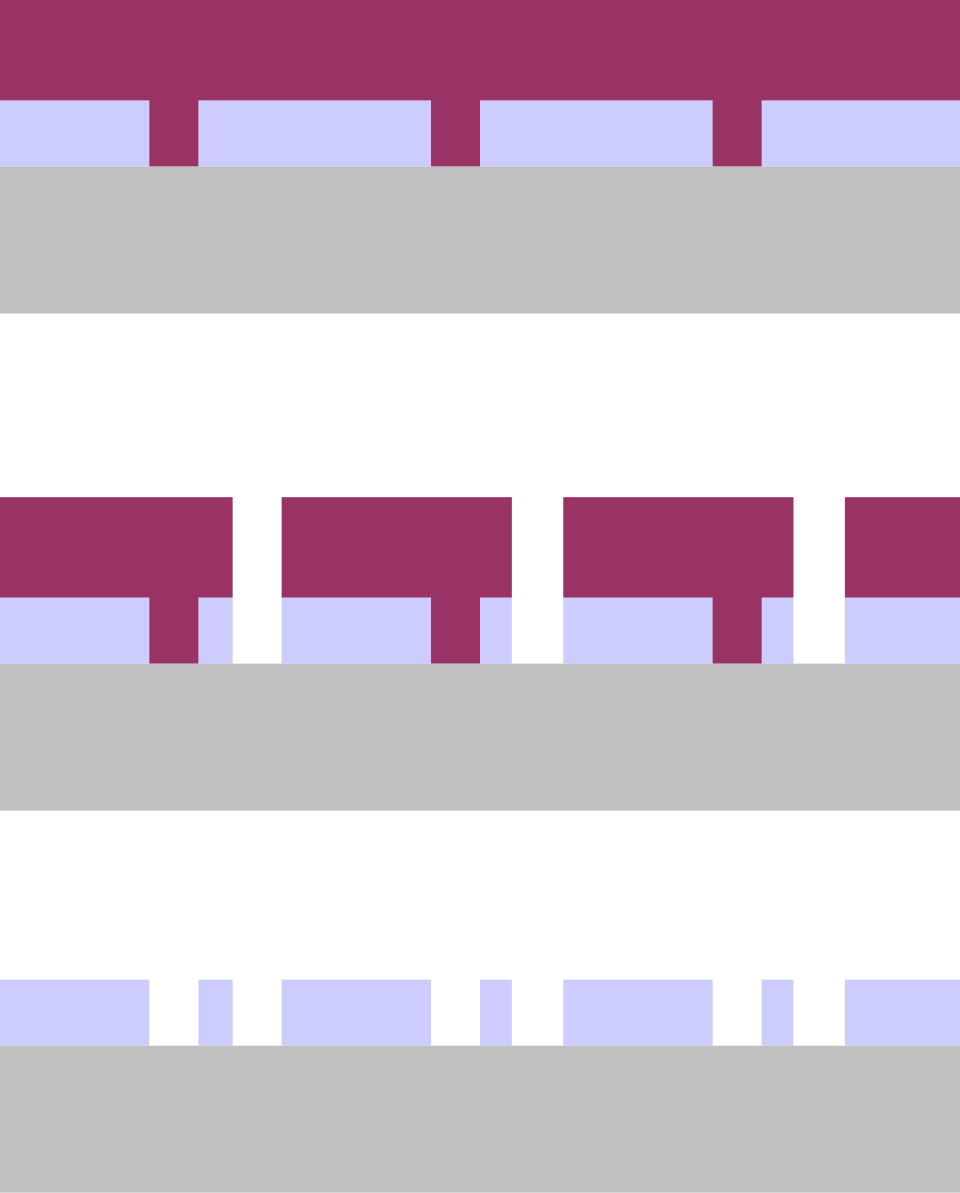

在先进工艺中,通过选择性外延在PMOS源漏区生长SiGe(锗浓度通常20%-40%),在NMOS源漏区生长Si:C(碳浓度1%-2%),再结合后续退火激活,可稳定地将应力锁定在沟道中。这种应变硅技术与栅极结构(如FinFET、GAA)兼容,已成为从90纳米到3纳米节点的标准工艺。实际数据显示,合理优化的应变工程可使PMOS的Idsat提升30%-50%,NMOS提升10%-20%,而几乎不增加漏电。这种“免费”的性能提升,是摩尔定律得以延续的重要推手之一。

结语

外延应力技术通过原子尺度的“尺码不匹配”,将应力精准地施加到晶体管最核心的沟道区域,重塑硅的能带结构,为载流子“提速”。它不改变晶体管的基本开关原理,却让同样的物理尺寸跑出更快的速度。这就像给短跑运动员穿上了专业钉鞋——鞋钉与跑道之间的微观咬合,释放出更大的爆发力。在芯片性能的竞赛中,这种原子级的“巧劲”,与光刻微缩同等重要。

评论区

登录后即可参与讨论

立即登录