本文主要讲述Via Post工艺。

Via Post Coreless(无芯铜柱法工艺)

Via Post 铜柱法无芯工艺,为越亚半导体(ACCESS)自研专利技术。作为国内早期布局IC封装载板量产的企业,越亚率先打破海外技术垄断,也是全球首批依托自主专利「铜柱增层法」,实现无芯IC封装载板规模化量产的厂商。

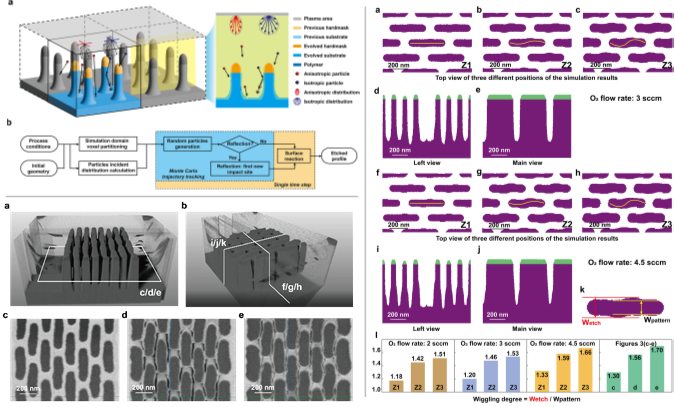

该工艺核心为越亚自主研发的干膜导通层控制技术,通过自孔底向上电镀成型铜柱导通孔,无需业界通用工艺的激光钻孔+电镀填孔流程,在无芯制程体系中形成差异化技术优势。

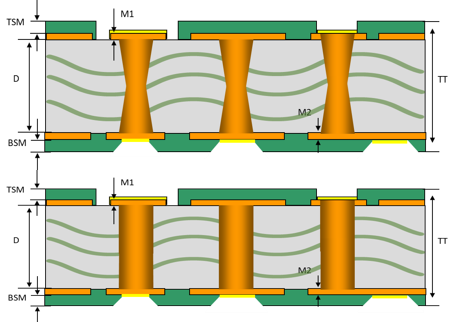

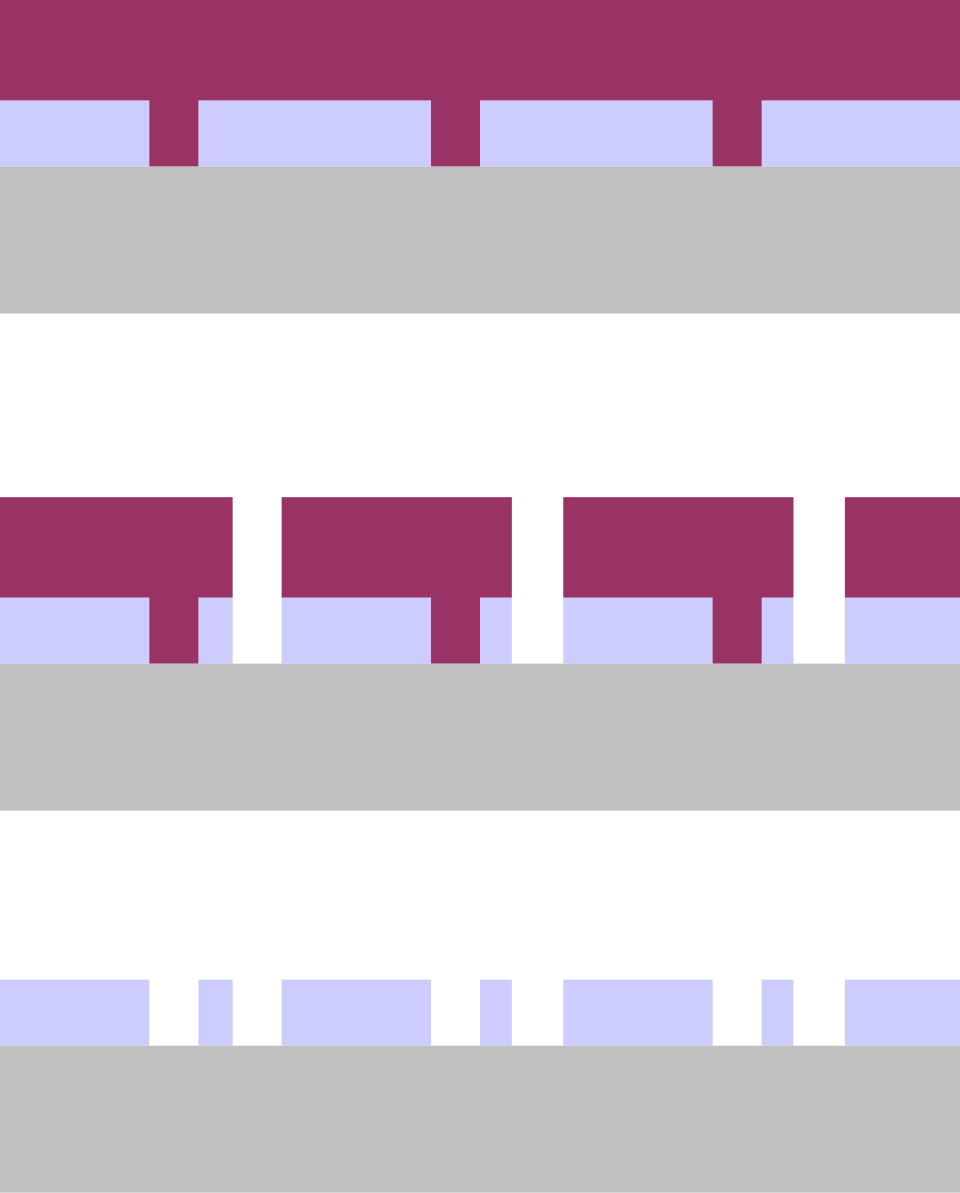

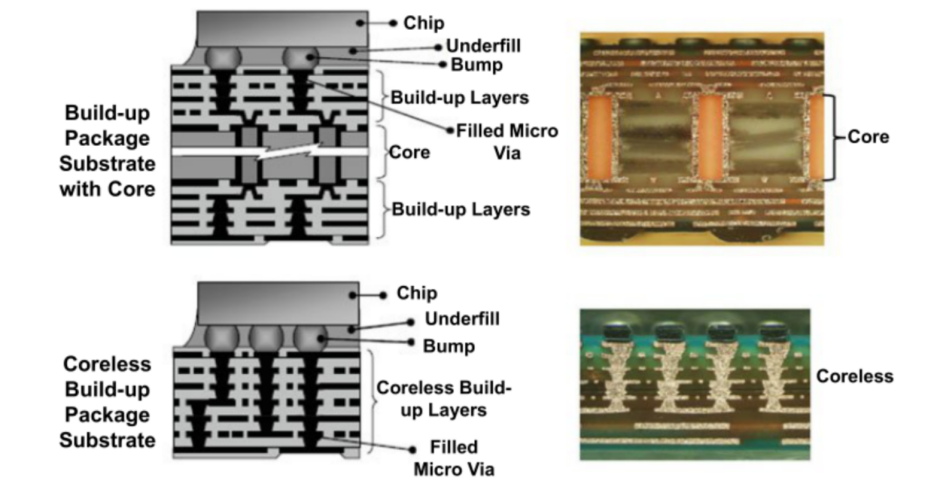

上为mSAP简单产品图示,下为Via Post简单产品图示

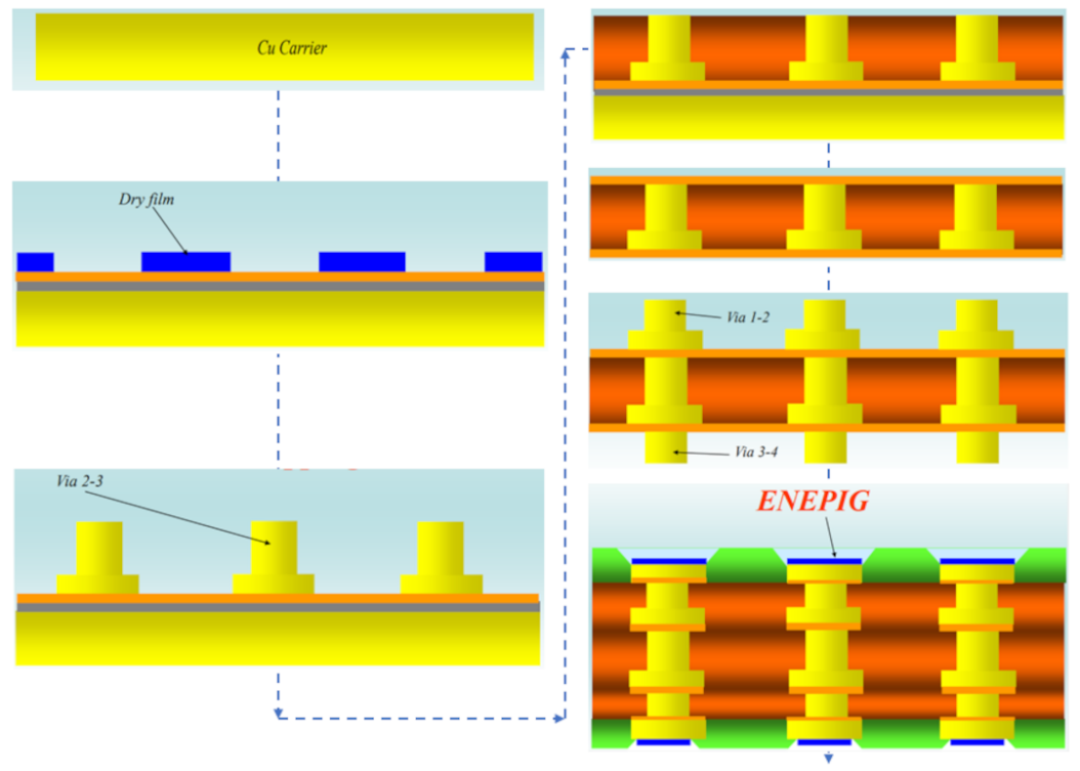

Via Post载板产品工艺流程

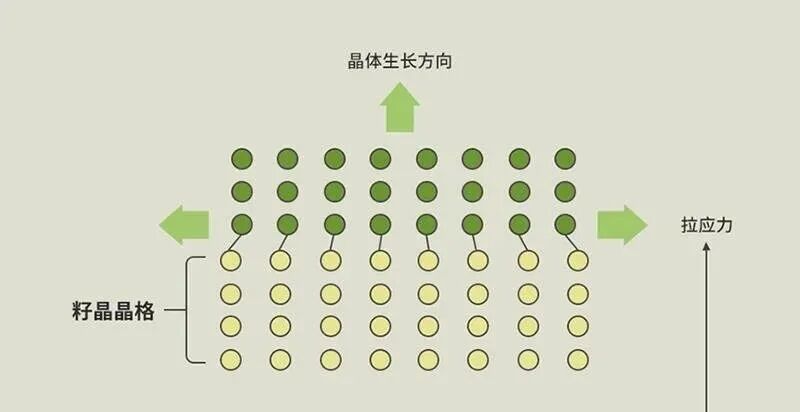

1、基础载体层准备:以Cu Carrier(铜载体)作为核心支撑骨架,在载体表面沉积导电种子层(Sputtering seed layer),为后续电镀工艺做准备。

2、图形与结构定义:压合介质层(绝缘层)并覆盖整个Cu Carrier;使用干膜直接曝光定义,确定铜柱贯穿位置(开窗)及待互连的层间结构。本环节无需激光钻孔,由干膜直接定义孔位。

3、电镀铜柱(Via Post)成型:采用自下而上电镀(Bottom-up Plating)方式生长铜柱:从Cu Carrier表面开始向上填镀,完全填充通孔,形成垂直互连结构,完成单次层的铜柱+介质层构建。

4、多层重复增层:重复步骤2-3:压合新介质层、使用干膜定义新一层图形、电镀铜柱,即可形成任意层互联(Any-layer Interconnection),各层间结构可独立定义,不依赖固定孔位。

5、表面处理:在最外层结构上进行ENEPIG(镍钯金)表面处理,以降低接触电阻、提升焊料可靠性,形成芯片/器件与基板的稳定焊接点。

流程图如下:

Via Post产品工艺流程

通过上述结构,可看出Via Post特点:

1.无传统核心板材(Core);

2.采用任意层起始的顺序增层制程;

3.依托铜柱工艺,实现任意层间互联;

4.依托铜柱工艺,支持任意形状互联结构;

5.可实现超薄介质层堆叠,打造轻量化封装载板;

6.以电镀铜柱/铜块作为芯片垂直散热通道,提升导热性能;

7.采用电镀铜柱替代传统机械钻孔、激光镭射钻孔,完成层间导通;

8.利用电镀铜柱/铜块成型,作为腔体(Cavity)加工方案;

9.以电镀铜柱或铜凸点,作为芯片与载板的焊接连接点位。

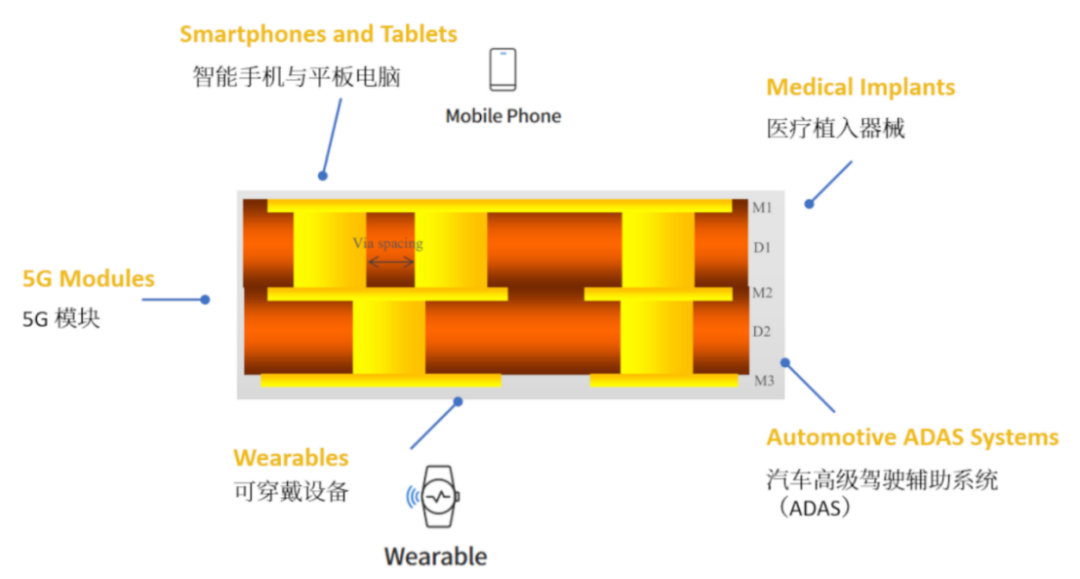

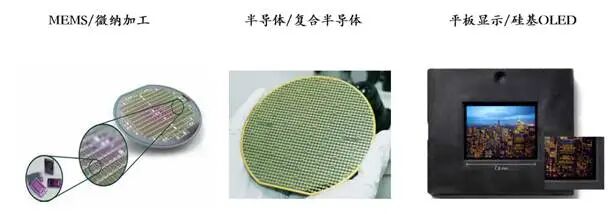

Via Post产品终端应用场景

总结越亚的Via Post优势:

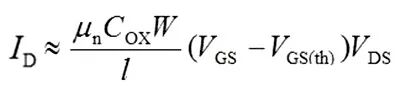

1、实心铜贯通孔结构优势:层间导通孔采用实心铜完全填充,孔壁垂直度优异,电流通流能力与散热性能表现突出,且无电镀凹陷(Dimple)缺陷,保障了互连的稳定性与可靠性。

2、高密度任意层互连能力:基于铜柱工艺实现高可靠、高密度的任意层互连,支持多种通孔形状。与业界通用工艺(mSAP)相比,Via Post技术突破了连续垂直堆叠孔的可靠性限制,可实现多层贯通孔堆叠,帮助客户减小产品尺寸、提升I/O密度。

3、基于光刻的高自由度图形定义:依托SSAP工艺的顺序增层制程,所有层可采用统一设计规则。Via Post是通过光刻直接定义线路与铜柱形状,一方面可实现任意图形结构,降低设计复杂度;另一方面为客户提供了更高的设计自由度,充分满足创新需求。

4、集成式散热与电源传输架构:结合上述工艺优势,可进一步实现连续贯通的大铜块结构PHS2®(Plated Heat Spreader)贯穿整个基板,有利于构建高散热、低损耗的电源传输路径,对PMIC(电源管理)等对散热与电源效率敏感的产品,具备更显著的性能优势。

评论区

登录后即可参与讨论

立即登录