本文主要讲述封装载板制造特殊工艺。

在行业通用的载板制造领域中,除了减成法(Tenting)、改良型半加成法(mSAP)、半加成法(SAP)这三种主流核心技术路线外,还包含无芯工艺(Coreless)、嵌入式线路工艺(ETS,即 Embedded Trace Substrate/Embedded Pattern Process)、无芯铜柱法工艺(Via Post Coreless)等特殊工艺。

这些特殊工艺凭借自身独特的产品特性,以及在结构设计、布线精度、性能表现上的差异化优势,精准填补了高端封装场景的应用缺口,成为适配不同终端需求、在各细分领域发挥核心价值的特色技术路径。

本次重点讲解无芯工艺(Coreless)及其变种工艺——嵌入式线路工艺(ETS),解析工艺原理、核心优势与适用场景。

Coreless(无芯载板工艺)

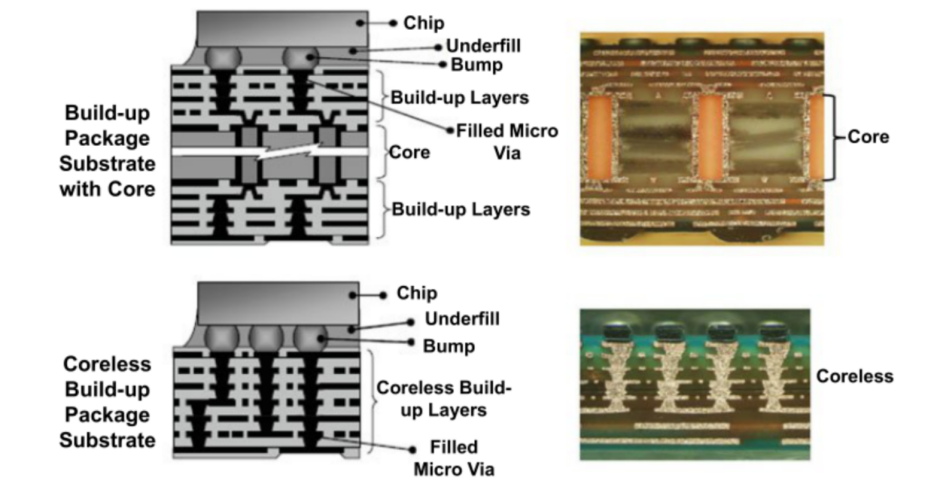

无芯载板于2006年由富士通公司首次提出,其全称为无芯封装载板(Coreless Substrates)。它是一种移除了传统刚性芯板(Core)、完全由高密度积层(Build-up)结构构成的有机封装载板,核心设计目的是实现电子产品的轻薄化、小型化,满足高端封装的尺寸需求。与传统带Core的有机封装载板相比,其最显著的区别在于:无芯载板不含芯层(core),所有层均为积层(build-up)结构,无刚性芯板支撑。同时,它具备超薄、低介电常数(Low Dk)、低损耗因子(Low Df)的核心特点,适配高精度、小型化的封装需求,广泛应用于高端芯片、便携电子等对尺寸和性能要求较高的场景。

传统带积层的有机封装基板与有机无芯封装基板对比

ETS/EPP(埋线路工艺)

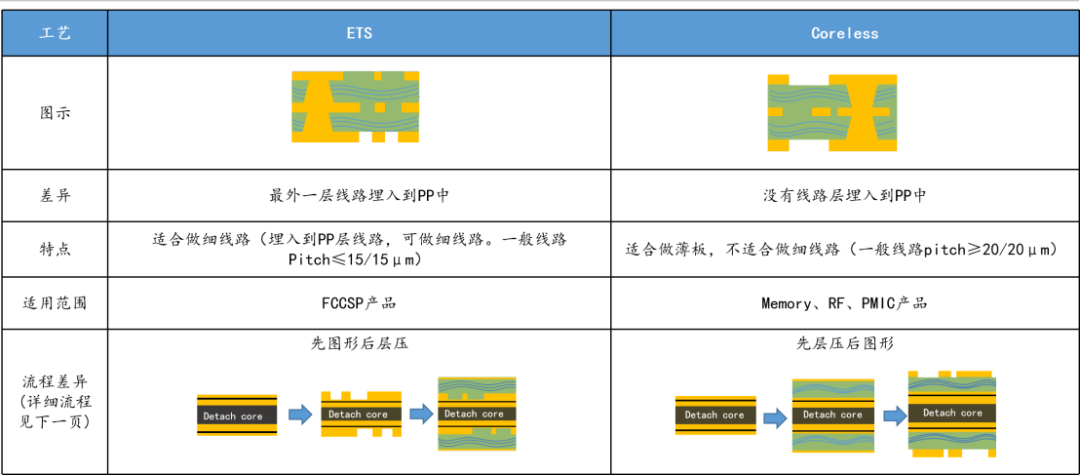

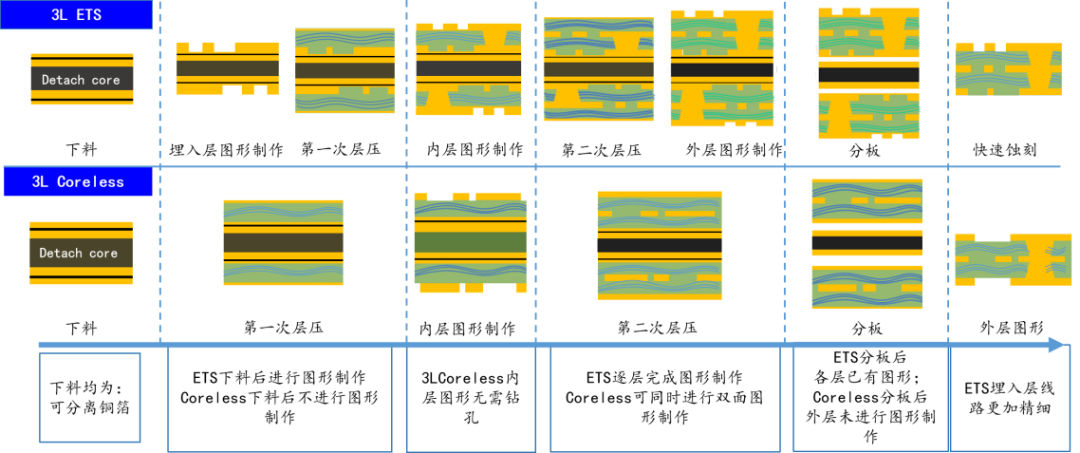

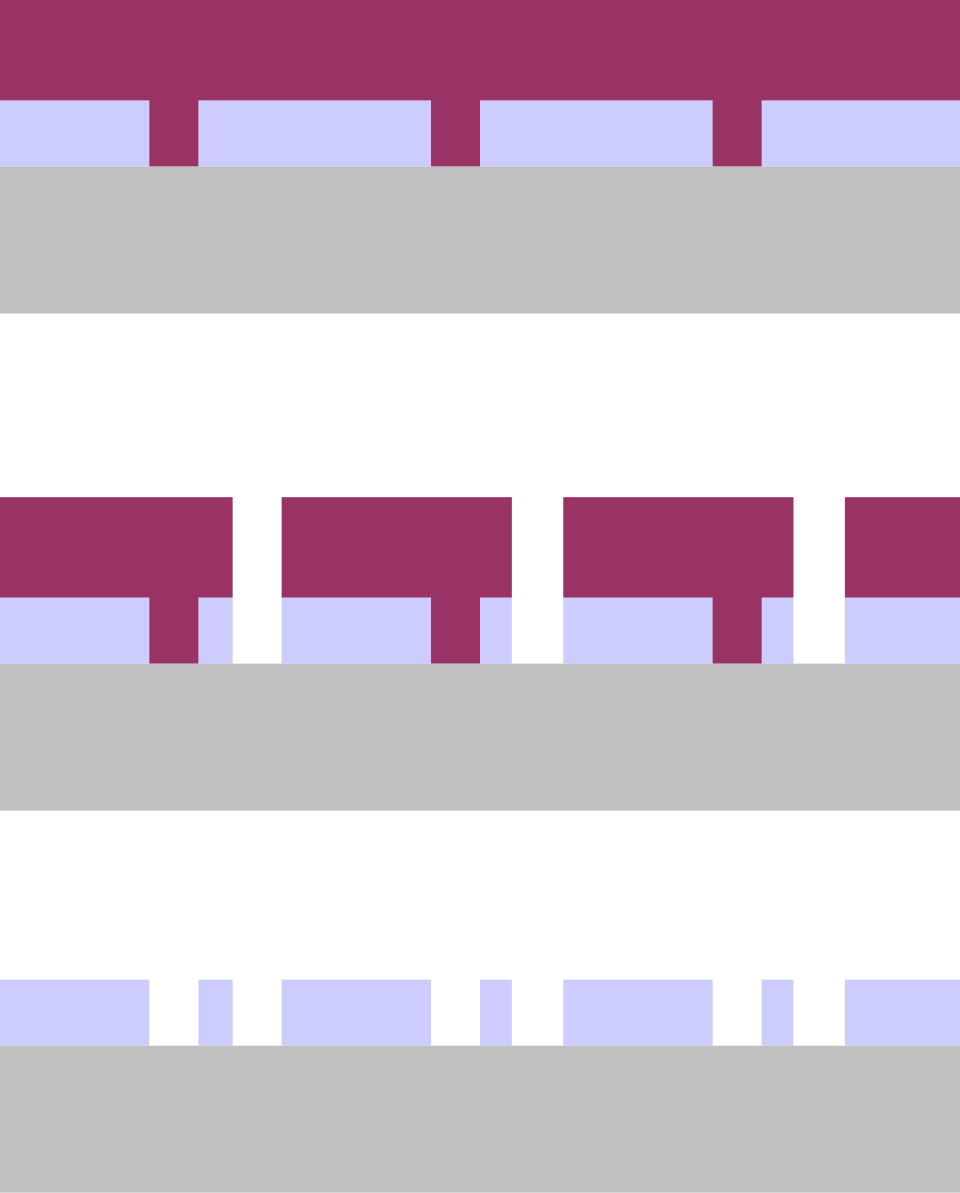

ETS工艺又称平齐基板,取其线路与PP(半固化片)平齐之意,其英文全称为Embedded Trace Substrate/Embedded Pattern Process,是在Coreless(无芯)工艺基础上迭代优化而来的先进封装载板制造技术。其核心原理是通过可剥离载体(Detach Core)实现线路的嵌入式成型,具体流程如下:先在可剥离的Detach Core载体上精准制作线路图形,随后通过层压工艺将PP与载体线路紧密贴合,使Carrier(载体)上的线路完全嵌入PP介质层中;待分板完成后,通过蚀刻工艺去除载体底铜,最终形成符合要求的导电图形。

与mSAP(改良型半加成法)工艺相比,ETS工艺具备两大核心优势:一是细间距能力更强,由于线路图形被完整嵌入PP介质内部,无需进行侧边蚀刻,有效避免了侧边蚀刻带来的线路精度损耗,可实现更精细的线路布局;二是薄型化能力突出,依托Detach Core载体的稳定支撑,能有效控制载板厚度,轻松满足薄型化产品需求,适配高端芯片小型化、高密度的封装要求。

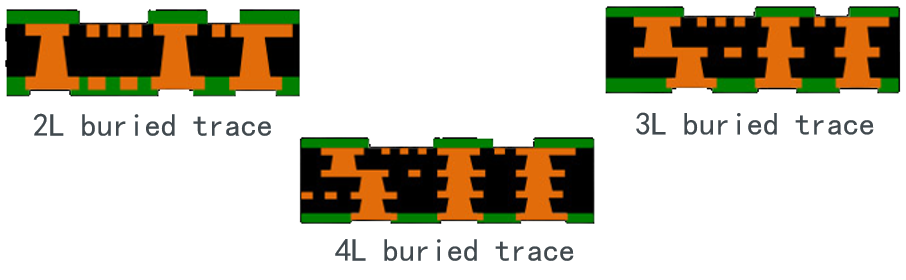

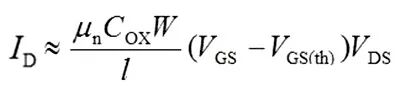

在埋入线路基板(ETS)中,电路图案位于绝缘材料内部,且ETS工艺具备无芯结构,这使得微电路的实现无需额外成本,同时大幅降低层数缩减的难度,可轻松实现从4层到3层的层数优化。此外,由于蚀刻工艺不受图案宽度的影响,电路宽度能够得到精确控制,这也让ETS技术成为大规模封装基板生产中,构建线宽/线距(L/S)<12μm精细线路图案的新方法,目前业内已知该技术可实现的最小线宽/线距为5/5μm。

目前,埋入线路基板(ETS)技术主要用于在两层、三层或四层基板中构建单一电路层,且该工艺可进一步扩展为垂直堆叠多层ETS图案,满足更高密度的封装需求。需要注意的是,ETS线路与顺序式积层加成法(SAP)线路存在明显区别:ETS线路集成在覆铜板(CCL)的介电层内,而SAP线路则位于覆铜板介电层之上,不过这两种线路的形貌一般均呈矩形,可保障信号传输的稳定性。

不同层数ETS基板图示

实现ETS工艺的两种方法

Pattern Plating approach(图形电镀法)

Detach Core是构建精细线路图案的支持基础。一般使用薄干膜(厚度<25μm)来实现精细线路,线路铜厚一般在10~15μm。然后再通过压合分板将图案集成到半固化片(Prepreg)中,再分板后蚀刻掉底铜。导通孔一般从埋线层的另一面用Laser的方式烧蚀出(盲孔)。

同时PP材料富含树脂,可以保护线路铜不会直接接触到玻璃纤维,防止后续基板产生导电阳极丝(CAF)缺陷。

目前业内较多使用此工艺(广芯基板/兴森快捷/越亚半导体/安捷利美维等)。

Laser Trenching approach(激光刻槽法)

普通Core材,在该板材一面先生成图形,另一面进行激光蚀刻。利用激光在板材无图案的表面精确烧蚀出具有精细间距的高密度电路图案,同时烧蚀出盲孔。随后,使用特殊的电镀工艺对板材的ETS面次进行全板电镀。

这种电镀工艺主要在沟槽和过孔内沉积金属,最大程度减少后续需要通过闪蚀去除的多余铜。

需要注意的是,由于激光烧蚀图案化的速度相对较慢,该工艺的产能低于激光直接成像(LDI)。此外,任何烧蚀不规则情况,都可能在最终产品中造成潜在缺陷(比如烧蚀深度过大或过浅)。

Coreless与ETS差异比对

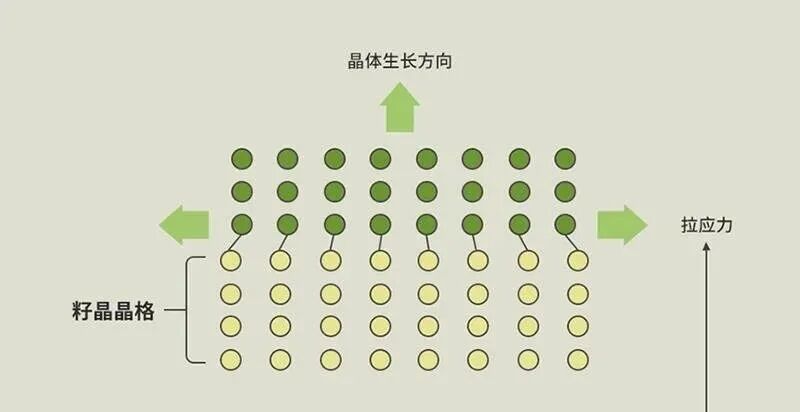

需要补充的是:上述所有Coreless(无芯)工艺的实现,均需依托Detach Core(可剥离载体)。而Detach Core是一种采用反向压合工艺制成的超薄铜箔芯板,其铜箔的剥离结合力主要由剥离层进行精准控制。剥离层主要分为有机粘结剂与无机粘结剂两大类,其中无机粘结剂可灵活调整剥离拉力强度,能够充分满足市场多样化的生产需求。

Coreless无芯工艺与ETS埋线路工艺,是突破传统封装基板局限的关键技术之一,既实现了产品的轻薄化、高精度,又通过可剥离载体的设计,降低了生产难度、提升了产品可靠性。二者各有侧重,能够精准匹配不同终端的封装需求,为载板制造的高端化升级提供了重要路径,也为后续工艺优化奠定了坚实基础。

评论区

登录后即可参与讨论

立即登录