本文介绍了芯片设计中的标准单元。

在数字芯片设计领域,标准单元(Standard Cell)是构成复杂芯片功能的基础构件。它是指经过预先设计、优化与验证,具备特定逻辑功能且可重复使用的标准化电路模块。从基本逻辑门如与门、或门、非门,到触发器、加法器等运算单元,标准单元覆盖了数字电路的核心需求。其本质在于“标准化与可复用性”:一旦某个单元完成设计验证,便可在整个芯片设计中无限次复用,从而极大降低设计复杂度与出错率。

标准单元的物理特征与布局规范

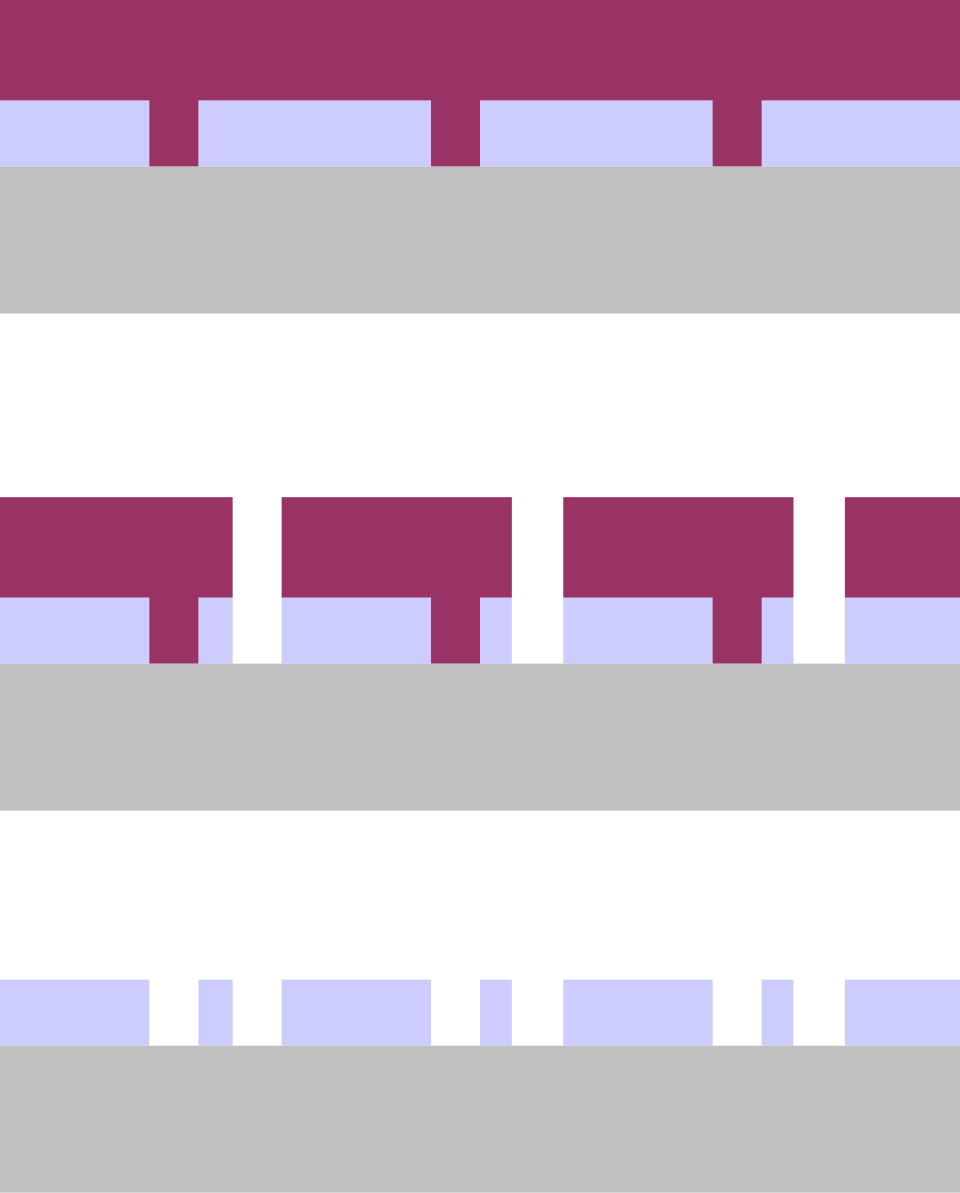

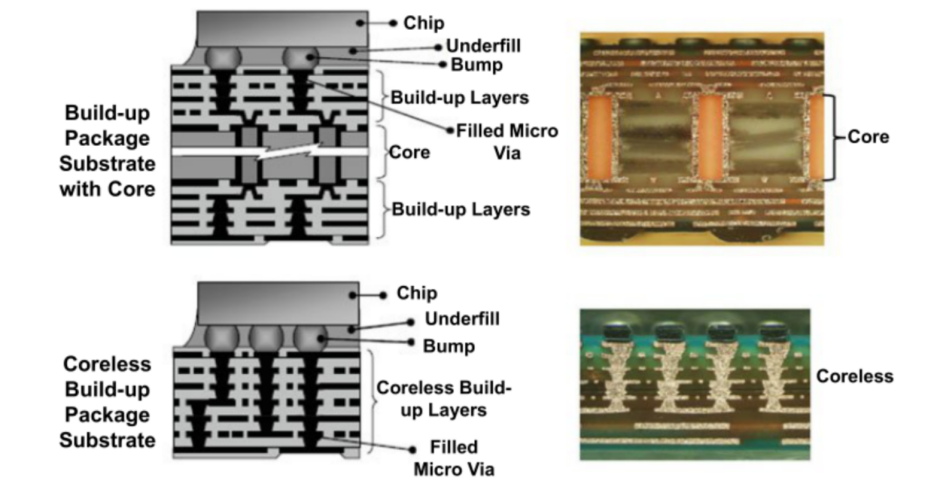

所有标准单元的高度保持一致,宽度则可根据功能复杂度灵活变化。单元的高度通常以其内部金属层轨道数来衡量,例如6T、9T、12T等,不同工艺节点的轨道高度从早期的7.5T逐步压缩至3T。宽度单位通常为CPP(接触多晶间距),即两个平行栅极之间的最小距离。这种“等高变宽”的设计使得标准单元能够整齐排列成单元行,简化了布局流程。

在电源与接口规范方面,所有标准单元的顶部统一布置VDD电源轨道,底部布置VSS地轨道,且均接入底层金属层。单元的输入输出引脚位置、金属层规范也完全统一,前端逻辑综合与后端布局布线均可直接调用这些接口信息,无需额外适配。

标准单元的设计流程与优化方法

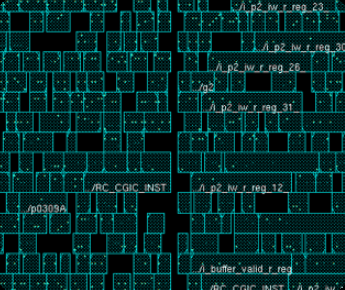

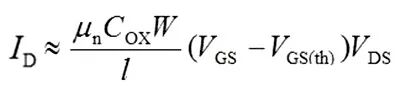

标准单元的设计流程涵盖从逻辑到物理的多个环节。逻辑电路设计阶段明确单元的功能需求,继而将其映射为晶体管级网表。在满足设计规则的前提下安排晶体管位置,PMOS位于单元上半部分的N-well区域,NMOS位于下半部分的P-well区域。完成晶体管布局后,进行单元内部的布线,随后开展版图优化,涵盖面积、延迟、功耗等指标,并通过设计规则检查以及版图与电路图一致性验证,最终生成LIB文件(时序与功耗参数库)和LEF文件(物理信息库)供芯片设计调用。

在先进工艺节点下,设计空间巨大且优化目标复杂。为提升性能,可采用多种优化技术:通过逻辑变换,同一逻辑功能可用不同布尔表达式实现,从而产生多种电路结构供选择;通过调整晶体管堆叠顺序优化欧拉路径,减少布线复杂度;利用网表分裂技术将大驱动单元拆分为多个小单元以降低延迟;还可将多个标准单元融合为一个复合单元,减少引脚数量并压缩面积。

不同规格标准单元的PPA权衡与应用

标准单元在设计阶段已完成功耗、性能、面积的多维度优化。不同规格的单元形成互补:小型单元(如6T单元)面积最小、功耗最低,适用于移动应用、超低功耗应用和嵌入式微控制器;中型单元(如9T单元)在面积与性能之间取得平衡,适用于通用计算和图形处理器;大型单元(如12T单元)驱动能力强、性能最优,用于高速计算和关键模块。工程师可根据芯片不同区域的需求选择合适规格的单元。

先进工艺下的挑战与协同优化

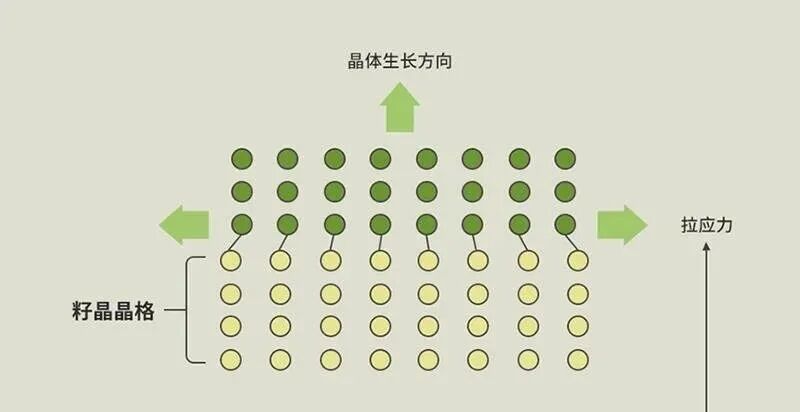

随着从平面晶体管到FinFET、再到环栅晶体管和互补场效应晶体管等新型器件结构的演进,设计规则愈加复杂,标准单元的轨道高度不断压缩,晶体管密度持续提升。标准单元的布局质量直接影响整个芯片的最终PPA表现,每一个晶体管的摆放、金属线的走向、过孔的位置都会影响性能与良率。

未来的标准单元设计已不再是单纯的版图绘制,而是跨逻辑层、拓扑层、物理层的系统级优化工程。结合设计-工艺协同优化与系统-技术协同优化理念,标准单元的设计范式有望随着新器件(如MESO、TFT)的引入而重新定义。

评论区

登录后即可参与讨论

立即登录