CoPoS玻璃基板突破CoWoS尺寸限制

随着摩尔定律失效和产业的“More than Moore”的技术路线发展,台积电的护城河早已不止晶体管的微缩节点之争,而是在封装技术上也不断推陈出新。

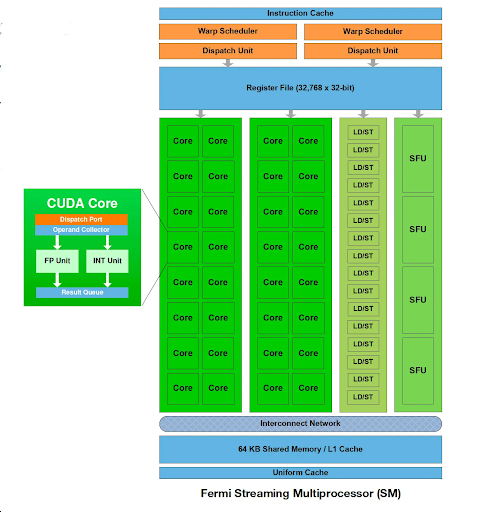

当前其核心的先进封装技术 CoWoS(Chip-on-Wafer-on-Substrate)。是一种将逻辑芯片(如 GPU、CPU)与高带宽内存(HBM)紧密集成在一起的 2.5D 封装技术,它通过在芯片和基板之间加入一层布线细密的“硅中介层”,让不同的芯片像并排摆放的模块一样实现超高速、低延迟的数据交换。这种技术突破了传统电路板传输速度的限制,能够显著提升芯片的整体性能并降低功耗。随着全球 AI 浪潮的爆发,CoWoS 已成为生产英伟达 H100、Blackwell 等高性能 AI 芯片不可或缺的关键工艺,因为它不仅解决了计算核心与内存之间的通讯瓶颈,还通过极高的集成度大幅缩小了设备体积,被视为目前半导体行业支撑大模型算力的技术基石和产能核心。

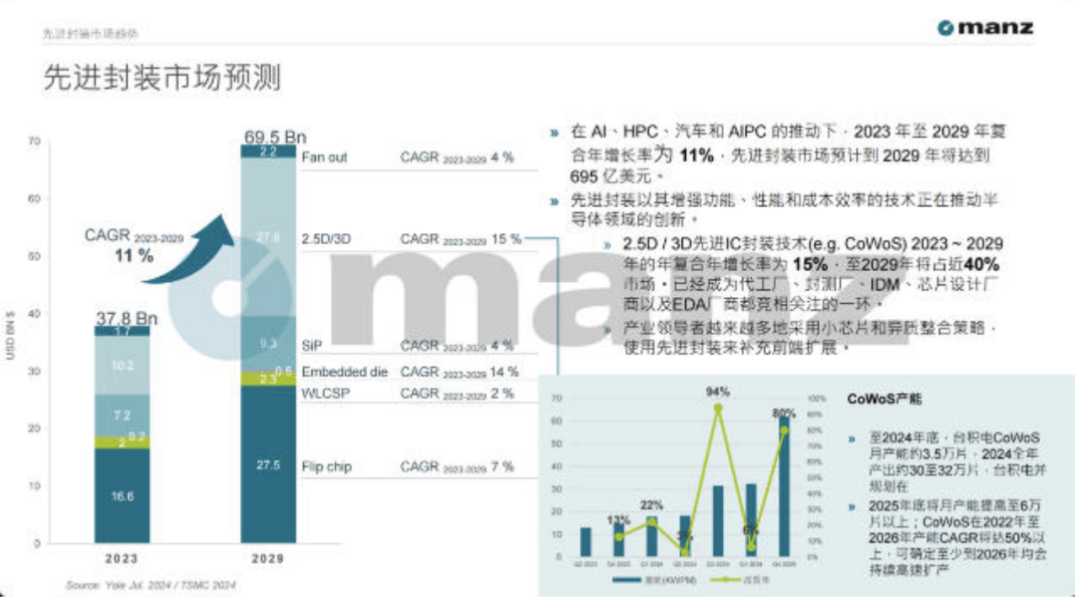

来自机构的先进封装市场的预测趋势显示(上图):在AI、HPC、汽车和AIPC等应用驱动下,全球先进封装市场将从2023年的37.8亿美元增长至2029年的695亿美元,2023–2029年复合年增长率(CAGR)达11%;其中,2.5D/3D封装(如CoWoS)增速最快(CAGR 15%),预计2029年占市场近40%,成为代工厂、封测厂、IDM、芯片设计厂及EDA厂商竞争焦点;Flip chip、SIP、Embedded die等技术亦保持稳定增长。CoWoS产能方面:台积电2024年月产能约3.5万片,2024全年约30–32万片;2025年底有望提升至6万片/月,2022–2026年CAGR超50%,并计划持续扩产至2026年。整体凸显先进封装作为“后摩尔时代”关键路径,正通过性能、功能与成本优化推动半导体产业链协同创新。

然而,CoWoS的尺寸也已经逼近极限,先进封装的老大TSMC正在考虑推动一场“从圆到方”的封装技术革命。

问题其实只是简单的几何学,我们最强大的 AI 芯片是矩形的。但当你试图从一个圆盘中切割出一堆矩形时,你总会在边缘留下大量无法使用的材料。试想一下,尝试从一张圆形的生面团中制作方形饼干。在这种情况下,所有这些剩下的边角料,也就是极其昂贵、超高纯度的硅,就这样被扔掉了。而所有这些浪费正是行业所谓的 CoWoS 瓶颈的核心所在。

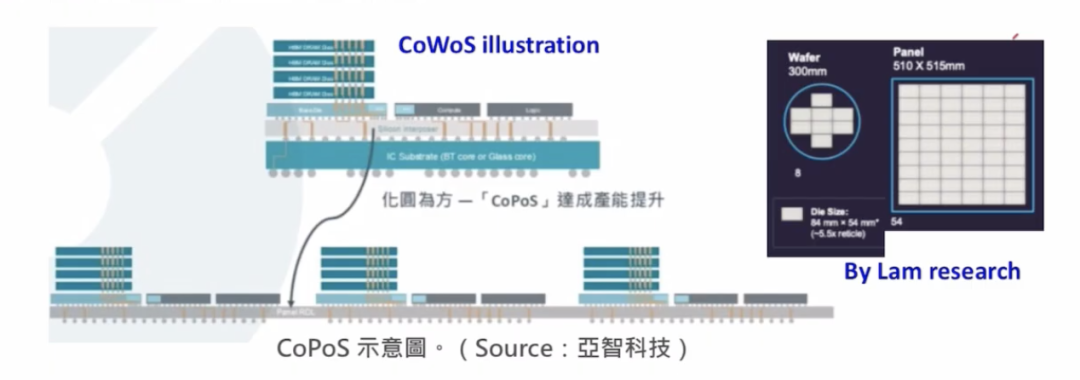

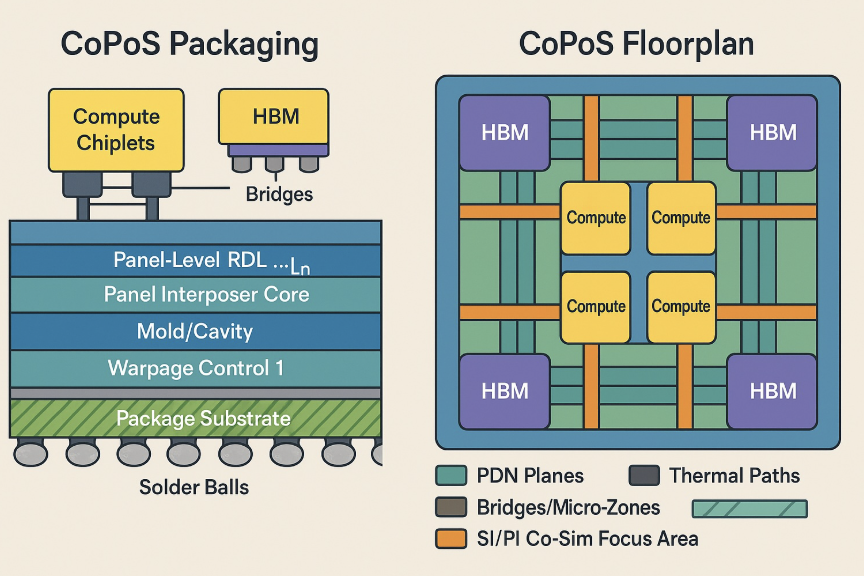

台积电(TSMC)正在研究的 CoPoS(Chip-on-Panel-on-Substrate) 是一种处于前沿开发阶段的先进封装技术,被视为目前主流 CoWoS 技术的延伸与进化方向。其核心创新在于将封装载体从传统的“圆形硅晶圆”更换为面积更大的“矩形面板”(通常基于玻璃或有机材料基板),通过这种 FOPLP(扇出型面板级封装) 模式,CoPoS 能够显著提升生产效率并降低单位成本。由于矩形面板在排布芯片时不会像圆形晶圆那样在边缘留下大量废料,且其物理尺寸上限远超传统晶圆,CoPoS 能够容纳更多数量的 GPU 计算核心与 HBM 内存组件,从而突破现有芯片尺寸限制(Reticle Limit),专门用于打造体积更庞大、算力更恐怖的下一代巨型 AI 加速器。

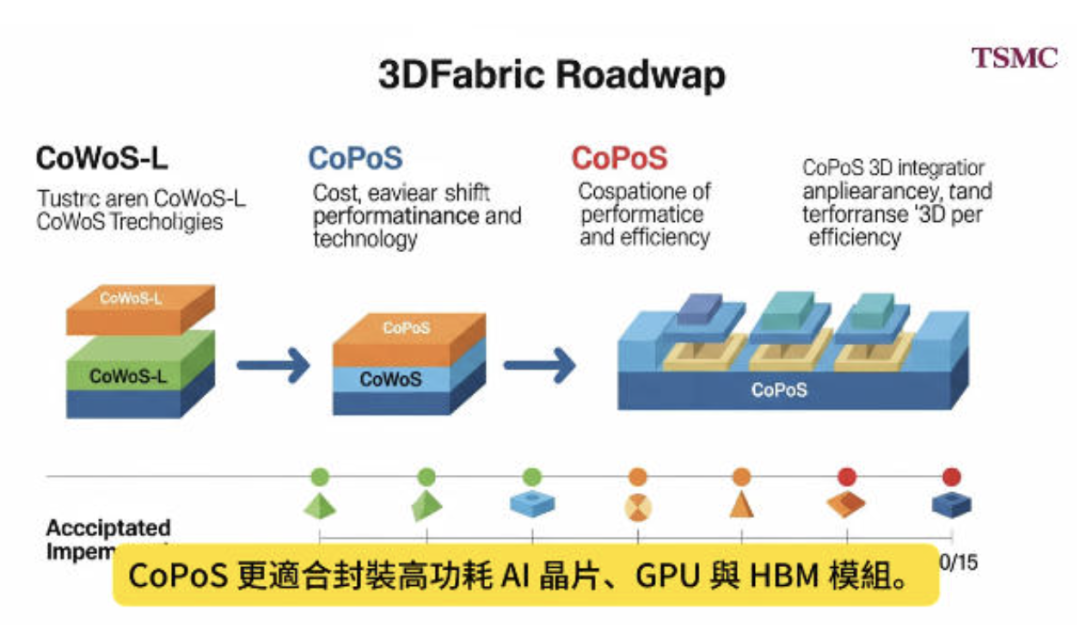

从 CoWoS 演进到 CoPoS,最核心的驱动力在于突破“尺寸极限”与“降低单位成本”。

首先是尺寸限制(Reticle Limit)的问题。现有的 CoWoS 技术基于 12 英寸(300mm)的圆形硅晶圆,这限制了单个封装体所能容纳的芯片数量和面积。随着 AI 算力需求的爆炸式增长,英伟达等厂商希望在一个封装内塞入更多的 GPU 核心和更多的 HBM 显存,但圆形晶圆的物理空间已接近极限。CoPoS 采用的矩形面板(如 515mm × 510mm 或更大)提供了比晶圆大数倍的可用面积,能够支持制造体积远超目前的“巨型芯片”,满足未来超级计算的需求。

其次是面积利用率与成本控制。在圆形晶圆上排布矩形的芯片时,边缘会留出大量无法利用的弧形废料,造成昂贵的材料浪费。而 CoPoS 采用的矩形面板能够实现近乎完美的“满格”排布,面积利用率从晶圆的约 70%-80% 提升至 90% 以上。这种规模效应配合面板级产线的大批量生产能力,能够显著摊薄单颗顶级 AI 芯片的封装成本。

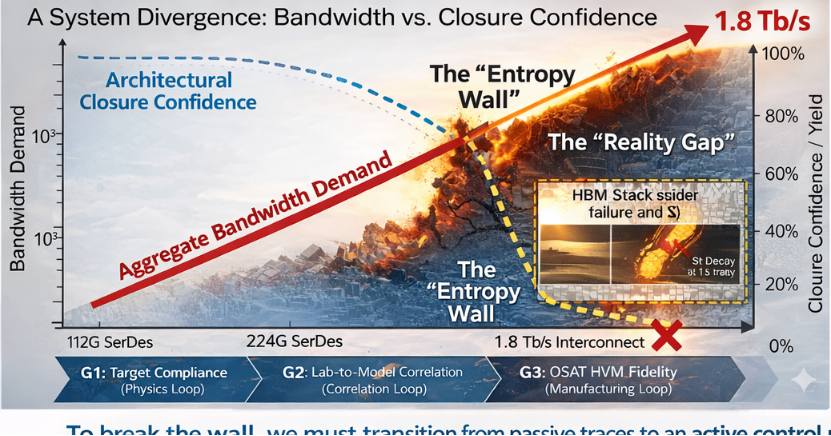

最后是性能与稳定性的考量。随着芯片功耗飙升,传统的硅中介层在极大尺寸下容易出现翘曲和散热挑战。CoPoS 往往伴随着玻璃基板等新材料的应用,这些材料具有更好的机械强度和电气性能,能提供更稳定的信号传输环境。因此,从 CoWoS 迈向 CoPoS,本质上是半导体封装从“精密加工”向“大规模、大尺寸集成”的一次战略性跨越,是为了制造出比现在更庞大、更强悍且更具经济效益的 AI 加速器。

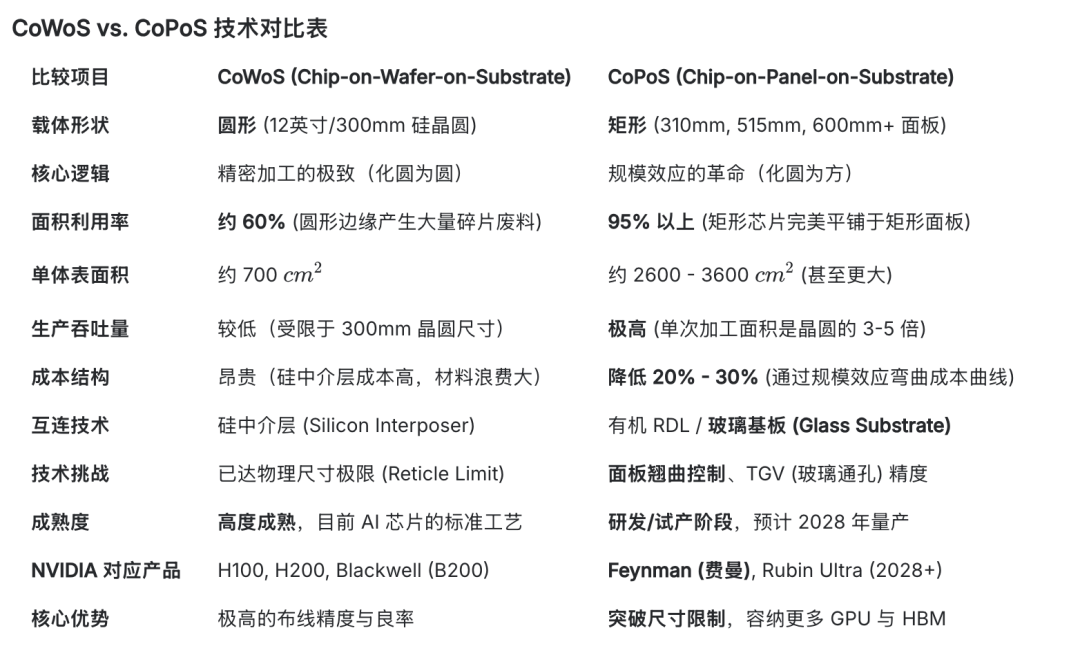

将 CoWoS 与 CoPoS 进行对比,本质上是在现有成熟精度的极致利用与未来大规模量产的扩张潜力之间做权衡。

CoWoS 的优势在于极其成熟的工艺与极高的互连精度。由于它基于成熟的 12 英寸硅晶圆制造技术,其布线密度可以达到亚微米级,能确保 GPU 与内存之间拥有最顶级的信号传输质量和良率。目前它是英伟达 H100 等高性能芯片的唯一标准。然而,CoWoS 的劣势在于“空间上限”和“材料浪费”:圆形晶圆限制了单个封装体的最大面积,且在排布矩形芯片时边缘会产生大量昂贵的报废区域,导致在生产更大规模的芯片组时成本高昂且物理空间受限。

相比之下,CoPoS 的核心优势是“巨型化”与“高利用率”。通过将载体从圆形晶圆变为面积大数倍的矩形面板,CoPoS 不仅能几乎百分之百地利用材料表面(矩形排布矩形),还能打破硅晶圆的尺寸限制,容纳更多的逻辑核心和 HBM 堆栈,是制造未来“超大算力怪兽”的必经之路。但 CoPoS 的劣势在于技术门槛和初期成本极高:在巨大的矩形面板上保持芯片对齐的精确度极其困难,且面板在加工过程中极易发生“翘曲”(弯曲变形),这对封装设备的精度、材料的刚性以及散热管理提出了近乎苛刻的要求。

综合比较来看,CoWoS 是“当下的王者”,代表了现阶段半导体封装能达到的最高精细度;而 CoPoS 则是“未来的天花板”,旨在通过牺牲一定的初期良率和设备投入,换取更强的扩展性和更低的长期单位成本。目前台积电正处于从 CoWoS 向 CoPoS 跨越的研发关键期,预计这种转变将成为 AI 芯片从“单体计算”迈向“整块面板计算”的分水岭。

关于台积电 CoPoS(Panel-level CoWoS / FOPLP) 的最新进展,目前正处于从“实验室研发”向“小规模试产”过渡的关键阶段。

虽然目前FOPLP已在小尺寸模拟芯片领域实现小幅量产,但台积电的CoPoS则将目标直指英伟达与AMD所属的高性能GPU市场。据未来半导体副主编齐道长报道,尽管现阶段大尺寸芯片的试产仍面临瓶颈,但行业内对于矩形载具的尺寸标准已展开激烈角逐。在台积电主导的310mm×310mm规格与力成、日月光、群创分别推动的515mm、600mm甚至700mm方案之间,600mm×600mm被不少专家看好为未来的主流,而台积电这种“化圆为方”的稳妥逻辑也在倒逼封测环节进行灵活的尺寸适配。

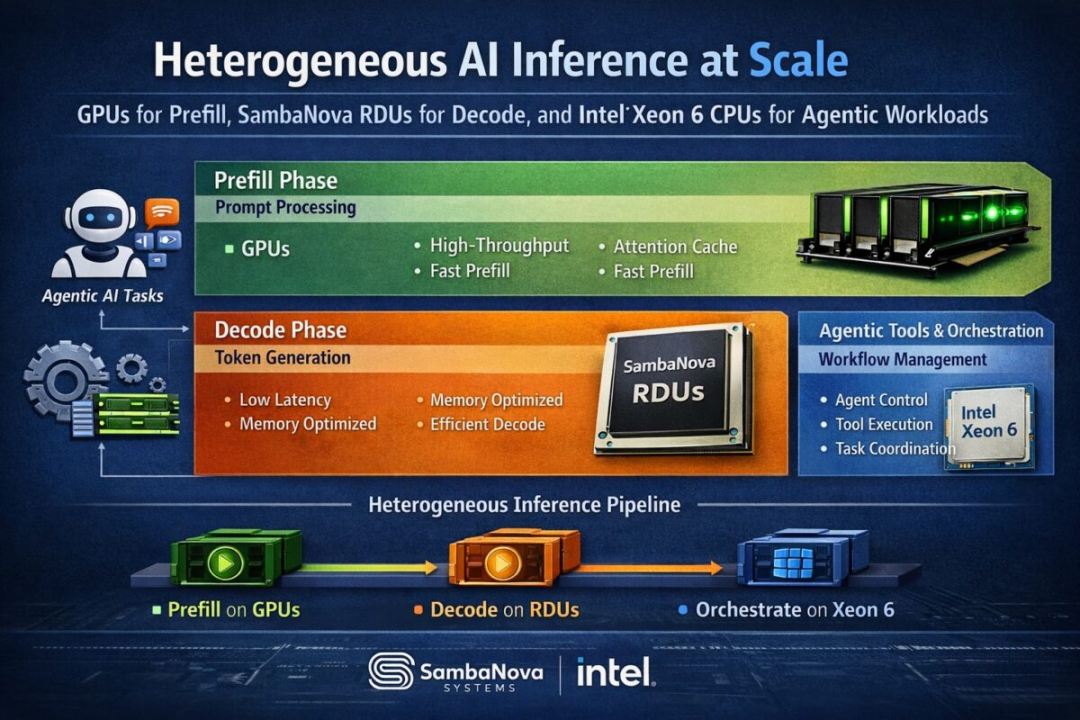

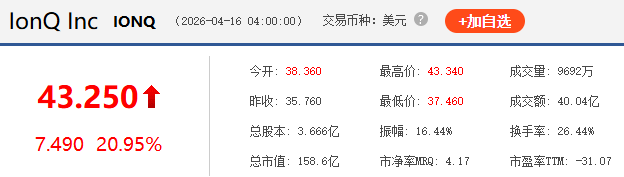

Nvidia 已经成功为其 2028 年代号为 Feynman 的 GPU 锁定了一个可以被称为“铁三角”的优势。它是三个关键优势的组合。首先,他们自己的先进芯片设计。其次,台积电全新的 A16 制造工艺。第三,这是真正的重磅炸弹:独家提前获得 CoPoS 封装的机会。这三位一体的结合可能是绝对无敌的。而且这里存在着令人难以置信的协同效应:那个全新的 A16 工艺有一个名为“背面供电”(backside power delivery)的秘密武器。这意味着他们将所有电源线移至芯片底部,从而释放了整个顶部表面,使其除了处理数据外别无他用。它为 CoPoS 连接巨大的芯片集群创造了一个完美的、整洁的画布,其密度和效率是我们从未见过的。

让我们用一些确凿的数据来说明:首先是规模。单个 600 毫米矩形面板的表面积是当今圆形晶圆的五倍以上。单凭这一点就是制造吞吐量上的一个里程碑式的飞跃。但它不仅更大,它还聪明得多。因为你是将矩形放在矩形上,那个可用面积从浪费的 60% 跳升到了令人难以置信的高效率——95% 甚至更高。所有那些浪费的硅片造成的支出被有效地制止了。

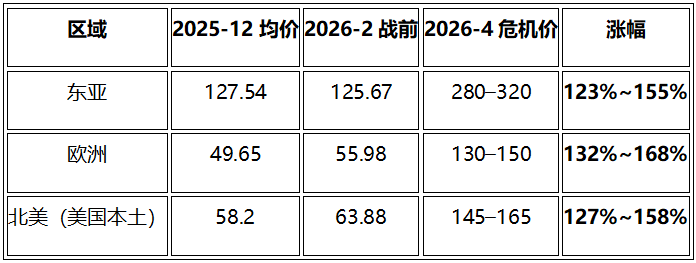

行业估计,CoPoS 可以将制造一个成品 AI 模块的总成本降低 20% 到 30%。这并不是一个小进步。它从根本上弯曲了 AI 的整个成本曲线,使得构建和部署全球最强大系统的成本变得更低。所以,如果 Nvidia 独家拥有这项改变游戏规则的成本削减技术,其他人会发生什么?这就是我们所说的“竞争对手的挤压”。

对于像 AMD 和 Google 这样的竞争对手,他们只能继续应对老旧的 CoWoS 瓶颈,这迫使他们在 Samsung 或 Intel 等其他供应商身上进行赌注,而这些供应商的替代技术要么不够成熟,要么在良率方面有过历史遗留问题。这是一场高风险的赌局,可能在比赛真正开始之前就让他们落后整整一代。

这张表格展示了一切。你看到 Nvidia 正在台积电安全地从成熟的 CoWoS-L 转向革命性的 CoPoS。与此同时,传闻 Google 正在探索 Intel 的 EMIB,而 AMD 正在关注一家名为力成(Power Tech)的公司。现在,这些都是可行的技术,但它们代表了巨大的战略赌博,是一次背离行业最稳定、最先进制造商的行动。

总结一下。先进封装这里的意义远远、远远超出了芯片制造本身。

这不仅仅关乎制造更便宜、更强大的芯片。当你锁定了基础制造工艺中为期数年的领先地位,这就是一家公司巩固其霸权的方式。这就是你如何获得对未来十年整个 AI 行业的经济,坦率地说,还有地缘政治杠杆的控制权。所以,这一切都回到了我们开始时的那个简单形状。AI 的未来将不仅仅由代码书写。它将由几何学决定。下一个十年的赢家将是率先逃离圆形统治的人。剩下唯一的问题是,谁会被留在身后。

评论区

登录后即可参与讨论

立即登录