本文将介绍CMOS功耗优化领域。

CMOS设计

低功耗CMOS集成电路设计作为半导体领域的核心研究方向,其发展脉络与行业需求紧密交织,自20世纪70年代CMOS技术初步应用以来,历经半个世纪的演进,已从早期的特定场景应用拓展为全行业普适性设计理念。

20世纪80年代中期,随着VLSI技术对高集成度与低功耗的双重需求凸显,CMOS凭借其静态功耗低、工艺兼容性强的优势,逐步取代nMOS成为主流工艺,这一转变不仅源于电池供电设备如腕表、计算器、医疗植入设备的普及需求,更根植于晶体管数量激增与性能提升带来的功耗挑战——从数千晶体管到百亿级规模,主频从兆赫兹跨越至千兆赫兹,芯片功耗从不足1W攀升至百瓦量级,ASIC类产品功耗亦突破瓦级限制,迫使设计者必须将低功耗策略贯穿于架构、电路、工艺协同优化的全流程中。

进入21世纪,便携式设备爆发式增长与高性能计算需求激增,进一步强化了低功耗设计的战略地位。消费电子领域,游戏终端、MP3播放器、数码相机、GPS模块、平板电视等产品对续航能力的极致追求,推动电池技术与电源管理芯片同步革新;PC市场中,笔记本电脑占比持续扩大,其散热限制与移动场景特性倒逼处理器、内存控制器等核心模块采用动态电压频率调节、近阈值计算等低功耗技术;通信领域,5G/6G基站与终端设备通过语音视频压缩算法优化、低功耗射频前端设计,实现信号处理与传输的高能效比。

与此同时,新兴多媒体应用如便携式全动态视频设备、AR/VR头显、智能穿戴设备等,对显示驱动、图像处理、无线连接模块的低功耗设计提出更高要求,而PDA等早期手持设备的技术积累,则为后续产品开发奠定了硬件与算法基础。面向未来系统需求,低功耗设计已成为突破物理极限的关键路径。

电池技术概述

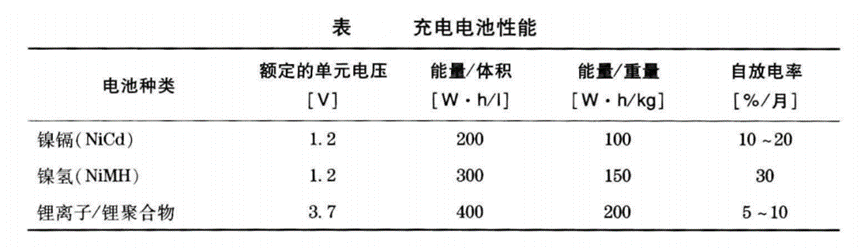

电池技术作为便携式电子设备与系统能效提升的核心支撑,其发展始终围绕能量密度、循环寿命、安全性能及成本效益四大维度展开。传统电池体系以非充电原电池与可充电蓄电池为两大分支——原电池凭借不可逆化学反应实现高能量存储效率,适用于低功耗、长寿命场景如电子钟表,但频繁更换的成本限制其在高性能系统中的应用;而充电电池通过可逆电化学反应实现能量循环利用,在需频繁充放电的移动设备中更具经济性,但需应对记忆效应、自放电率及安全风险等挑战。

进入21世纪,电池技术革新聚焦于材料科学与工艺突破。镍镉电池虽曾主导市场,但其低电压、低能量效率及记忆效应缺陷促使镍氢电池快速崛起,后者通过提高能量容量实现部分替代,但仍需定期深度放电以缓解电压弱化问题。锂离子与锂聚合物电池则凭借高单体电压、高能量密度及低自放电率成为主流选择——锂离子电池采用有机电解液,锂聚合物电池则以固态聚合物电解质替代,二者均实现每升400Wh以上的能量密度,且自放电率控制在每月5%以内,记忆效应几乎可忽略。然而,锂基电池对过充、过放及短路高度敏感,需内置保护电路监测电压与温度,防止热失控导致的起火或爆炸风险,这限制了其在高温环境中的应用场景。

近年来,电池技术突破呈现多元化趋势。固态电池通过替换液态电解液为固态电解质,从根本上解决了漏液、易燃问题,同时支持更高能量密度材料如锂金属负极的应用,理论能量密度可达500Wh/kg以上,已进入小规模量产阶段。钠离子电池则凭借钠资源丰富、成本低廉的优势,在储能电站、低速电动车等领域展现潜力,其循环寿命与低温性能持续优化。锂硫电池通过硫正极的高比容量特性,理论能量密度可达600Wh/kg,但需解决多硫化物穿梭效应导致的循环衰减问题。此外,电池管理系统(BMS)的智能化升级,结合AI算法实现精准SOC估算、动态充放电控制及热管理优化,进一步提升了电池系统的安全性与能效。

低功耗的工艺选择

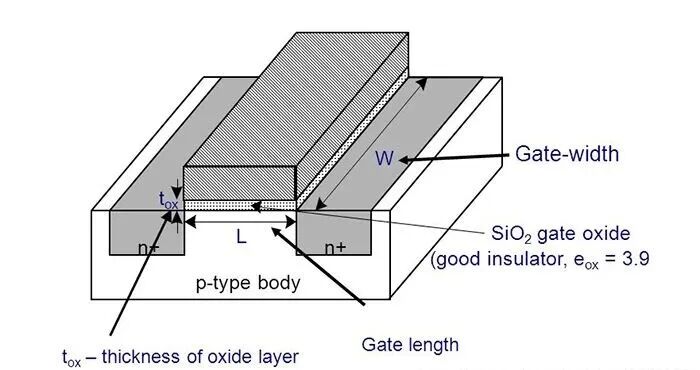

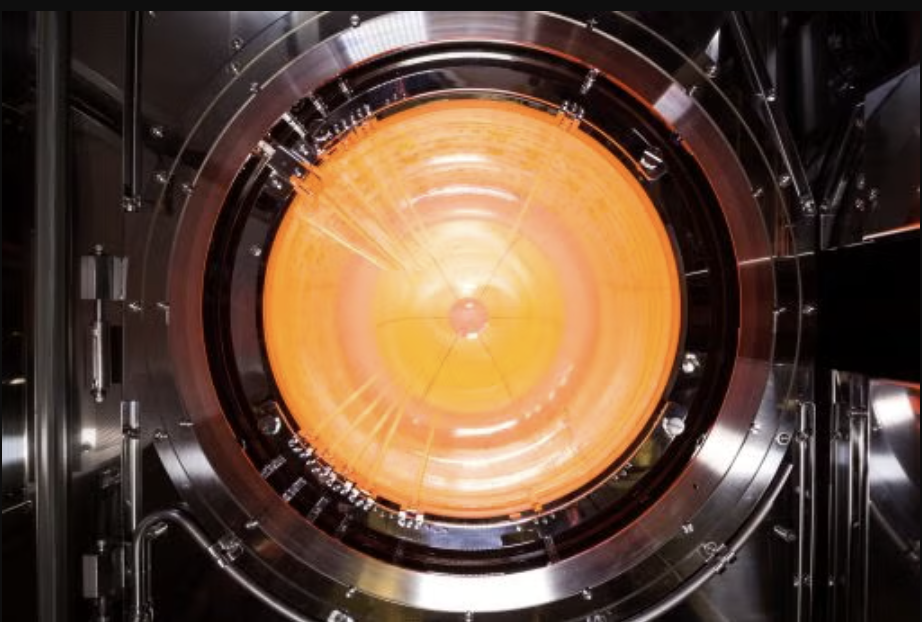

在CMOS功耗优化领域,工艺选择对泄漏功耗的控制尤为关键,其技术演进始终围绕阈值电压调控、器件结构创新及工艺参数优化展开。

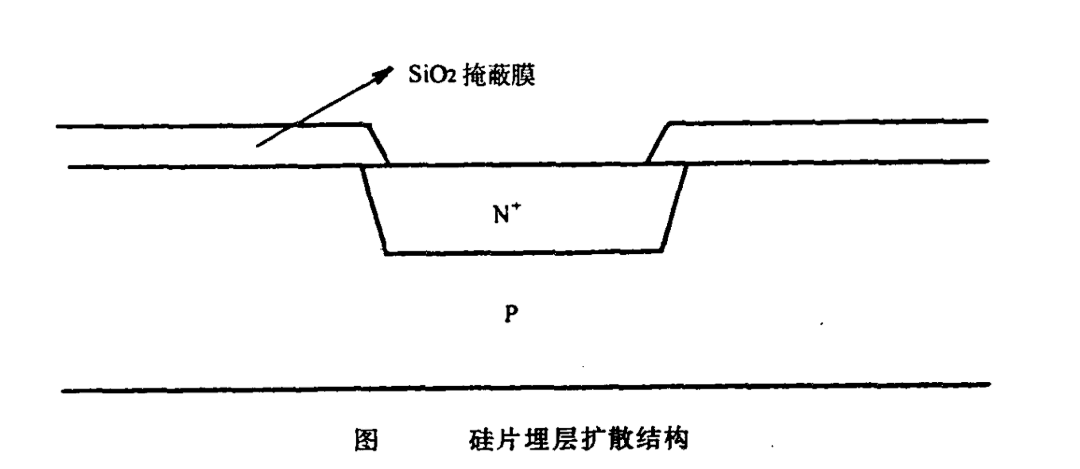

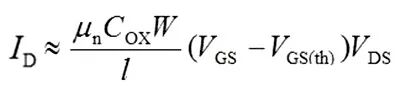

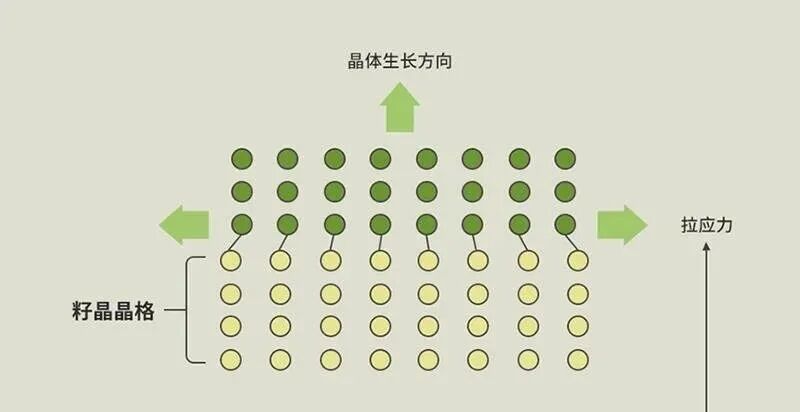

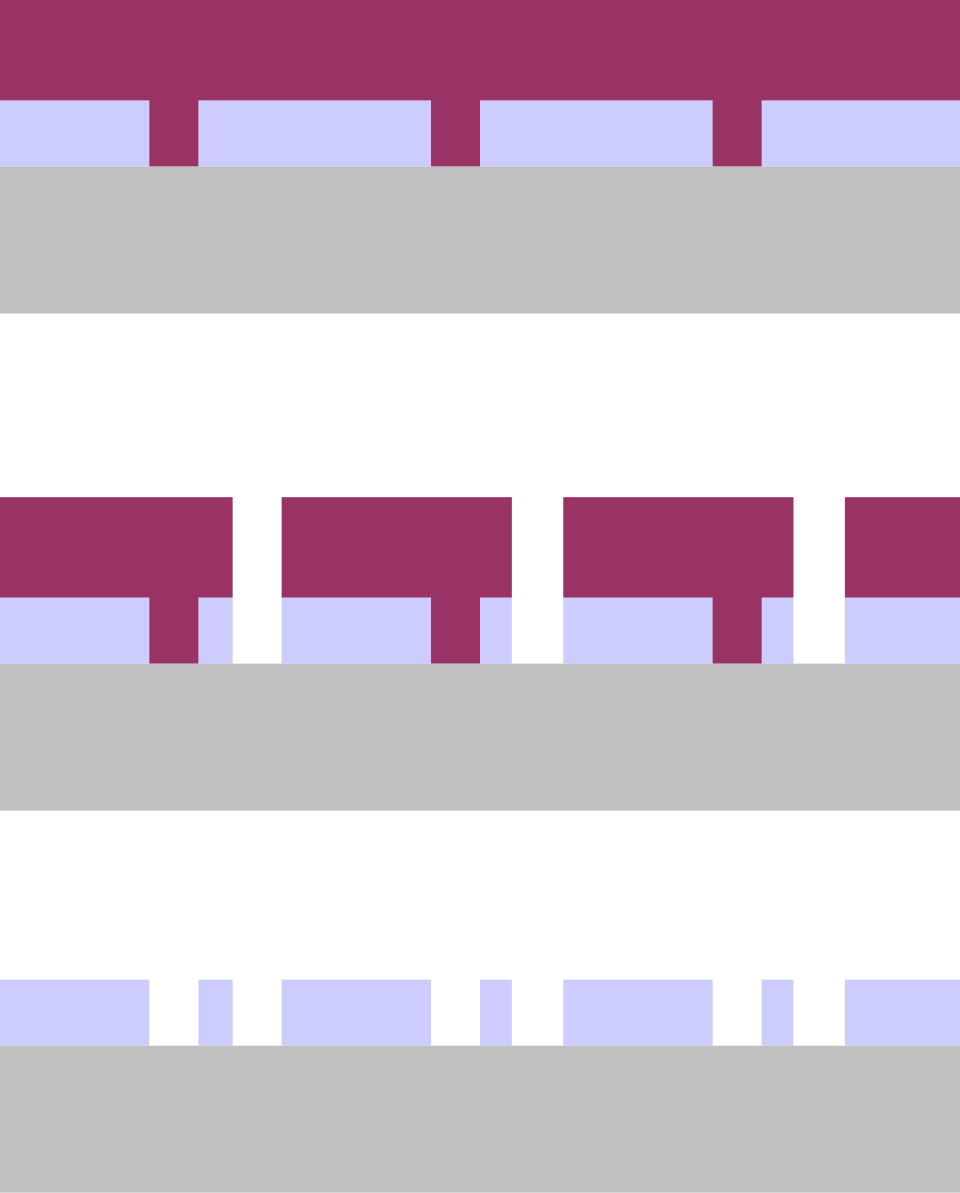

随着工艺节点向65nm及以下推进,短沟道效应引发的阈值电压滚降现象加剧,导致亚阈值泄漏电流呈指数级增长——根据亚阈值斜率特性,阈值电压每降低100mV将引发泄漏电流约18倍的增加,这对待机模式下的功耗控制构成严峻挑战。为抑制此类泄漏,行业普遍采用三阱工艺实现p阱与衬底的物理隔离,通过动态调整背偏置电压改变阈值电压,例如对nMOS施加负p阱偏置或对pMOS施加正n阱偏置,可使阈值电压提升约100mV,有效降低待机电流。然而,该技术在小尺寸工艺中面临局限性:局部halo掺杂虽能缓解短沟道效应,但会加剧结泄漏电流;当栅氧厚度降至2nm以下时,栅极隧穿漏电可能超越亚阈值泄漏,成为主导因素。

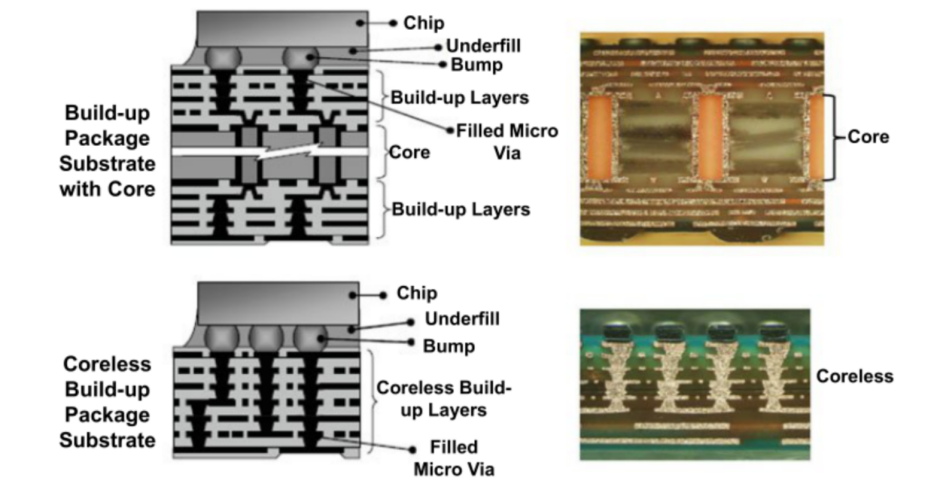

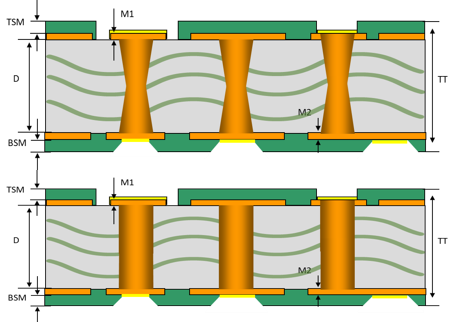

多阈值CMOS(MTCMOS)技术通过组合高VT与低VT晶体管实现功耗与性能的平衡——智能综合工具可自动将非关键路径替换为高VT单元(约占逻辑总量的10%),使泄漏功耗降低近一个数量级,同时保留关键路径的低VT单元保障性能。此外,采用长沟道晶体管(沟道长度大于最小工艺尺寸)可同步提升阈值电压,抑制亚阈值泄漏与导通电流,该策略需结合单元库支持以实现有效部署。在栅氧泄漏控制方面,高k介质与金属栅极技术的引入显著缓解了栅极隧穿问题,而双栅氧厚度工艺则为不同功能模块提供定制化选择,例如高k介质用于高性能单元,传统氧化层用于低泄漏单元。

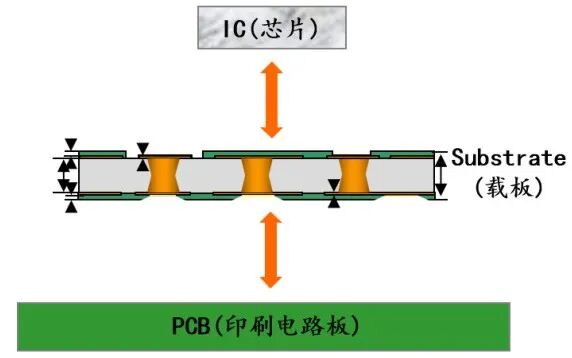

当前,自适应体偏置(ABB)与自适应电压调整(AVS)技术通过实时监测工艺扰动并动态调节体偏置电压,进一步优化泄漏功耗与性能的权衡。在三维集成领域,Chiplet异构集成与三维堆叠技术通过优化互连结构减少寄生电容,结合电源分配网络设计降低动态功耗;而FinFET与GAA FET等新型器件结构通过增强栅极控制能力,在抑制亚阈值漏电的同时支持更低的电源电压。这些工艺创新与系统级协同优化策略,共同推动CMOS功耗管理向跨层级、智能化方向演进,为高性能计算、物联网及可穿戴设备提供更高效的能效解决方案。

评论区

登录后即可参与讨论

立即登录