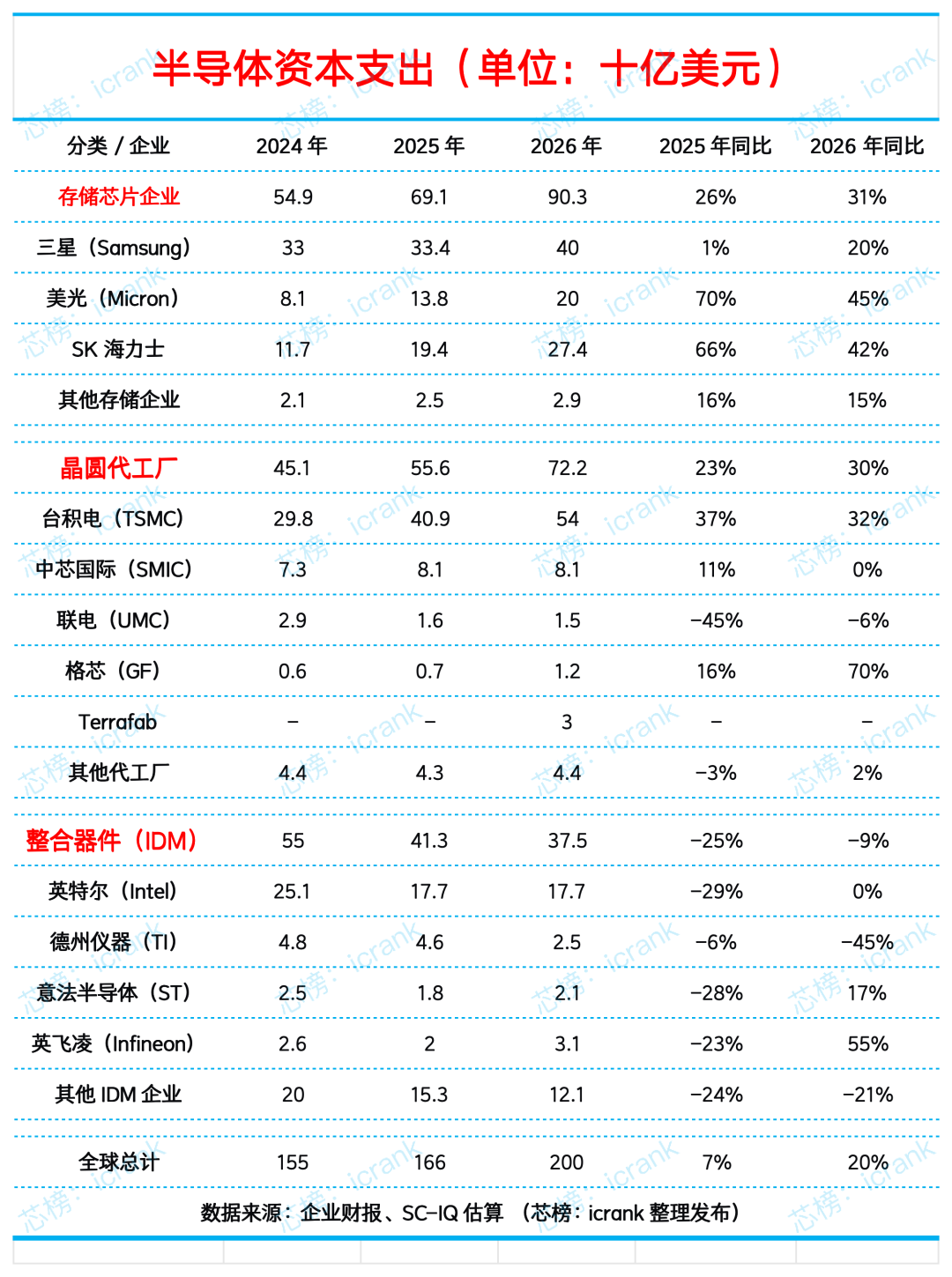

台积电在其2026年北美技术研讨会上公布了截至2029年的通用制造技术路线图,先进制程仍在继续推进。

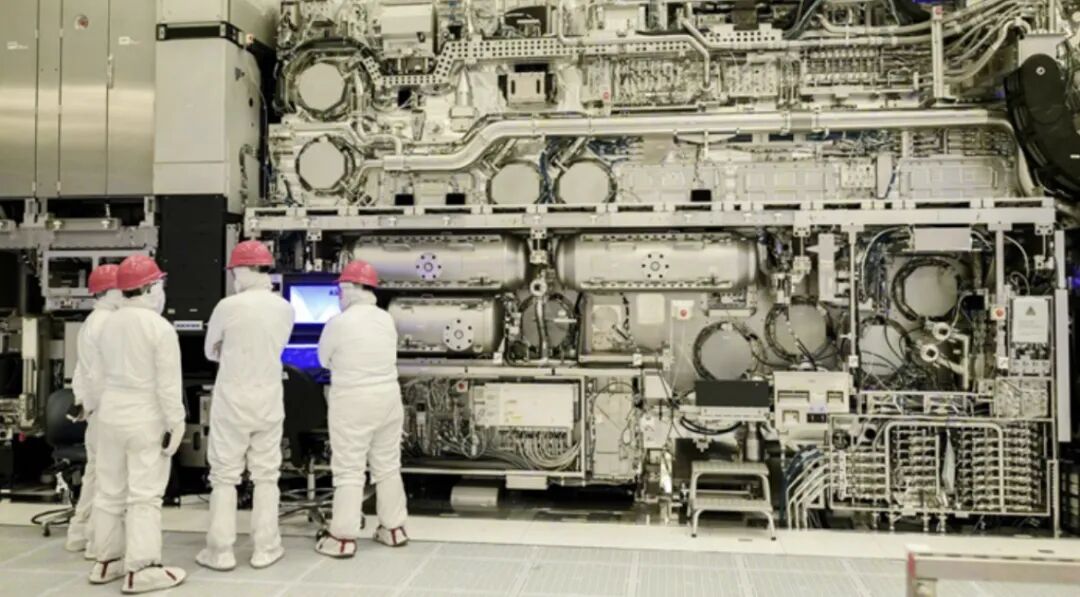

值得注意的是,台积电并没有急着把High-NA EUV(高数值孔径极紫外光)光刻技术放进2029年前的量产节点。作为对比,英特尔则更早导入High-NA设备。两家公司真正的差异,不只是设备选择,而是量产节奏、成本和良率风险的取舍。

近年来,台积电AI和HPC(高性能计算)已反超手机业务,在其路线图中也体现了出来 —— 台积电将先进制程按终端市场需求进行“分轨”规划,而非“一刀切”。具体来说:A16和A12等面向AI/HPC的节点,提供显著性能提升以支撑技术迁移,成本相对不那么敏感,但更新节奏为两年一次;N2、N2P、N2U、A14、A13等制程主要面向智能手机和客户端设备,这些市场更看重成本、能效和IP复用,对设计兼容性要求高,能保持每年一个新节点的节奏。

-

A16被列为2027年节点(相较此前2026年略有延后),基于第一代GAA纳米片晶体管,引入SPR背面供电,专为高性能数据中心应用打造;而A16将由A12接棒,预计2029年推出。

-

A14制程,基于第二代GAA纳米片晶体管,并通过NanoFlex Pro技术提供更高设计灵活性,预计将于2028年用于高端智能手机和客户端芯片;A13则是以最小扰动换取额外效率提升,在保持完整设计规则和电气兼容性的同时,相对A14实现约6%的面积缩减;

-

同时,台积电通过N2U持续扩展2nm平台,预计于2028年开始生产。N2U利用N2技术平台的制程成熟度与高良率表现,能够用较低迁移成本覆盖AI/HPC和移动应用。

台积电为何现在深挖现有EUV潜力

针对展示的最新技术,台积电计划在现有Low-NA EUV体系下继续通过工艺优化推进节点,而非转向新一代High-NA EUV设备。台积电全球业务资深副总经理暨副共同营运长张晓强表示,“只有当High-NA EUV能带来切实、可量化的技术增益时,我们才会引入。现阶段依托现有EUV设备,A14及后续制程依旧能实现大幅性能升级。研发团队正持续挖掘现有EUV设备潜力,依靠工艺优化延续摩尔定律微缩优势。”

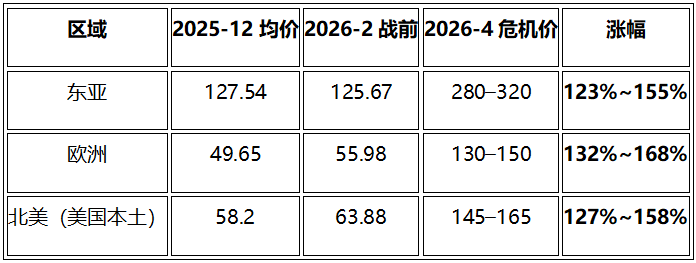

当前全球AI算力需求爆发,各大厂商加速新建晶圆厂扩产,而High-NA EUV的引入也是一笔高额资本开支:市场报道显示,Low-NA EUV Twinscan NXE:3800E每台成本约为2.35亿美元,High-NA EUV Twinscan EXE:5200B预计每台成本为3.8亿美元。

台积电目前公开路线图显示,2029年前规划节点仍不会依赖High-NA EUV。选择继续复用现有EUV光刻机,完成A12、A13等新一代优化制程的研发与量产落地。这与英特尔的路线形成鲜明对比。需要注意的是,High-NA EUV设备不是未来左右输赢的唯一关键,工艺整合和先进封装同样关键。例如,去年台积电就成功地透过调整光阻材料、光罩制程等方式,在提升先进制程的临界尺寸与图形精度的同时,还降低了缺陷密度。

英特尔更早进入High-NA EUV调试阶段

早在2023年底,ASML就向英特尔交货了首套High-NA EUV光刻机,型号为TWINSCAN EXE:5000。英特尔将其作为试验机,并于2024年初在美国俄勒冈州的Fab D1X晶圆厂完成安装。之后,该晶圆厂成为英特尔半导体技术研发基地,进一步研发基于High-NA EUV光刻技术的尖端制程。

High-NA EUV光刻机与标准EUV光刻机差异不小,提升使用经验需要大量时间修正基础设施。更早安装设备意味着英特尔可以更早进入设备调试、工艺整合和量测验证阶段,但High-NA的先发投入能否转化为商业回报,还取决于设备利用率、良率爬坡和外部客户导入。

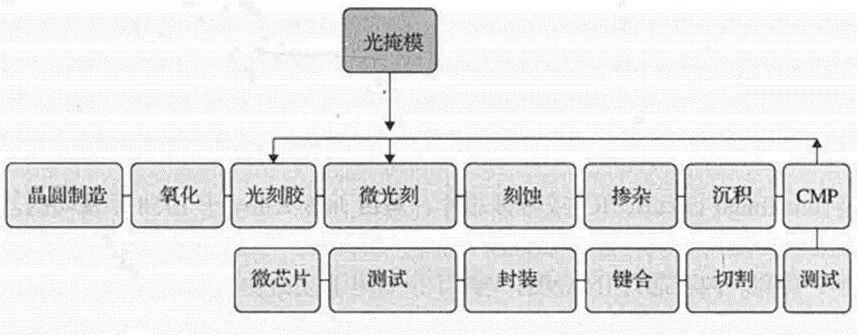

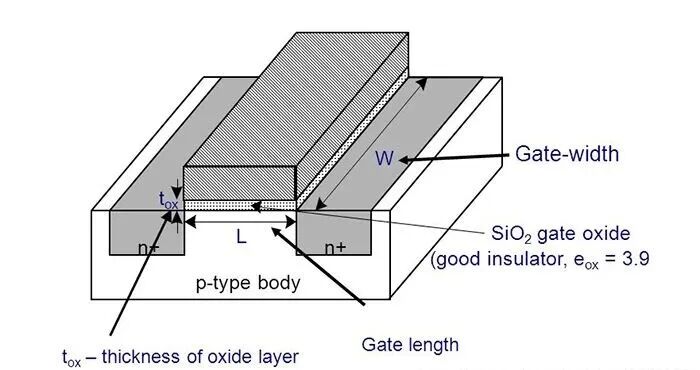

光刻设备中的NA代表数值孔径,表示光学系统收集和聚光的能力。High-NA EUV把NA从0.33提高到0.55,更强的聚光能力意味着能够处理更加精细的几何尺寸,同时这也是继续推进半导体制程进化的路线之一。

ASML称其High-NA EUV系统在单次曝光中实现了8nm分辨率,与当前Low-NA EUV工具的13.5nm分辨率相比有所提升。尽管Low-NA EUV系统也可以使用双图案化(双重曝光)达到8nm分辨率,但这种方法会增加工艺复杂度并影响良率。因此,英特尔抢先导入High-NA,被视为其推进14A和代工业务的重要技术押注。

英特尔首席财务官David Zinsner在花旗2025年全球TMT大会上表示,下一代Intel 14A制程技术将使用ASML最新的第二代High-NA EUV光刻机TWINSCAN EXE:5200B。根据英特尔此前披露的数据显示,Intel 14A相比Intel 18A将带来15-20%的每瓦特性能提升,密度提升30%,功耗降低25-35%。****

如果14A能够按计划推进,并获得外部客户导入,英特尔可能借High-NA经验争取AI/HPC客户。必须指出的是,目前一切都还处于测试芯片和评估阶段,还没有完全确定采用14A芯片的外部客户。潜在客户/代工客户的决策窗口将在2026年下半年开启,并延续至2027年初。****

**虽有部分分析机构质疑,台积电暂缓High-NA EUV在量产节点引入,可能会让台积电在未来的竞争中处于劣势。但考虑到High-NA EUV设备成本高昂,在现有EUV设备尚有最佳化空间的情况下,台积电选择审慎评估投资时机,这更像是一种在技术收益、设备成本和量产风险之间的节奏选择。**

先进制程最终要回到良率和客户导入

三星与台积电的竞争在7nm后拉开了差距,由于在晶体管密度这一关键指标上,三星的表现始终未能超过台积电。尽管两者的市场份额已经存在显著差距,但三星并未因此放弃超越台积电的目标,反而加速晶圆代工技术的发展。

在3nm制程上三星率先采用GAA架构,也是唯一在3nm制程中采用GAA架构的,想要以技术代差压制台积电的FinFET路线,但量产表现和客户导入并没有帮助它实现对台积电的反超。

新晶体管结构的引入,会同时带来设备适配、工艺整合、设计规则和良率爬坡问题,不止首发那么简单。三星技术负责人曾坦言:“我们误判了GAA工艺的产业化难度,设备适配和工艺整合复杂度远超预期。”

三星3nm GAA的案例说明,先进结构只有和量产良率、客户导入、成本控制同时跑通,才能转化为竞争力。台积电在3nm继续沿用FinFET架构,但依靠更成熟的工艺整合和客户生态保持了量产节奏。

先进制程竞争不是谁先换设备谁就赢。High-NA EUV会成为重要工具,但设备、光刻胶、光罩、设计规则、良率、先进封装、客户导入和产能节奏必须一起成立,技术领先才会变成量产领先。

评论区

登录后即可参与讨论

立即登录